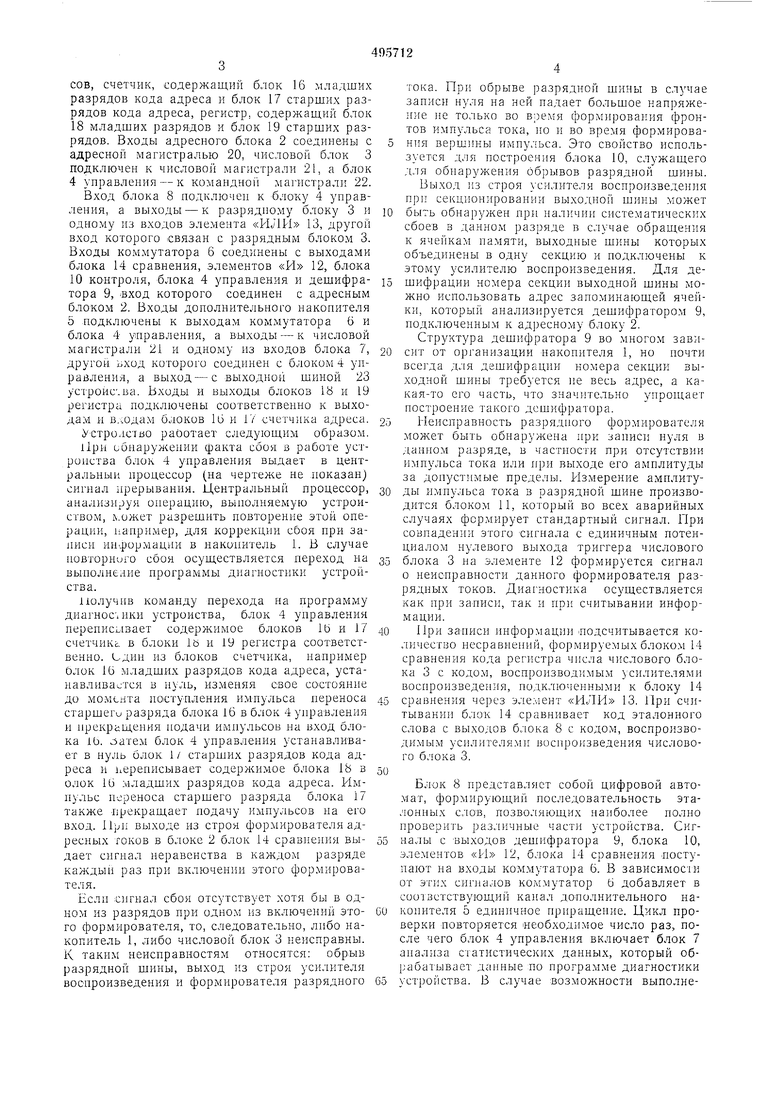

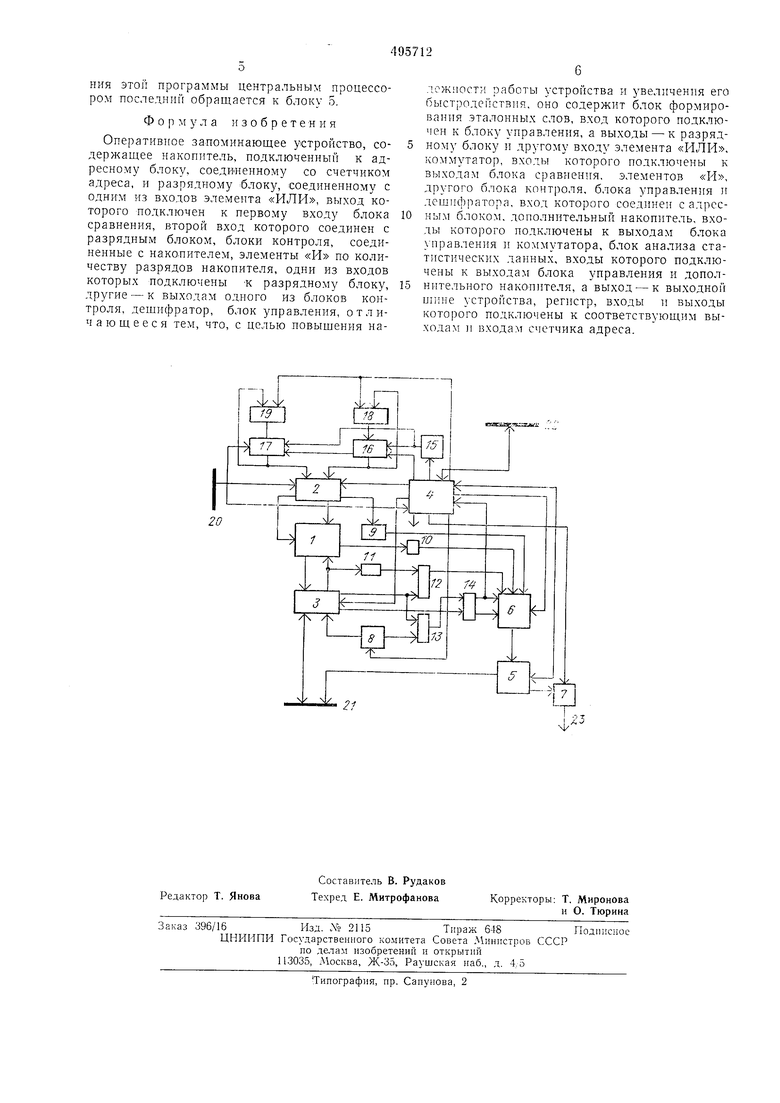

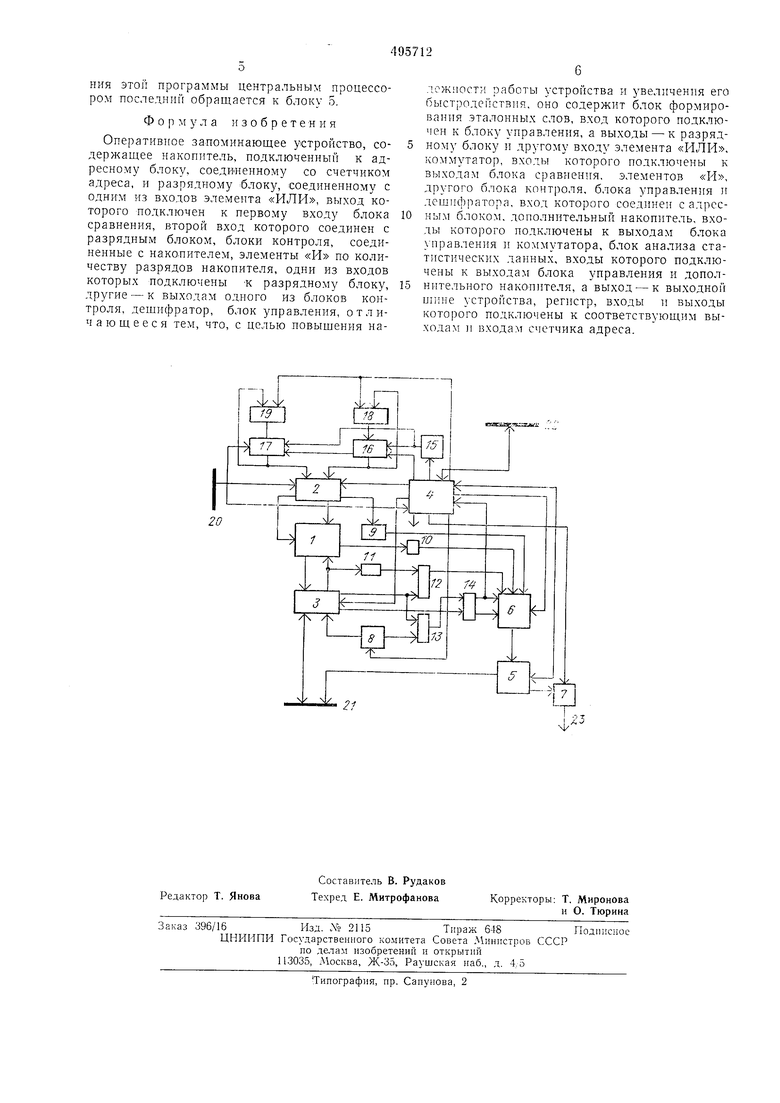

сов, счетчик, содержащий блок 16 младших разрядов кода адреса и блок 17 старших разрядов кода адреса, регистр, содержаш ий блок 18 младших разрядов и блок 19 старших разрядов. Входы адресного блока 2 соединены с адресной магистралью 20, числовой блок 3 подключен к числовой магистрали 21, а блок

4управления - к командной магистрали 22. Вход блока 8 подключен к блоку 4 управления, а выходы - к разрядному блоку 3 и одному из входов элемента «ИЛИ 13, другой вход которого связан с разрядным блоком 3. Входы ком.мутатора 6 соединены с выходами блока 14 сравнения, элементов «И 12, блока

10 контроля, блока 4 управления и дешифратора 9, ВХОД которого соединен с адресным блоком 2. Входы дополнительного накопителя

5подключены к выходам коммутатора 6 и блока 4 управления, а выходы - к числовой магистрали 21 и одному из входов блока 7, другой ьход которого соединен с блоком 4 управления, а ВВ1ХОД-с выходной шиной 23 устройства. Входы и выходы блоков 18 и 19 регистра подключены соответственно к выходам и В-..одам блоков 16 и Г/ счетчика адреса.

Устролство раоотает следуюндим образом.

ilpn обнаружении факта сбоя в работе устройства блок 4 управления выдает в центральный процессор (па чертеже пе показан) сигнал ирерыванпя. Централвньп процессор, анализируя операцию, выполняемую устройством, кожет разрешпть повторение этой операции, например, для коррекции сбоя при записи информации в накопитель 1. В случае новторниго сбоя осуществляется переход па выполнение программы диагностики устройства.

получив комапду перехода па программу диагнос,ики устройства, блок 4 уиравления переписывает содержимое блоков 16 и 17 счетчикс в блоки 1ь и 19 регистра соответственно, идин из блоков счетчика, иапример Олок 16 младших разрядов кода адреса, устанавливается в нуль, изменяя свое состояние до момента поступления импульса переноса старшеги разряда блока 16 в блок 4 управления и прекращения нодачи импульсов па вход блока 16. 5атем блок 4 управлепия устанавливает в нуль блок 1/ старших разрядов кода адреса и переписывает содержимое блока 18 в ОЛОК 16 младших разрядов кода адреса. Импульс перепоса старшего разряда блока 17 также т рекращает подачу импульсов па его вход. При выходе из строя формирователя адресных ГОКОВ в блоке 2 блок 14 сравнепия выдает сигнал неравенства в каждом разряде каждьп раз при включении этого формирователя.

Если сигнал сбоя отсутствует хотя бы в одном из разрядов при одном из включений этого формирователя, то, следовательно, либо накопитель 1, либо числовой блок 3 неисправны. К таким неисправностям относятся: обрыв разрядной шины, выход из строя усилителя воспроизведения и формирователя разрядного

тока. При обрыве разрядной шины в случае записи нуля на ней надает большое напряжение не только во время формирования фронтов импульса тока, но и во время формирования вершины имнульса. Это свойство используется для построения блока 10, служашего для обнаружения Обрывов разрядной шипы.

Выход из строя усилителя воспроизведения при секциопироваиии выходной шины может быть обнаружен при наличии систематических сбоев в данном разряде в случае обращения к ячейкам намяти, выходиые шины которых объединены в одну секцию и подключены к этому усилителю воспроизведения. Для дешифрации номера секции выходной шины можно использовать адрес запоминающей ячейки, который анализируется дешифратором 9, подключенным к адресному блоку 2.

Структура дешифратора 9 во многом зависит от организации накопителя 1, но почти всегда для дешифрации номера секции выходной шины требуется пе весь адрес, а какая-то его часть, что значительно упрощает построение такого дешифратора.

Неисправность разрядного формирователя .может быть обиаружеиа при заииси нуля в даппом разряде, в частности при отсутствии импульса тока или при выходе его амплитуды за допустимые пределы. Измерение амплитуды импульса тока в разрядной шиие производится блоком И, который во всех аварийных случаях формирует стандартный сигнал. При совпадении этого сигнала с единичным потенциалом нулевого выхода триггера числового блока 3 на элементе 12 формируется сигнал о неиоиравпости данного формирователя разрядных токов. Диагностика осуществляется как при записи, так и при считывании информации.

При заииси ипформации подсчитывается количество песравпепий, формируемых блоком 14 сравнения кода регистра числа числового блока 3 с кодом, воспроизводимым усилителями воспроизведения, подключенными к блоку 14 сравнения через элемент «ИЛИ 13. При считывании блок 14 сравнивает код эталонного слова с выходов блока 8 с кодом, воспроизводимым усилителями воспроизведения числового блока 3.

Блок 8 представляет собой цифровой авто.мат, формирующий последовательность эталоппых слов, позво.тяющих наиболее полно проверить различные части устройства. Сигпалы с выходов депшфратора 9, блока 10, элементов «И 12, блока 14 сравнения поступают на входы коммутатора 6. В зависимос1И от этих сигналов коммутатор 6 добавляет в соответствующий канал дополнительного пакопителя 5 единнчное ириращение. Цикл проверки повторяется необходимое число раз, после чего блок 4 управления включает блок 7 аиализа статистических даиных, который обрабатывает данные по программе диагностики устройства. В случае возможности выполнения этой программы центральным процессором последний обращается к блоку 5.

Формула изобретен и я

Оперативное запоминающее устройство, содержащее накопитель, подключенный к адресному блоку, соединенному со счетчиком адреса, и разрядному блоку, соединенному с одним из входов элемента «ИЛИ, выход которого подключен к первому входу блока сравнения, второй вход которого соединен с разрядным блоком, блоки контроля, соединенные с накопителем, элементы «И по количеству разрядов накопителя, одни из входов которых подключены К разрядному блоку, другие - к выходам одного из блоков контроля, дешифратор, блок управления, отличающееся тем, что, с целью повышения на/южности работы устройства и увеличения его быстродейств1 Я, оно содержит блок формирования эталонных слов, вход которого подключен к блоку управления, а выходы - к разрядному блоку и другому входу элемента «ИЛИ, коммутатор, входы которого подключены к выходам блока сравнения, элементов «И, другого блока контроля, блока управления и дешифратора, вход которого соединен с адрсскым блоком, дополнительный накопитель, входы которого подключены к выходам блока управления и коммутатора, блок анализа статистических данных, входы которого подключены к выходам блока управления и дополинтельного накопителя, а выход - к выходной И1ине устройства, регистр, входы и выходы которого подключены к соответствующим выходам и входам счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для управления роботом | 1983 |

|

SU1228074A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

1й-даау.кггг ду

Авторы

Даты

1975-12-15—Публикация

1974-04-05—Подача