1

Изобрете;ние относится к аналоговой вычислительной технике и может быть использовано в комплексе с аналоговыми вычлслительньши машинами для .воспроизведения функциональных зависимостей одной переменной.

Извесины аН1алого-циф:ровые функциональные преоб|р(азователи, содержащие источник onQpiHoro напряжения, бломи, памяти, дешифраторы, уаилителм, схему управления, счетчики, Тригге ры, регистры, цифровые управляемые резисторы и ключи.

Их недостатками являются «изкая точность и нестабильность воспроизведения заданной функции.

Предложенный многоканальный аналогоцифровой функциональный преобразователь, с целью повышения точности и стабильности, содержит много«а,нальный аналоговый запоми.наюш,Ий блок, входы которого через переключатель каналов присоединены к выходу первого операционного усилителя, подключенного через цифровые удравляемые резисторы к источ,11ику onQpiHoro напряжения и к выхода.м второго и третьего опе|рационных усилителей и присоединенного через резистор и ключи, к выходам четвертого и пятого операционных усилителей. Вход второго операционного усилителя подключен через цифровой управляемый резистор к источнику опорного напряжения п через переключатель каналов и резисторы соединен с входными клеммами. Вход и выход третьего операционного усилителя соедипены соответственно с выходом второго операционного усилителя и со входами квадратора, выход которого через шестой операционный усилитель и цифровой управляемый резистор присоединен к последовательно включенным четвертому и пятому операционным усилителям. Управляюш,ие входы всех цифровых управляемых резисторов соединены с выходами резисторов, входы которых подключены через схемы совпадения к выходам усилителей блоков памяти и выходу аналогоцифрового преобразоватеЛЯ, присоединенного к схеме управления, к дешифратору и через переключатель каналов ко входпым клеммам. Вход счетчика соединен с выходом схемы управления, а его выход подключен к одному из

входов дешифратора, вход триггера знака подключен через схему совпадепия к выходу одного из усилителей блока памяти.

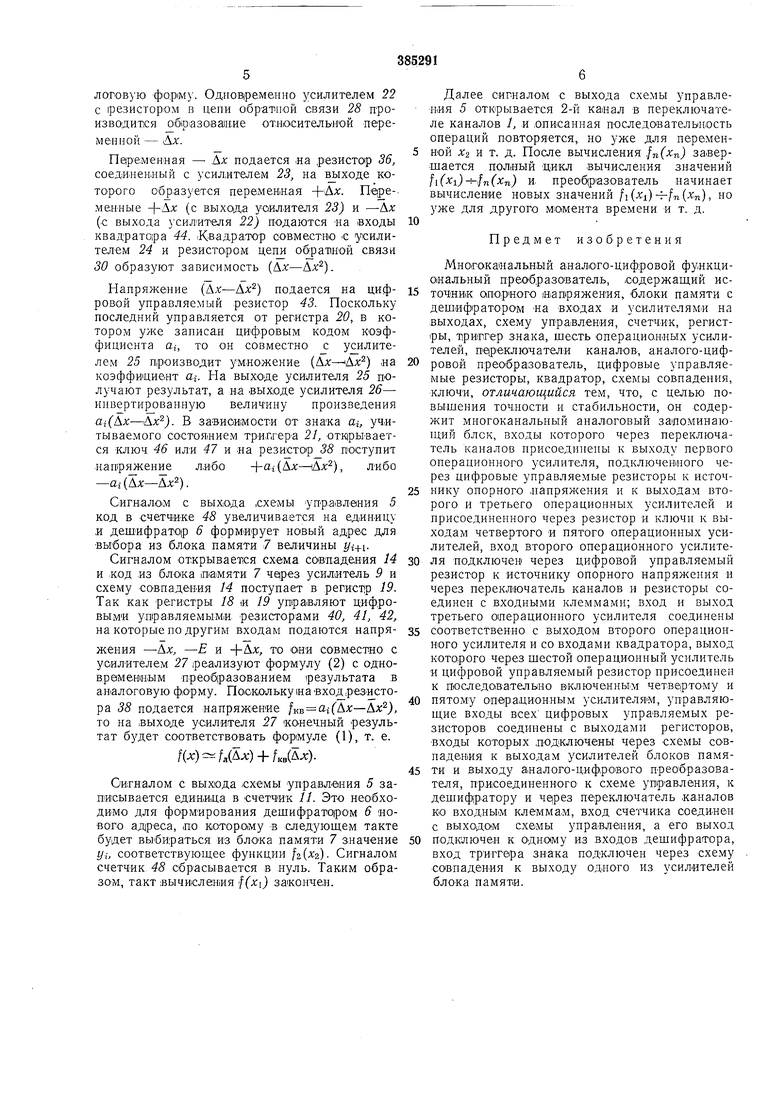

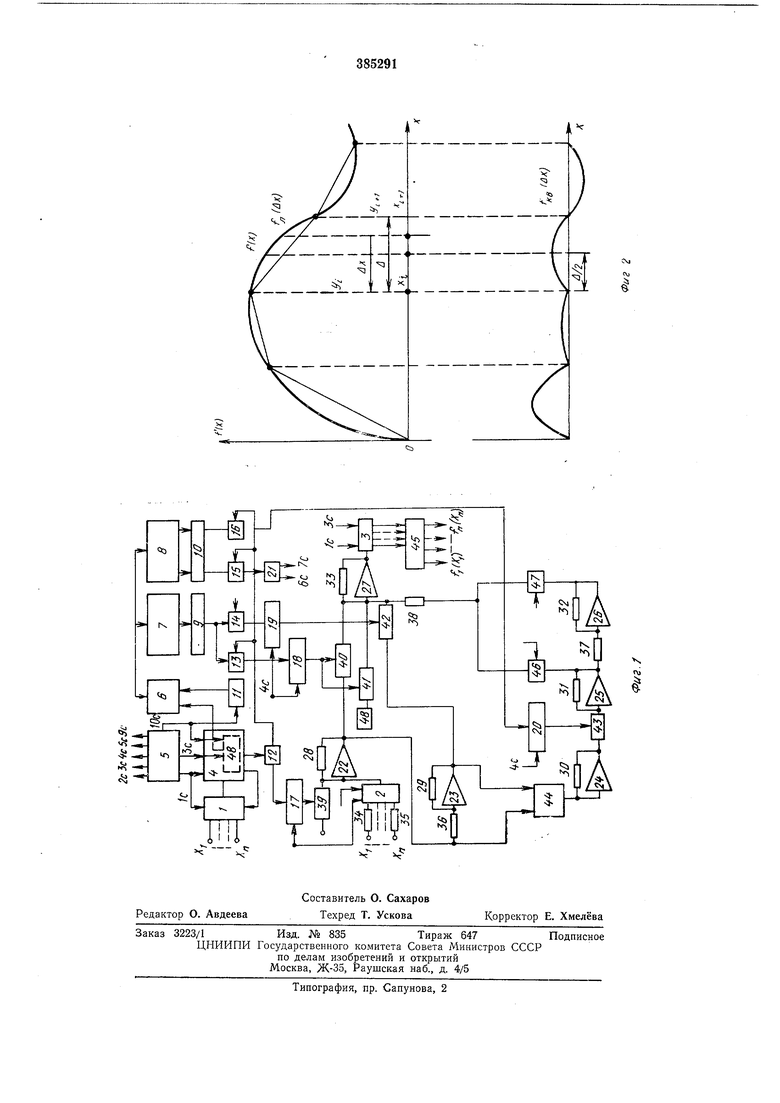

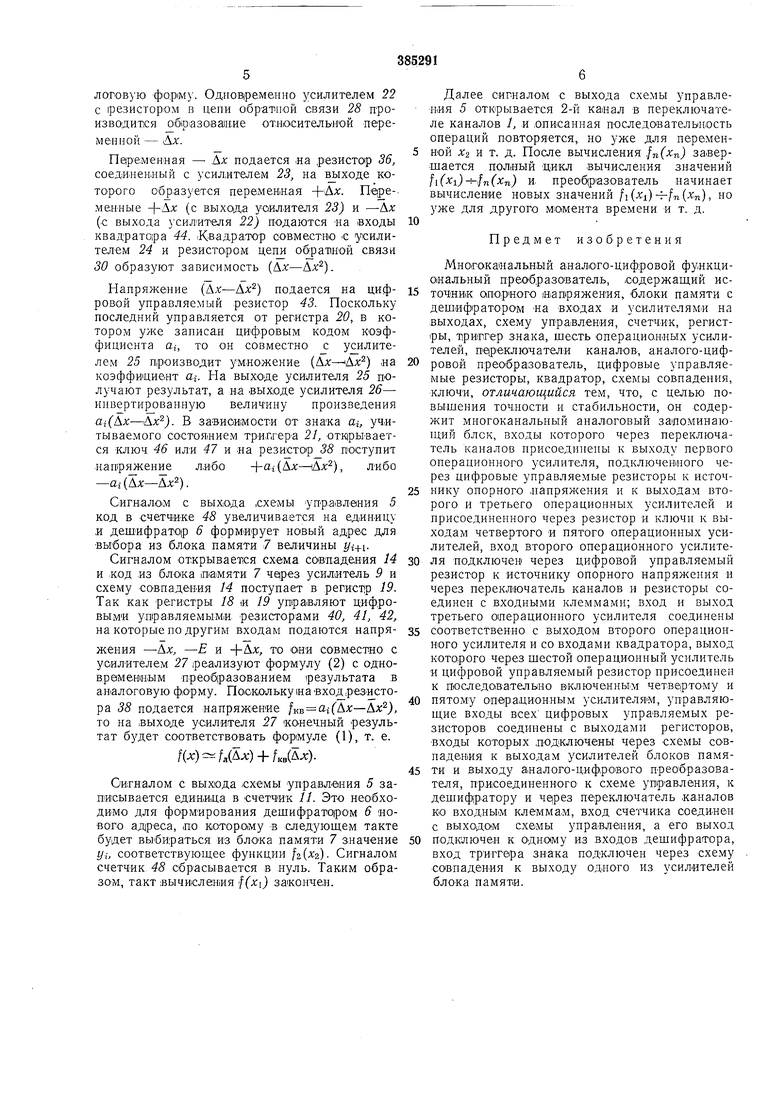

На фиг. 1 показана блок-схема устройства; на фиг. 2 изображен гр1афик аппроксимации функции.

Для воспрюиЗВедения заданной зависимости

f(x) ось независимой переменной разбивается

на N интервалов и на каждом интервале

функция f(x) представляется состоящей из двух слагаемых: линейкой зависимости от относителыюй координаты Ал и квадратичной (фиг. 2), т. е. f()WA.v) + UM,(1) /л(Лл) У; + ((/«+ - г//)Дл:, f,3(AA:) ai(x - Кх). Здесь: Ад: - координата текущей точки относительно Хг, А - величина интервала; уь z/j+i - значения функции f(x) в точках Хг и Xi+i; иг - постоянный для i-ro участка коэффициент. Знак коэффициента оир.еделяется знаком ;раЗ:НосТ|И f(x)-,fn(Ax) ,на участке номе.ра . Вел-ичин,а а может быть оиределана из условия миНимума ореднеквадратичной ошибки между f(x) и /a Axj-f/квСАлг) на I-M участке ил.и другими 1методами, например, приближенно положить (а,.) 4lf(x) - )x z 0,5. в устройстве при подаче на его входы независимых переменных Xi, Xz,..., Хп восшроязводятся функции /i(-«:). Ш) . . . ), причем каждая из функций |i-fn воспроизводится в соответствии с приведенными формулами. Функции fi-,fn .вычисляются последовательно во времени. Блок-схема устройства, представленная на фиг. 1, состоит из переключателей каналов 1, 2, 3, ан алого-цифрОВОГо преобразователя 4, схемы упра:вления 5, дешифратора 6, блоков памяти 7 ц 8, подключенных к ним усилителей 9 и 10, счетчика Л, cxeiM С0|впадения 12- 16, регистров 17-20, тригге ра 3|Н.ака 21, операционных усилителей 22-27 с резисто1рами 28-33 в ценях обратной связи, входными резисторЭ.ми 34-38 а цифровыми упр|авляемы:ми резисторами 55-43, квадратора 44, многоканального аналогового запоминающего блока 45, ключей 46, 47 и счетчика 48. Основные элементы схемы технически (Могут быть выполнены следующим образом: аналого-цифровой преобразователь 4 - времяимпульсного типа или поразрядного кодирования, дешифратор 6 - ,на диодной матрице, блоки памяти 7 и 5 - на диодах, регистры и счетчики - на три1ггерах, каждая из схем цифровых управляемых резисторов 39-43-на параллельных резистор.ах, подключенных через ключевые схемы к операционному усилителю, юваД|р1атор 44 - как аналоговый блок на диодных ячейках, .подключаемых к операционному усилителю 24, 1М1цотокан1альный аналоговый запоминающий блок 45 - на операЦИОН1НЫХ усилителях с конденсаторами в цепи обратной связи. Преобразователь работает следующим образом. 5 10 15 20 25 30 35 40 45 50 55 60 65 В блоки памяти 7 к 8 щредварительно заносятся значения Уг и коэффициентов иг для Bicex п функций. Независимые переменные подключаются ко входу уст1ройства. ПоСледовательность операций по .выч.ислению функций ацр еделяется схемой упра влен1ия 5, выр|абатывающей управляющие си-пналы. Каждый ЦИ1КЛ вычи1сления значений функций fi(xi) состоит из п тактов, и в каждом такте вычисляется значение лишь одной из этих функций. Проследим работу преобразователя в процессе выпол1нения одного из тактов, например первого. Сигналом с выхода схемы управления 5 открывается 1-й «анал в переключателе каиалов 1, и пераменн.ая х через переключатель каналоВ подается на вход аналого-цифрового преобразователя 4, запускаемого этим сигналом. Аналого-цифровой преобразователь начинает преобр1азован.ие в код переменной х, выделяя при этом лишь старщие разряды вел.ичины Xi (номер интервала). Сигналом с выхода схемы 5 открывается также /1-й канал в переключателе ка.налов 3, и результат вычисления в предыдущем такте, полученный на выходе усил.ителя 27, т. е. fn(xn), начинает записываться в М|НОгоканаль.ный аналоговый запоминающий блок 45. Сигнал, вырабатываемый схемой преобразователя 4 по окончании кодирования переменной Xi, закрывает 1-й канал в переключатеЛе каналов 1. Результат кодирования Xi фиксируется в счетчике 48, входящем в состав ана.лого-цифрового преобразователя 4 (в счетчике 48 записываются лишь старшие разряды величины xi - .номер интервала по оси х). Так. как счетчик 48 связан с дешифратором 6, на выходе деш.и.фратора возбуждается соответствующая адресная шина для выбора из блока памяти 7 соответствующей величины уг и коэффициента иг - из блока памяти 8. Далее закрыва.ется п-й канал в переключателе каналов 3 (функция fn(Xn) записана в ан|ало говый запоминающий блок 45). Сигналом с выхо.да схемы 5 закрывается я-ый канал в переключателе .каналов 2. Одновременно регистры 17-20 сбрасываются в нуль и открываются схемы совпадения 12, 13 и -15, 16. В регистр 17 переписывается код из счетчика 48, в регистр 75 через усилитель 9 и схему совпадения 13 заносится код г/г .из блока памяти 7, в регистр 20 че1рез усилитель 10 и схему совпадения 16 заносится коэффициент а, из блока памяти 8, а тр.аггер 21 фиксирует знак коэффициента uj. Сигналом открывается также 1-й канал в переключателе каналов 2 1И перемеЕная х подается .на вход усилителя 22. Поскольку с усил.ителем 22 соединен также цифровой упр.авляемый резистор 39, на который подается п.остоянное напряжение Е, а с другой cTOipoHbi управляющий код, записанный в регистре 17, то обеснечивается npeo6ipaзование записанно.го в регистре 17 кода в аналотовую ф|О.р1му. Одпов|ремвиио усилителем 22 с 1резистором в цепи обратпой связи 28 производится обю азоваигие относительной переменной - ДА . П ремениая - Ал; подается .на резистор 36, соед;И.нен.ный с усил,ителем 23, па вь1ходе которого Обр.азуется перемеиная . Пфе-менные (с выхода усилителя 23) и -Дл: (С выхода усилителя 22) подаются «а входы квадрато1ра 44. гКвадра.тор совместно € усилителем 24 и резистором цепи обратной связи 30 образуют зависимость (Д.г-Дл;). Напряжение () подается на циф- is ровои управляемый резистор 43. Поскольку последний управляется от регистра 20, в котором уже записан цифровым кодом коэффициснта ui, то он совместно с усилителем 25 производит умножение (Дх-Д;) ,jja 20 коэффищиент иг. На выходе усилителя 25 получают результат, а на выходе усилителя 26- инвертированную величину произведения аг(Дл:-Ах). В зависи мости от знака ai, учитываемого состоянием триггера 21, открывается КЛЮЧ 46 или 47 и на резистор 38 поступит напряжение либо -}-ai(), либо -аг(Ах-Ах }. Сигналом с выхода схемы упр.авления 5 код в счетчике 48 увеличивается на единицу и дешифратор 6 формирует новый адрес для выбора из блока памяти 7 величины . Сигналом открывается схема совпадения 14 зо и код из блока памяти 7 че(рез усилитель 9 и схему совпадения 14 поступает в регист р 19. Так как регистры 18 и 19 управляют цифровыми управляемыми резистор ами 40, 41, 42, на которые по другим входам подаются напря- 35 дд; и +Кх то они совместно с усилителем 27 реализуют формулу (2) с одновременным преобразованием результата в аналоговую форму. Поскольку на вход р езисто„„,...-г г 04 40 ра 38 подается напряжение 1 а(). то на выходе усилителя 27 конечный результат будет соответствовать формуле (1), т. е. /(х)(ДА-) + /кв(А-). Сигналом с выхода схемы управления 5 записывается едини,ца в счетчик //. Это необходимо для формирования дешифратором 6 нового адреса, по которому в следующем такте будет выбираться из блока памяти 7 значение 50 Уг, соответствующее функции fz(xz)- Сигналом счетчик 48 сбрасывается в нуль. Таким образом, такт ;вычислен1ия 1(Х) закончен. 5 25 45 Далее сигналом с выхода схемы управления 5 открывается 2-й каиал в переключателе каналов /, ,и ,олисанная последовательность операций повторяется, цо уже для переменной Х2 и т. д. После вычисления fn(xn) завершается полный ЦИКЛ вычисления значений f(xi)n(xn) и, преобр азователь начинает вычисление новых значений li(Xi)(Xn), но уже для другого момента времени и т. д. Предмет изобретения Многокаиальный аналого-цифровой функциональный преобразователь, содержащий источяик опорного напряжения, -блоки памяти с дешифратором на входах и усилителями на выходах, схему управления, счетчи:к, регист р призер знака, шесть операционных усили п реключатели каналов, аналого-цифровой преобразователь, цифровые управляемые резисторы, квадратор, схемы со1впадения, ключи, отличающийся тем, что, с целью повышения точности и стабильности, он содержит многоканальный аналоговый за поминающий блок, входы которого через переключатель каналов присоединены к выходу первого операционного усилителя, подключенного через цифровые управляемые резисторы к источнику опорного |Напряжения и к выходам второго и третьего операционных усилителей и присоединенного через резистор и ключи к выходам четвертого и пятого операционных усилителей, вход второго операционного усилителя подключен через цифровой управляемый резистор к источнику опорного напряжения и через переключатель каналов и резисторы соединен с входными клеммами; вход и выход третьего операционного усилителя соединены соответственно с выходом второго операцион™го усилителя и со входами квадратора, выход которого через шестой операционный усилитель и цифровой управляемый резистор присоединен к последо вательно ВКлюченнььм четве ртому и пятому операционным усилителяМ, управляювходы всех цифровых управляемых резисторов соединены с выходами регисторов, входы которых подключены через схемы совпадения к выходам усилителей блоков памяти и выходу аналого-цифрового преобразователя, присоединенного к схеме управления, к дешифратору и че|рез переключатель каналов ко входным клемма.м, вход счетчика соединен с выходом схемы управления, а его выход подключен к одному из входов дешифратора, вход триггера знака подключен через схему совпадения к выходу одного из усилителей блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный аналого-цифровой преобразователь | 1972 |

|

SU493019A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Устройство аналого-цифрового преобразования | 1991 |

|

SU1807559A1 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1462475A1 |

| ПОЛИГАРМОНИЧЕСКИЙ ПРЕДСКАЗЫВАЮЩИЙ ФИЛЬТР | 1993 |

|

RU2046359C1 |

| Устройство для цифровой индикации многоканального регулятора температуры | 1983 |

|

SU1211709A1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

Авторы

Даты

1973-01-01—Публикация