со

СХ

tmi

о:) со

4

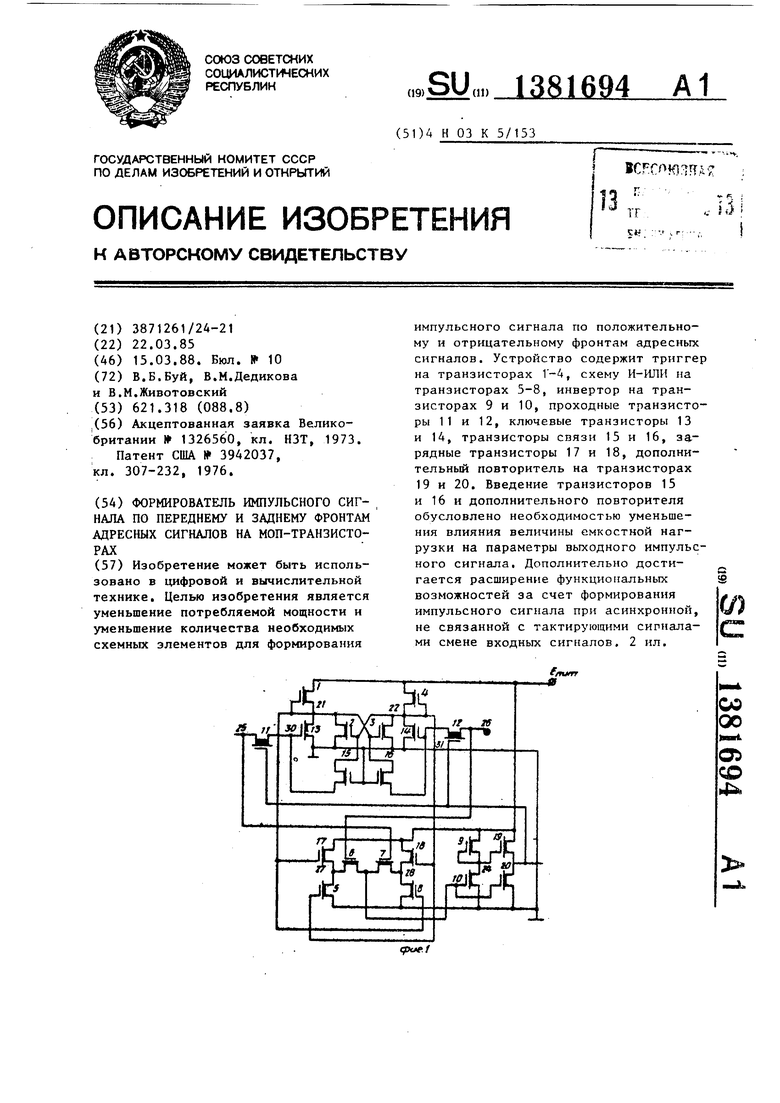

Предлагаемое устройство относится к импульсной технике ч может быть использовано в цифровой вычислительной технике.

Целью изобретения является уменьшение потребляемой мощности и уменьшение количества элементов при формировании импульсного сигнала по обоим (положительному и отрицатель- ному) фронтам адресных сигналов.

Дополнительно достигается расширение функциональных возможностей за счет формирования импульсного сигнала при асинхронной (не связан- ной с тактирующими сигналами) смене входных сигналов.

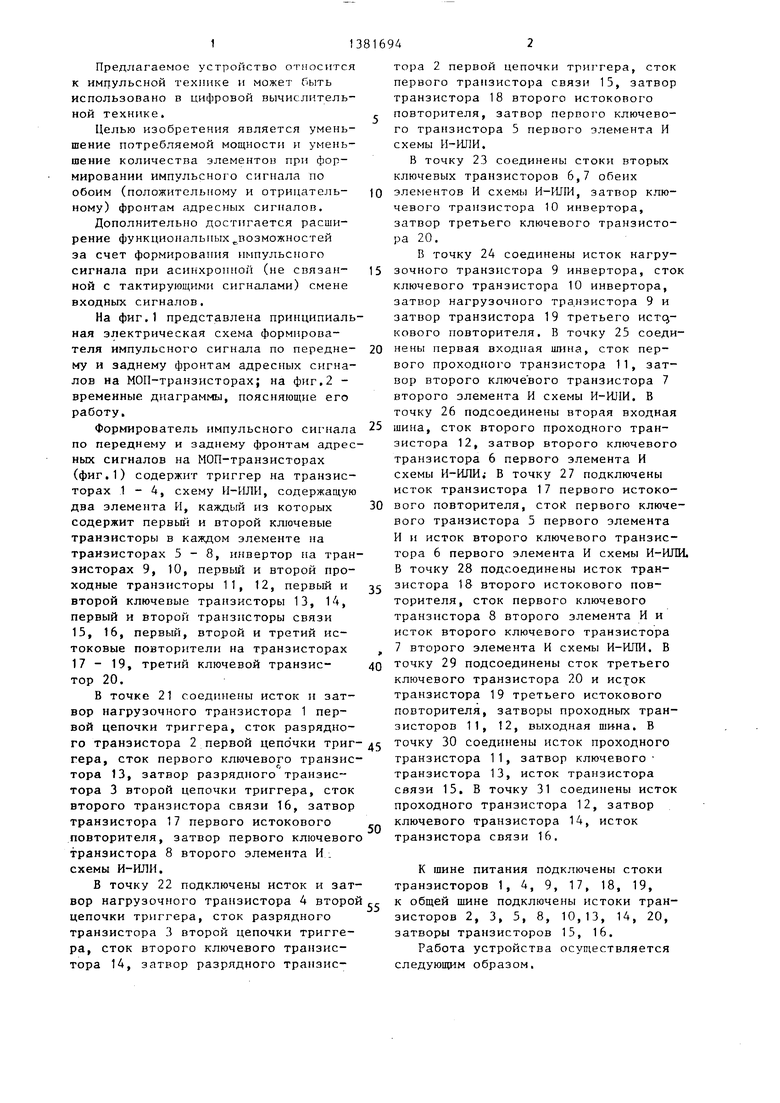

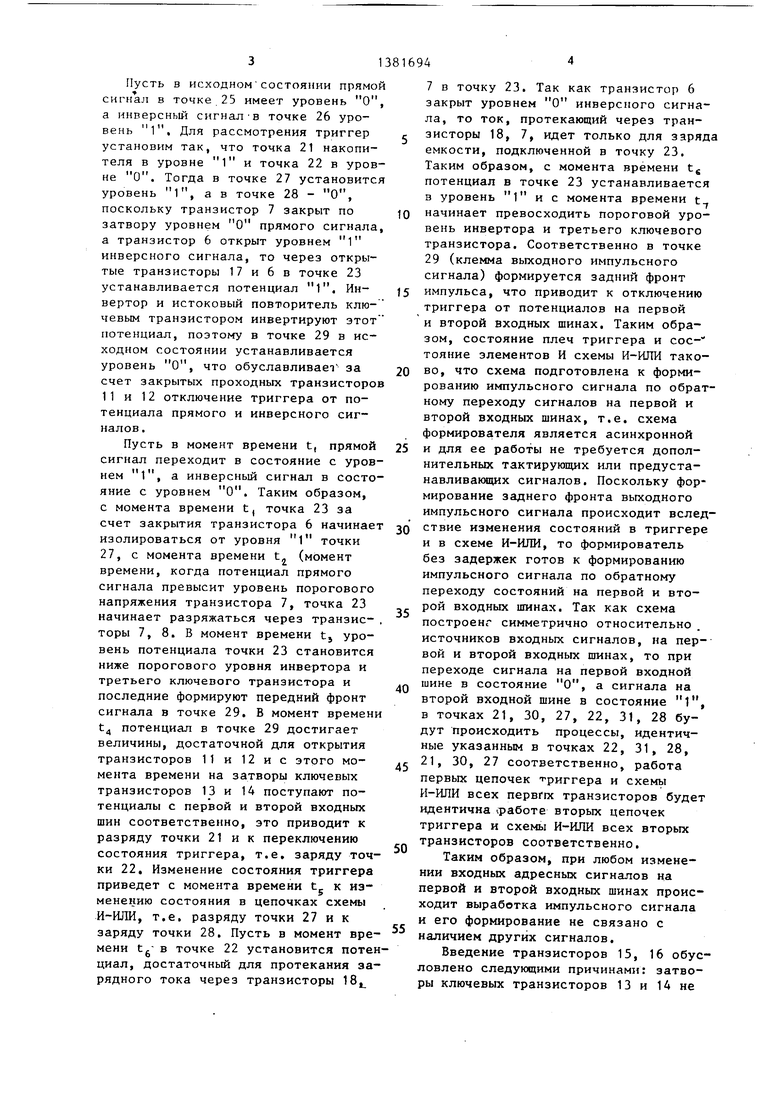

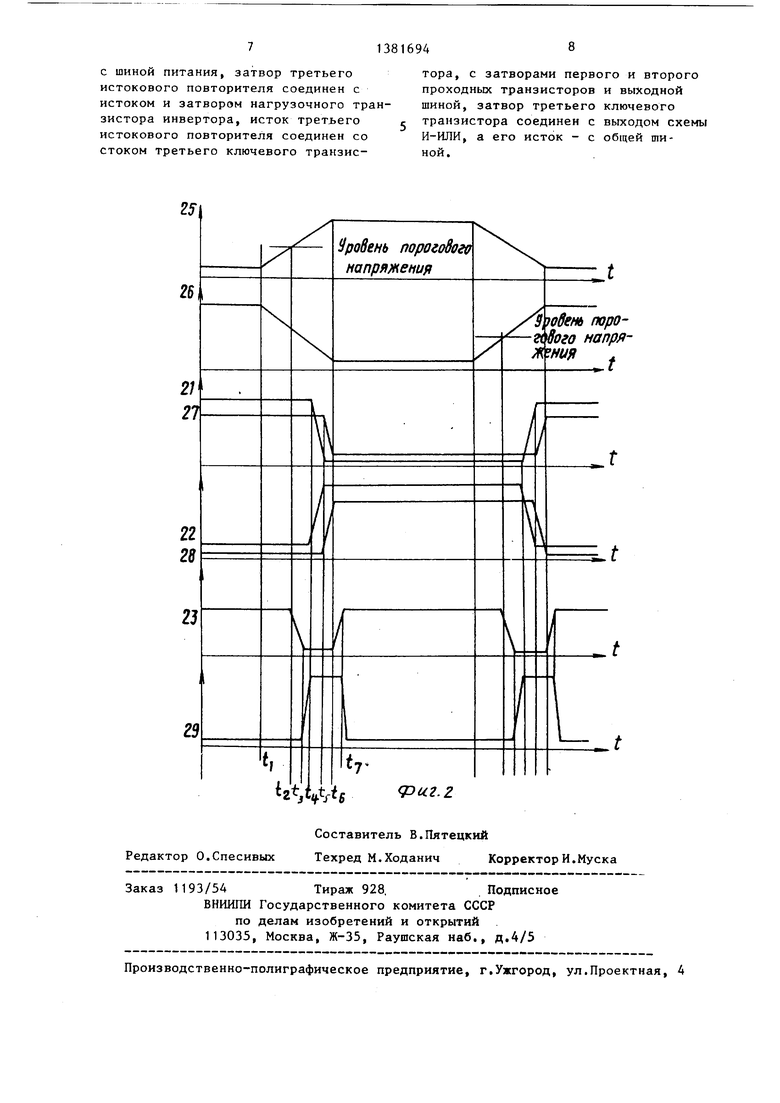

На фиг.1 представлена принципиальная электрическая схема формирователя импульсного сигнала по передне- му и заднему фронтам адресных сигналов на МОП-транзисторах; на фиг.2 - временные диаграммы, поясняющие его работу.

Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП-транзисторах (фиг.1) содержит триггер на транзисторах 1-4, схему И-ИЛИ, содержащую два элемента И, каждый из которых содержит первьд и второй ключевые транзисторы в каждом элементе на транзисторах 5-8, инвертор на транзисторах 9, 10, первьш и второй проходные транзисторы 11, 12, первый и второй ключевые транзисторы 13, 14, первый и второй транзисторы связи 15, 16, первый, второй и третий ис- токовые повторители на транзисторах 17 - 19, третий ключевой транзис- тор 20.

В точке 21 соединены исток и затвор нагрузочного транзистора 1 первой цепочки триггера, сток разрядного транзистора 2 первой цепо чки триг гера, сток первого ключевого транзистора 13, затвор разрядного транзистора 3 второй цепочки триггера, сток второго транзистора связи 16, затвор транзистора 17 первого истокового повторителя, затвор первого ключевог транзистора 8 второго элемента И: схемы И-ИЛИ.

В точку 22 подключены исток и затвор нагрузочного транзистора А второ цепочки триггера, сток разрядного транзистора 3 второй цепочки триггера, сток второго ключевого транзистора 1А, затвор разрядного транзистора 2 первой цепочки триггера, сток первого транзистора связи 15, затвор транзистора 18 второго истокового повторителя, затвор первого ключевого транзистора 5 первого элемента И схемы И-ИЛИ.

В точку 23 соединены стоки вторых ключевых транзисторов 6,7 обеих элементов И схемы И-ИЛИ, затвор ключевого транзистора 10 инвертора, затвор третьего ключевого транзистора 20.

В точку 24 соединены исток нагрузочного транзистора 9 инвертора, сто ключевого транзистора 10 инвертора, затвор нагрузочного тра.нэистора 9 и затвор транзистора 19 третьего HCTQ- кового повторителя. В точку 25 соединены первая входная шина, сток первого проходного транзистора 11, затвор второго ключевого транзистора 7 второго элемента И схемы И-ИЛИ. В точку 26 подсоединены вторая входная шина, сток второго проходного транзистора 12, затвор второго ключевого транзистора 6 первого элемента И схемы И-ИЛИ; В точку 27 подключены исток транзистора 17 первого истоко- вого повторителя, стой первого ключевого транзистора 5 первого элемента И и исток второго ключевого транзистора 6 первого элемента И схемы И-ИЛ В точку 28 подсоединены исток транзистора 18 второго истокового повторителя, сток первого ключевого транзистора 8 второго элемента И и исток второго ключевого транзистора 7 второго элемента И схемы И-ИЛИ. В точку 29 подсоединены сток третьего ключевого транзистора 20 и транзистора 19 третьего истокового повторителя, затворы проходных транзисторов 11, 12, выходная шина. В точку 30 соединены исток проходного транзистора 11, затвор ключевого транзистора 13, исток транзистора связи 15, В точку 31 соединены исток проходного транзистора 12, затвор ключевого транзистора 14, исток транзистора связи 16.

К шине питания подключены стоки транзисторов 1, 4, 9, 17, 18, 19, к общей шине подключены истоки транзисторов 2, 3, 5, 8, 10,13, 14, 20, затворы транзисторов 15, 16.

Работа устройства осуществляется следующим образом.

Пусть в исходном состоянии прямой сигнал в точке 25 имеет уровень О, а инверсный сигналов точке 26 уровень 1, Для рассмотрения триггер установим так, что точка 21 накопителя в уровне 1 и точка 22 в уровне О. Тогда в точке 27 установится уровень 1, а в точке 28 - О, поскольку транзистор 7 закрыт по затвору уровнем О прямого сигнала, а транзистор 6 открыт уровнем 1 инверсного сигнала, то через открытые транзисторы 17 и 6 в точке 23 устанавливается потенциал 1. Инвертор и истоковый повторитель клго- чевым транзистором инвертируют этот потенциал, поэтому в точке 29 в исходном состоянии устанавливается уровень О, что обуславливает за счет закрытых проходных транзисторов 11 и 12 отключение триггера от потенциала прямого и инверсного CHI- налов.

Пусть в момент времени t, прямой сигнал переходит в состояние с уровнем 1, а инверсный сигнал в состояние с уровнем О. Таким образом, с момента времени t, точка 23 за счет закрытия транзистора 6 начинает изолироваться от уровня 1 точки 27, с момента времени t (момент времени, когда потенциал прямого сигнала превысит уровень порогового напряжения транзистора 7, точка 23 начинает разряжаться через транзис- торы 7, 8. В момент времени t, уровень потенциала точки 23 становится ниже порогового уровня инвертора и третьего ключевого транзистора и последние формируют передний фронт сигнала в точке 29. В момент времени t потенциал в точке 29 достигает величины, достаточной для открытия транзисторов 11 и 12 и с этого момента времени на затворы ключевых транзисторов 13 и 14 поступают потенциалы с первой и второй входных шин соответственно, это приводит к разряду точки 21 и к переключению состояния триггера, т.е. заряду точки 22, Изменение состояния триггера приведет с момента времени tg к изменению состояния в цепочках схемы И-ИЛИ, т.е. разряду точки 27 и к заряду точки 28. Пусть в момент времени t, в точке 22 установится потенb

циал, достаточный для протекания зарядного тока через транзисторы 18

5

0

5

0

5

0

5

0

5

7 в точку 23. Так как транзистор 6 закрыт уровнем О инверсного сигнала, то ток, протекающий через транзисторы 18, 7, идет только для заряда емкости, подключенной в точку 23. Таким образом, с момента времени tg потенциал в точке 23 устанавливается в уровень 1 и с момента времени t начинает превосходить пороговой уровень инвертора и третьего ключевого транзистора. Соответственно в точке 29 (клемма выходного импульсного сигнала) формируется задний фронт импульса, что приводит к отключению триггера от потенциалов на первой и второй входных шинах. Таким образом, состояние плеч триггера и сое- тояние элементов И схемы И-ШТИ таково, что схема подготовлена к формированию импульсного сигнала по обратному переходу сигналов на первой и второй входных шинах, т.е. схема формирователя является асинхронной и для ее работы не требуется дополнительных тактирующих или предуста- навливаюпщх сигналов. Поскольку формирование заднего фронта выходного импульсного сигнала происходит вследствие изменения состояний в триггере и в схеме И-ИЛИ, то формирователь без задержек готов к формированию импульсного сигнала по обратному переходу состояний на первой и второй входных шинах. Так как схема построенг симметрично относительно . источников входных сигналов, на пер-- вой и второй входных шинах, то при переходе сигнала на первой входной шине в состояние О, а сигнала на второй входной шине в состояние 1, в точках 21, 30, 27, 22, 31, 28 будут происходить процессы, идентичные указанным в точках 22, 31, 28, 21, 30, 27 соответственно, работа первых цепочек триггера и схемь И-ИЛИ всех первггх транзисторов будет идентична работе вторых цепочек триггера и схемы И-ИЛИ всех вторых транзисторов соответственно.

Таким образом, при любом изменении входных адресных сигналов на первой и второй входных шинах происходит выработка импульсного сигнала и его формирование не связано с наличием других сигналов.

Введение транзисторов 15, 16 обусловлено следующими причинами: затворы ключевых транзисторов 13 и 14 не

должны находиться в высокопмпедансном состоянии, в противном случае возможно ложное срабатывание триггера по наводкам; исключение транзисторов, т.е. замена закороткой, также невозможно, так как это приведет к увеличению емкостной и к появлению токовой нагрузки на источник входного сигнала.Ю

Введение транзисторов истоковых повторителей и третьего ключевого транзистора обуслоилено неоходимостью уменьшения влияния величины емкостной нагрузки на параметры выходного 5 импульсного сигнала. Все вновь вводимые элементы не приводят к изменению тока потребления элементов, входящих в общую часть прототипа и предлагаемого формирователя, количество вво- 20 димых элементов значительно меньше, чем в прототипе, кроме того, для работы формирователя не требуется наличие других устройств,тогда как для работы прототипа необходим регистр. 25

Фор м у ла изобретения

Формирователь импульсного сигнала по переднему и заднему фронтам ад- JQ ресных сигналов на МОП-транзисторах, содержащий триггер, схему И-ИЛИ, инвертор, первьш и второй ключевые транзисторы, первую и вторую входные ины, выходную шину, причем первое и второе плечи триггера содержат нагрузочный и ключевой транзисторы, в каждом плече, первый и второй элеенты И схемы И-ИЛИ содержат первый и второй ключевые транзисторы в каж- д,ч ом элементе И, инвертор содержит ключевой и нагрузочные транзисторы, стоки нагрузочных транзисторов и инвертора соединены с шиной питания, истоки первого, второго ключевых c транзисторов, ключевых транзисторов триггера, ключевого транзистора инвертора, первых ключевых транзисторов обоих элементов И схемы И-ИЛИ соединены с общей шиной, первый вы- ход триггера соединен с истоком и затвором нагрузочного, стоком ключевого транзистора первого плеча триггера, с затвором ключевого транзистора второго плеча триггера, с затвором первого ключевого транзис тора второго элемента И схемы И-ИЛИ, стоком первого ключевого транзистора, второй выход триггера соединен

35

50

,55

м Ю

5 2025

JQ д,ч c

35

50

55

с истоком и затвором нагрузочного, стоком ключевого транзистора второг о плеча триггера, с затвором ключевого транзистора первого плеча триггера, с затвором первого ключевого транзистора первого элемента И схемы И-ИЛИ, стоком второго ключевого транзистора, первая входная шина соеди- нена с затвором второго ключевого транзистора второго элемента И схемы И-ИЛИ, вторая входная шина соединена с затвором второго ключевого транзистора первого элемента И схемы И-ИЛИ, выход схемы И-ИЛИ соединен со стоками вторых ключевых транзисторов элементов И схемы И-ИЛИ, с затвором ключевого транзистора инвертора, сток которого соединен с истоком и затвором нагрузочного транзистора инвертора, отличающий ся тем, что, с целью уменьшения потребляемой мощности и упрощения при формировании импульсного сигнала как по переднему, так и по заднему фронтам адресных сигналов, в него дополнительно введены первый и второй проходные транзисторы, первый и второй транзисторы связи, первый, второй и третий истоковыё повторители, третий ключевой транзистор, причем стоки первого и второго проходных транзисторов соединены с первой и второй входными шинами соответственно, исток первого проходного тран-, зистора соединен с .затвором первого ключевого транзистора и с истоком первого транзистора связи, исток второго проходного транзистора соединен с затвором второго ключевого транзистора и истоком второго транзистора связи, затворы первого и второго транзисторов связи соединены с общей шиной, первьй выход -триггера соединен со стоком второго транзистора связи, с затвором первого ис- токового повторителя, исток которого соединен со стоком первого ключевого и с истоком второго ключевого транзисторов первого элемента И схемы И-ИЛИ, второй выход триггера соединен со стоком первого транзистора связи, с затвором второго истоково- го повторителя, исток которого соединен со стоком первого ключевого и с истоком второго ключевого транзисторов второго элемента И схемы И-ИЛИ, стоки первого, второго и третьего истоковых повторителей соединены

с шиной питания, затвор третьего истокового повторителя соединен с истоком и затвором нагрузочного транзистора инвертора, исток третьего истокового повторителя соединен со стоком третьего ключевого транзистора, с затворами первого и второго проходных транзисторов и выходной шиной, затвор третьего ключевого транзистора соединен с выходом схемы И-ИЛИ, а его исток - с общей тиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах | 1984 |

|

SU1249695A1 |

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Формирователь адресных сигналов для блоков памяти | 1983 |

|

SU1163354A1 |

| Двухтактный усилитель импульсного сигнала | 1981 |

|

SU1108611A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Стабилизатор постоянного напряжения | 1988 |

|

SU1557552A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА НОРМАЛЬНО ОТКРЫТЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1987 |

|

SU1530059A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

Изобретение может быть использовано в цифровой и вычислительной технике. Целью изобретения является уменьшение потребляемой мощности и уменьшение количества необходимых схемных элементов для формирования импульсного сигнала по положительному и отрицательному фронтам адресных сигналов. Устройство содержит триггер на транзисторах 1-4, схему И-ИЛИ на транзисторах 5-8, инвертор на транзисторах 9 и 10, проходные транзисторы 11 и 12, ключевые транзисторы 13 и 14, транзисторы связи 15 и 16, за,- рядные транзисторы 17 и 18, дополнительный повторитель на транзисторах 19 и 20. Введение транзисторов 15 и 16 и дополнительного повторителя обусловлено необходимостью уменьшения влияния величины емкостной нагрузки на параметры выходного импульсного сигнала. Дополнительно достигается расширение функциональных возможностей за счет формирования импульсного сигнала при асинхронной, не связанной с тактирующими сигналами смене входньк сигналов, 2 ил. S

вровень порогового напря кения

гэ

- -«

7offeM6 поро- Зого напря-

Авторы

Даты

1988-03-15—Публикация

1985-03-22—Подача