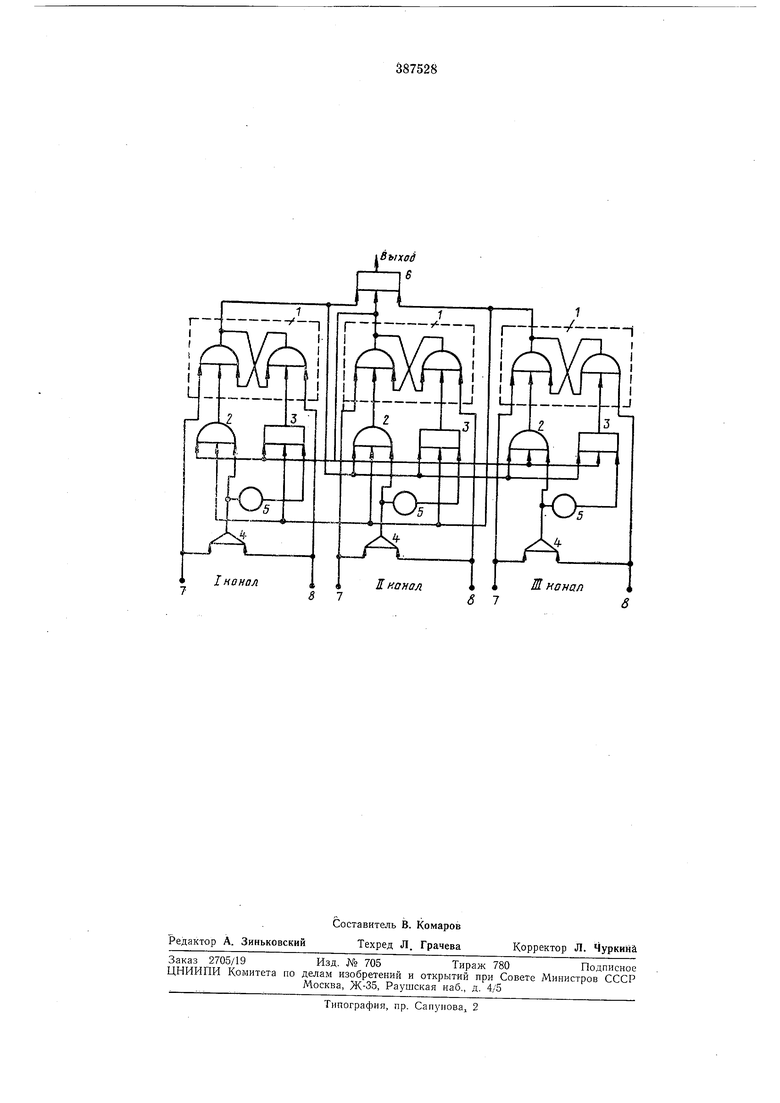

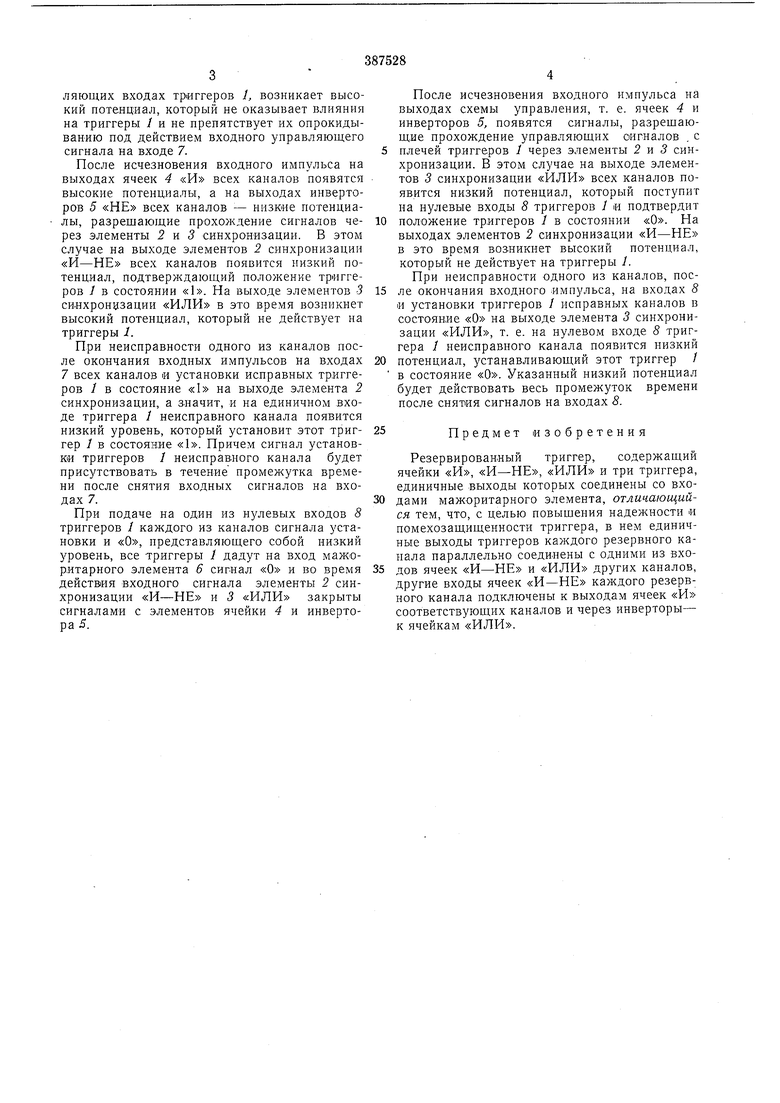

Изобретение относится к вычислительной технике и может найти применение в счетнорешающих устройствах повышенной «адежноСТ1И, а также в системах автоматического контроля и регулирования. Известны трехканальные триггерные устройства с мажоритарным выходом, содержащие триггеры, ячейки «И, «ИЛИ, «НЕ и мажоритарный элемент. Однако известные устройства отличаются сложностью, что обусловлено применением дополнительных источников тактовых импульсов, применением цепи обратной связи с выхода мажоритарного элемента и увеличением обшего числа связей между каналами, что вызывает дополнительные усложнения схемы, особенно в тех случаях, когда для повышения показателей помехозащищенности при длинных линиях связи, а также для повышения надежности при различных неисправностях, все; каналы и выходы обратной связи с мажоритарного элемента должны быть гальванически развязаны между собой. Целью изобретения является повышение надеж.ности и помехозаш,ищенности устройства с мажоритарным выходом с минимальным количеством связей между каналами. Для этого единичные выходы триггеров каждого резервного канала параллельно соединены с одними из входов ячеек «И-НЕ и «ИЛИ других каналов, другие входы ячеек «И-НЕ каждого резервного канала подключены к выходам ячеек «И соответствующих каналов и через инверторы - к ячейкам «ИЛИ. Изобретение пояснено чертежом. Устройство содержит триггеры /, собранные на основе ячеек «И-НЕ, трехвходовые элементы 2 синхронизации «И-НЕ для единичных входов триггеров / и трехвходовые элементы 3 синхронизации «ИЛИ для нулевых входов триггеров 1, схему управления, состоящую из последовательно соединенных двухвходовой ячейки 4 «И и инвертора 5 «НЕ, выходы которых управляют элементами 2 и 3 синхронизации, а также мажоритарного элемента 6, ко входам которого подсоединены единичные выходы триггеров /. Устройство работает следуюц;им образом. При подаче на один из единичных входов 7 всех триггеров / сигнала установки триггеров / в состояние «1, который представляет собой низкий уровень, все триггеры 1 устанавливаются в состояние «1 и подают «а вход мал оритарного элемента 6 сигнал «1. Во время действия входного сигнала элементы 2 н 3 синхронизации закрыты соответственно низким и высоким уровнями с элементов ячейки 4 «И и 5 «НЕ, а на выходе элементов 2 и 3 синхронизации, а значит, и на вторых управляющих входах триггеров 1, возникает высокий потенциал, который не оказывает влияния на триггеры / и не препятствует их опрокидыванию под действием входного управляюпдего сигнала на входе 7.

После исчезновения входного импульса на выходах ячеек 4 «И всех каналов появятся высокие потенциалы, а на выходах инверторов 5 «НЕ всех каналов - низкие потенциалы, разрешающие прохождение сигналов через элементы 2 н 3 синхронизации. В этом случае на выходе элементов 2 синхронизации «И-НЕ всех каналов появится низкий потенциал, подтверждающий положение триггеров / в состоянии «1. На выходе элементов 3 синхронизации «ИЛИ в это время возникнет высокий потенциал, который не действует на триггеры 1.

При неисправности одного из каналов после окончания входных импульсов на входах 7 всех каналов и установки исправных триггеров / в состояние «Ь на выходе элемента 2 синхронизации, а значит, и на единичном входе триггера 1 неисправного канала появится низкий уровень, который установит этот триггер 1 в состояние «1. Причем сигнал установки триггеров / неисправ-ного канала будет присутствовать в течение промежутка времени после снятия входных сигналов на входах 7.

При подаче на один из нулевых входов 8 триггеров / каждого из каналов сигнала установки и «О, представляющего собой низкий уровень, все триггеры / дадут на вход мажоритарного элемента 6 сигнал «О и во время действия входного сигнала элементы 2 синхронизации «И-НЕ и 3 «ИЛИ закрыты сигналами с элементов ячейки 4 и инвертора S.

После исчезновения входного импульса на выходах схемы управления, т. е. ячеек 4 и инверторов 5, появятся сигналы, разрешающие прохождение управляющих сигналов . с плечей триггеров 1 через элементы 2 и 5 синхронизации. В этом случае на выходе элементов 3 синхронизации «ИЛИ всех каналов появится низкий потенциал, который поступит на нулевые входы 8 триггеров 1 и подтвердит

положение триггеров 1 в состоянии «О. На

выходах элементов 2 синхронизации «И-НЕ

в это время возникнет высокий потенциал,

который не действует на триггеры /.

При неисправности одного из каналов, после окончания входного импульса, на входах 8 и установки триггеров / исправных каналов в состояние «О на выходе элемента 3 синхронизации «ИЛИ, т. е. на нулевом входе 5 триггера / неисправного канала появится низкий

потенциал, устанавливающий этот триггер / в состояние «О. Указанный низкий потенциал будет действовать весь промежуток времени после снятия сигналов на входах 8.

Предмет изобретения

Резервированный триггер, содержащий ячейки «И, «И-НЕ, «ИЛИ и три триггера, единичные выходы которых соединены со входами мажоритарного элемента, отличающийся тем, что, с целью повыщения надежности « помехозащищенности триггера, в нем единичные выходы триггеров каждого резервного канала параллельно соединены с одними из входов ячеек «И-НЕ и «ИЛИ других каналов, другие входы ячеек «И-НЕ каждого резервного канала подключены к выходам ячеек «И соответствующих каналов и через инверторы- к ячейкам «ИЛИ.

I Выход

/---i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации входных сигналов многоканальной дискретной системы | 1975 |

|

SU565294A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ СИГНАЛОВ | 1973 |

|

SU378830A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| Система обработки информации | 1990 |

|

SU1795468A1 |

| Резервированное пересчетноеуСТРОйСТВО | 1978 |

|

SU834923A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Коммутатор для переключения резервных генераторов | 1988 |

|

SU1541763A1 |

| Трехканальное резервированное устройство для синхронизации сигналов | 1983 |

|

SU1221769A1 |

Авторы

Даты

1973-01-01—Публикация