1

Изобретение относится к вычислительной технике.

Устройст-во может быть использовано как в электронных вычислительных машинах, так и в различных устройствах автоматики для интегрирования в течение длительного времени некоторой входной информации, представленной в виде напряжения синусоидальной или а-налоговой фopJмы.

Известно интегрирующее устройство, содержащее интегрирующий усилитель с коЯлЧенсатором в цепи обратной связи, .пороговый элемент, выход которого подключен к .коммутатору И ко входу запоминающего преобразователя, -сумматор, блок вычитания и управляемые с выхода коммутатора вентили.

Для данного устройства характерны невозможность вьтолйеиия долговременного интегрирования синусоидального входного сигнала, низкая точность результата интегрирования, .вызванная значительным временем раврйда Нако.пительного конденсатора интегрирующего усилителя; невысокая надежность и узкая область применения.

Цель изобретения - повышение точности долговременного интегрирования и надежности работы устройства.

Предлагаемое устройство отличается тем, что источник входного ситналв лодключен ко входу интегрирующего уоилителя через поS

следовательно соединенные лреобразойатёль полярности и входные управляемые вентили, выход усилителя -- ко вхоДу одного выходного управляемого вентиля непосредственно и 5 через блок вычитания - ко входу другого выходного управляемого вентиля; выходы вентилей объединены и соединены с оДним из входов порогового элемента и -сумматора, другой вход noporoBOiro элемента и вход блока вычитания подключены к источнику опорного напряжения.

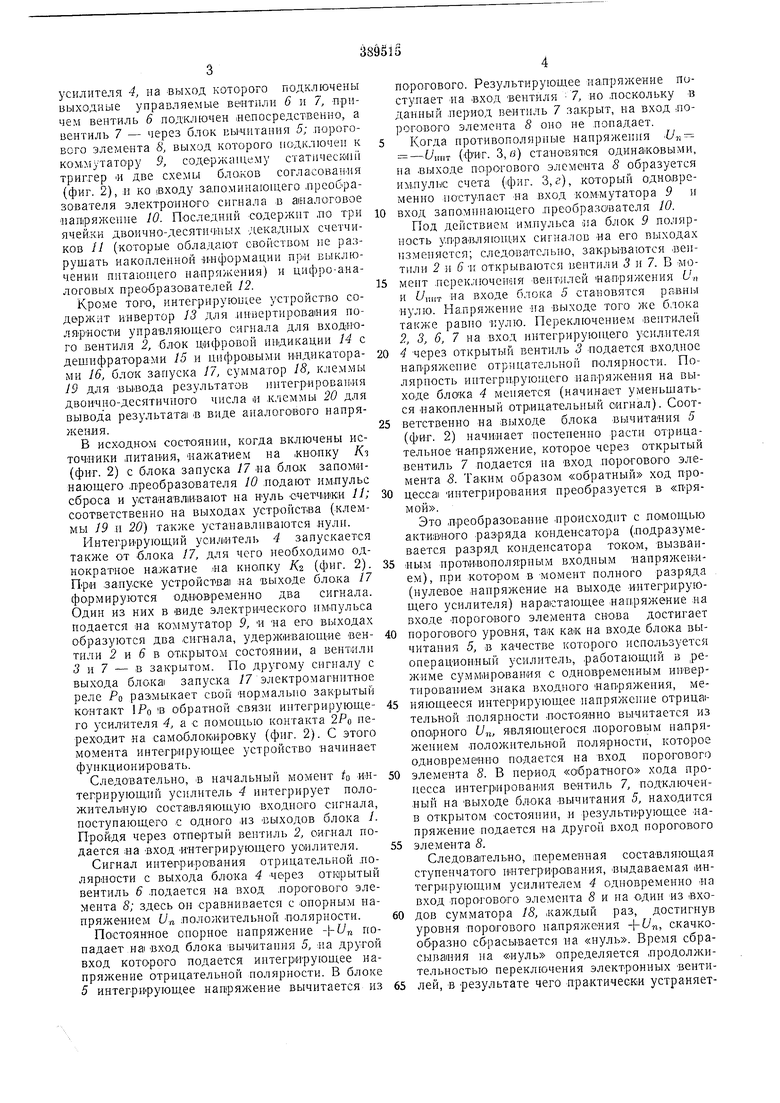

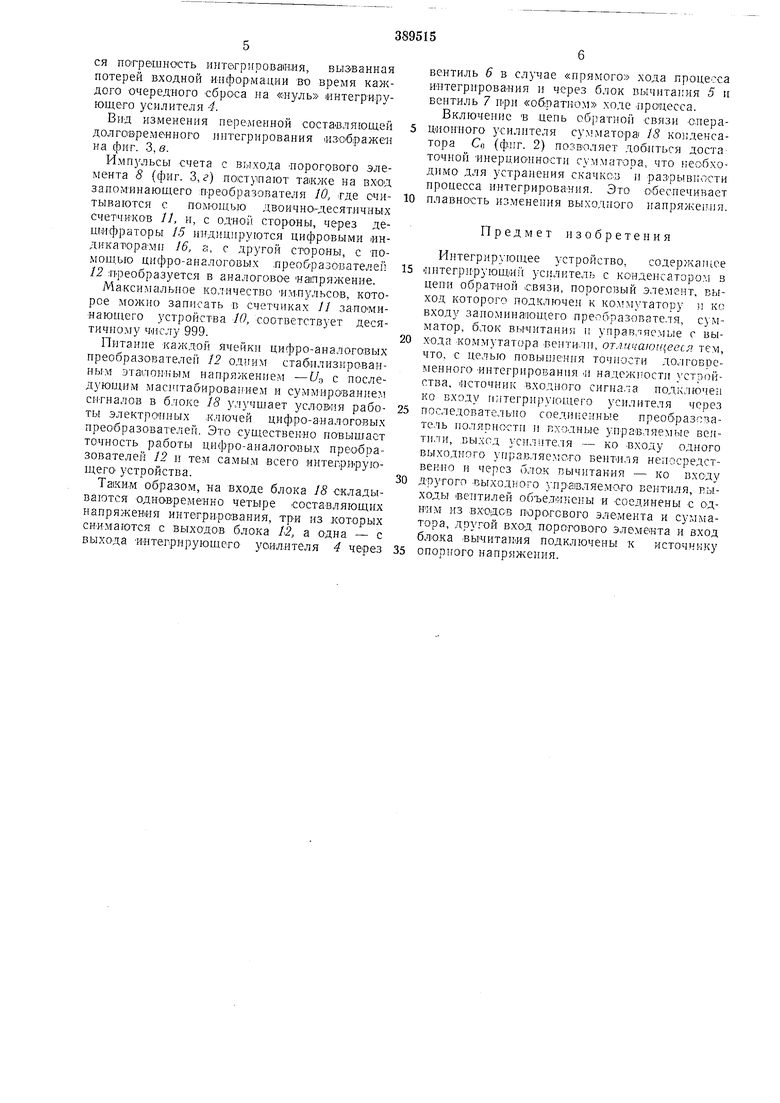

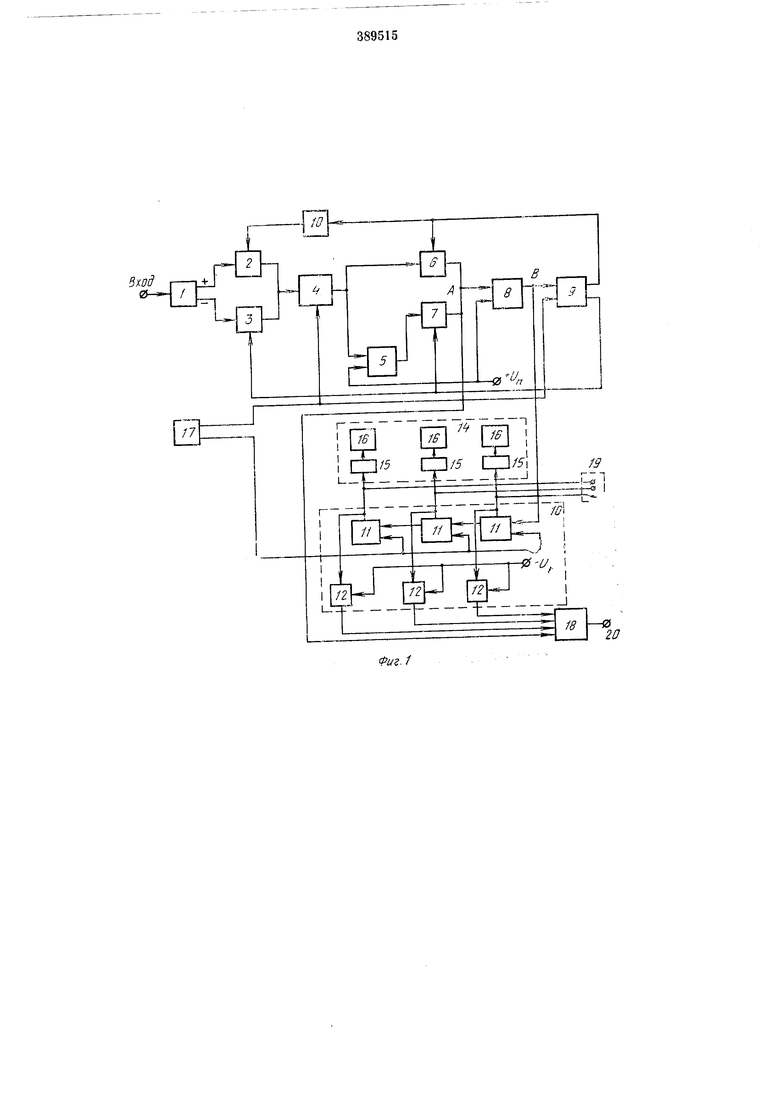

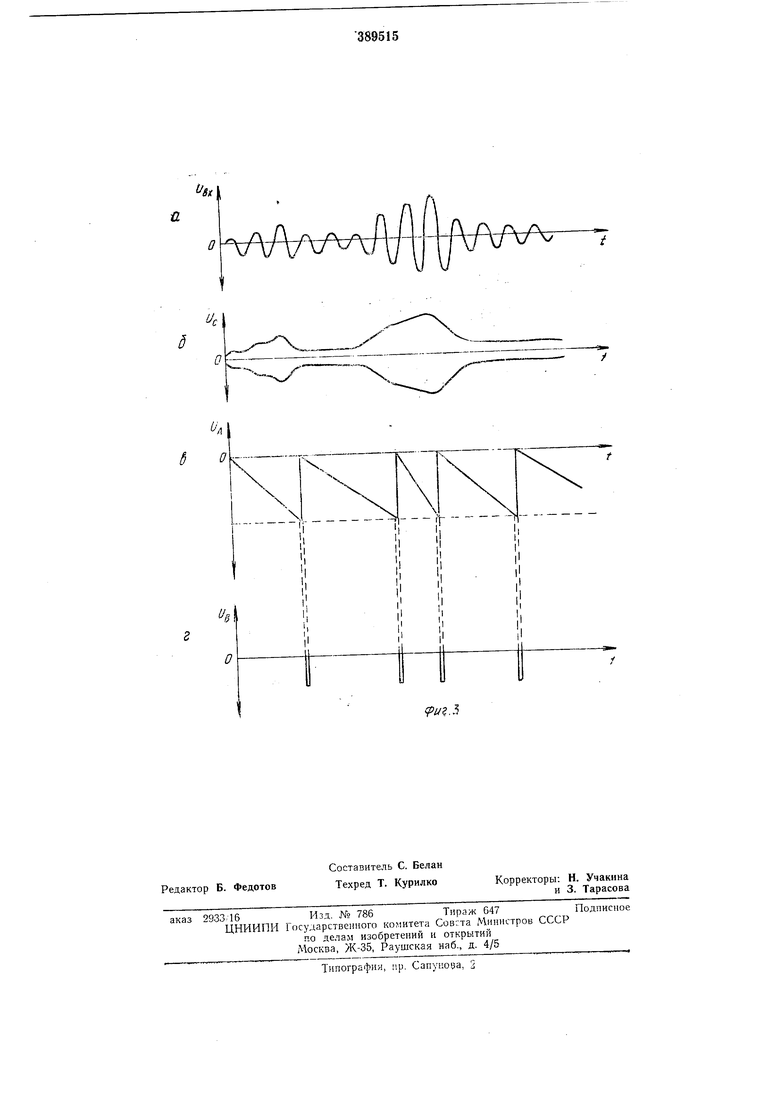

На фиг. 1 .представлена блок-схема .предлагаемого устройства; на фиг. 2 -- функц.иоиальная схе.ма; на фиг. 3 (а, б, в, г) - виды

5 сигналов в отдельны;х точках схемы (на фиг. 3,й нредставлен вид изменения входного сигнапа, на фиг. 3,6 - график изменения напряжения на выходе преобразователя, а на фиг. 3, в, г - 1В11ДЫ иЗ менения напряжения на

0 входе и выходе порогового устройства).

На фиг. 3,а ра-ссматривается случай синусоидального входного сигнала, являющийся наиболее характерным видом сигнала для многих датчико:в производительностей.

5 Предлагаемое интегрирующее устройство {фиг. 1) состоит из преобразователя полярности /, на одном из выходов которого удерживается всегда положительная полярность сигнаяа, а на другом - отрицательная; входных

0 управляемых вентилей 2 а 3, интегр1ирующего

усилителя 4, на выход которого подключены выходные управляемые вентпли 6 и 7, причем вентиль 6 подключен непосредственно, а вентиль 7 - через блок вычитания 5; .порогового элемента 8, выход которого юдключеи к ком,мутатОру 9, содержащему статичесК||111 триггер « две схемы бло,ков согласован ия (фиг. 2), и ко .входу за,поминаюи.1,его .преоб разователя электротшото сигнала в аналоговое нап ряжение 10. Последний содержит ло три ячейки двоично-десятич-ных декадных счетчиков и (которые обладают свойством не разрушать иакопленной ««формации прИ выключении питающего напряжения) и цифро-аналоговых преобразователей 12.

Кроме того, интегрирующее устройство содержит инвертор 13 для нивертироваиия полЯ.р«ост1И управляющего сигнала для входного вентиля 2, блок цифровой индикации 14 с дешифраторами 15 и цифровыми иидикаторами 16, блок запуска 17, сумматор 18, клеммы 19 для вывода результатов интегрирования двоично-десятичного числа « клеммы 20 для вывода результата в виде аналогового напряжения.

В исходном состоянии, когда включены источиики питавИЯ, «ажатием на .кнолку К(фиг. 2) с блока запуска 17 «а блок запоминающего преобразователя 10 лодают имлульс сброса и уста«авл1ивают на нуль счетчики 11; соответственно на выходах устройства (клеммы 19 ц 20) также устанавлнваются нули.

Интегрирующий усилитель 4 запускается также от блока 17, для чего необходимо однократное нажатие ла кнолку Kz (фиг. 2). При заиуске устройства: на выходе блока 17 формирзются однов-ременно два сигнала. Один из них в виде электрического имлульса подается «а коммутатор 9, л «а его выходах образуются два сигнала, удерживающие вентили 2 и 6 в открытом состоянии, а вентИли гЗ и 7 - в закрытом. По другому сигналу с выхода блока запуска /7 электромагнитное реле РО раз мыкает cBoii нормально закрытый контакт 1Ро в обратной «вязи интегрирующего усилителя 4, а с помощью контакта 2Ро нереходит на самоблокировку (фиг. 2). С этого момента интегрирующее устройство начинает функционировать.

Следовательно, iB начальный момент fo и«тегрирующнй усилитель 4 интегрирует положительную составляющую входного сигнала, поступающего с одного .из выходов блока /. Пройдя через отпертый вентиль 2, сигнал подается «а ВХОД Интегрирующего усилителя.

Сигнал интегрирования отрицательной лоляриости с выхода блока 4 через отырытый вентиль 6 лодается на вход лорогового элемента 8; здесь он сравнивается с олорным напряжением Vn лоложительиой -полярности.

Постоянное опорное напряжение попадает на вход блока вычитания 5, на другой вход которОГО подается интегрирующее напряжение отрицательной полярности. В блоке 5 интегрирующее напряжение вычитается из

порогового. Результирующее цалряжение поступает Иа вход вентиля - 7, но лоскольку в данный лериод вентиль 7 закрыт, на вход лороговОГО элемента 8 оно не Лэладает. Когда нротивополярные наиряжеиня .L/,,- (фиг. 3, fl) становятся одинаковыми, на выходе порогового элемента 8 образуется имлулыс счета (фиг. 3,г), который одновременно поступает на вход ком-мутатора 9 и

вход запомипающего лреобразователя 10.

Под действием имлульса «а блок 9 полярность улравляюнлих сигналов «а его выходах изменяется; следовательно, закрываются вентили 2 и 6 И открываются вентили 3 и 7. В адомент лереключения ве1ггПлей напряжения L,, и Unuf на входе блока 5 становятся нулю. Напряжение Иа выходе того же блока также равно нулю. Переключением вентилей 2, 3, 6, 7 на вход интегрирующего усилителя

4 Через открытый вентиль 3 подается входное налряжение отрицательной полярности. Полярность интегрирующего напряжения на выхОДе блока 4 меняется (начинаст уменьшаться «аколленный отрицательный сигнал). Соответственно на выходе блока вычитания 5 (фиг. 2) иачинает постепенно расти отрицательное Напряжение, которое через открытый вентиль 7 подается па вход лорогового элемента S. Таким образом «обратный ход ироцесса интегрирования преобразуется в «прямой.

Это лреобразование лроисходнт с помощью активного разряда конденсатора (лодразумевается разряд конденсатора токОМ, вызван:иым лротивололярным входным напряжением), при котором в Момент полного разряда (нулевое нанряжение на выходе интегрирующего усилителя) нара стающее напряжение на входе Порогового элемента снова достигает

норогового уровня, так как на входе блока вычитания 5, в качестве которого используется операционный усилитель, работающий в режиме суммирования с одновременным инвертированием знака входного налряжеиия, меняющееся интегрирующее напряжение отрица:тельной лолярности лостоянно вычитается из опорного Un, являющегося лороговым налряжением лоложительной полярностн, которое одновременно поДается на вход порОГового

элемента 8. В перИод «обратного хода процесса интегрирования вентиль 7, лодкл Оченный на выходе блока вычитания 5, находится в открытом состоянии, н результирующее иапряжение подается на другой вход порогового

элемента 8.

Следовательно, леременная составляющая ступенчатОГО интегрирования, выдаваемая интегрирующим усилителем 4 одновременно на вход порОГового элемента 8 и на один из входов сумматора 18, каждый раз, достигнув уровня лорогового налряжения -i-U, скачкообразно сбрасЫВается на «нуль. Время сбрасывания на «нуль определяется лродолжительностью переключения электронных вентилей, в результате чего практически устраняется погрешность интегрирования, вызванная потерей входной ипформа;ции во время каждого очередного сброса на «нуль интегрирующего усилителя 4.

Вид изменения переменной соста вляющей долгоеремеииого иитегрирования 1ИЗ0б;ражен на фиг. 3, в.

Импульсы счета с выхода Норогового элемента 8 (фиг. 3, г) поступают таиоке на вход запоминающего преобразователя 10, где считываются с помощью двоичнО-десятичных счетчиков //, н, с одной стороны, через дешифраторы /5 инд цируются цифровыми «ндккаторамп 16, а, с другой стороды, с помош.ью цифро-аналоговых лреобразосателей 12 преобразуется в аналоговое На1пряжение.

Максимальное количество им.пульсов, которое можно записать в счетчиках 11 запоминающего устройства 10, соответствует десятичному ч.ислу 999.

Питан е каждой ячейки цифро-аналоговых преобразователей 12 одним стабилизированным этапоННым напряжением -t/g с последующим мас1птабирова1 ием и суммированием сигналов в блоке 18 улучшает услов1 я работы электроиных ключей цифро-аналоговых преобразователей. Это существенно повышает точность работы цифро-аналоговых преобразователей 12 и тем самым всего интегрирующего устройства.

Таким образом, на входе блока 18 складываются одновременно четыре составляющих напряжения интегрирования, три из которых снимаются с выходов блока 12, а одна - с выхода интегрирующего усилителя 4 через

вентиль 6 в случае «прямого хода процесса интегрирования и через блок вычитания 5 и вентиль 7 при «обратном ходе .процесса. Включение в депь обратной связи олерационного усилителя сумматора /5 конденсатора Со (фиг. 2) позволяет добиться доста точной янерциОНностн сумматора, что нес-бходимо для устранения скачкси и разрывности процесса интегрироваНия. Это о-беснечивает

плавность изменения выходного нанряжепля.

Предмет изобретения

Интегрируюпдее устройство, содержащее

ИНтегрируюЩИЙ ус1 литель с конденсаторо.м в цени обратной связи, пороговый элемент, выход которого подключе к ко ;мутатору л ко входу заномииающего преобразователя, сумматор, блок вычитания и управляемые с выхода коммутатора веити.и, отличаюк ееся тем, что, с целью повышбННя точности долговре генного Интегрирования и надежности устройства, ИСТОЧНИК входного сигнала подключен ко входу гпгтегрнрующего усилителя через

последовательно соединенные преобразлпатель нолярностп н входные управляемые вентили, .выход }сил те.;1я - ко в.ходу одного выходного yrlpaвляe :o,гo вент-иля непосредствешю и через бло.к вычитания - ко входу

другого выходного унравляемого вентиля, выходы вентилей объедияены и соединены с одним из входов порогового элемента и сумматора, другой вход порогового элемента и вход блока вычитания подключены к источнику

опорього напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| I ВСГГСО'ЭЗНЛЯ I ДИСКРЕТНО-АНАЛОГОВЫЙ ИНТЕГРАТОР]|]ДТГ[{Т! Л :'Тк;^;Г v-^:^ | 1973 |

|

SU370614A1 |

| ИНТЕГРАТОР НАПРЯЖЕНИЯ | 1972 |

|

SU332466A1 |

| Дискретно-аналоговый интегратор | 1976 |

|

SU611218A1 |

| Интегратор | 1974 |

|

SU489120A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Способ управления группой импульсных преобразователей | 1981 |

|

SU1020958A1 |

| Устройство задержки | 1987 |

|

SU1497728A1 |

| Источник калиброванных напряжений | 1980 |

|

SU943672A1 |

| Система управления мощностью турбины | 1984 |

|

SU1227823A1 |

Авторы

Даты

1973-01-01—Публикация