(54) ИСТОЧНИК КАЛИБРОВАННЫХ НАПРЯЖЕНИЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник калиброванных напряжений | 1981 |

|

SU1029155A2 |

| Источник калиброванных напряжений | 1979 |

|

SU860025A2 |

| Источник калиброванных напряжений | 1980 |

|

SU877500A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Источник калиброванных напряжений | 1979 |

|

SU860021A2 |

| Источник калиброванных напряжений | 1980 |

|

SU907518A2 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

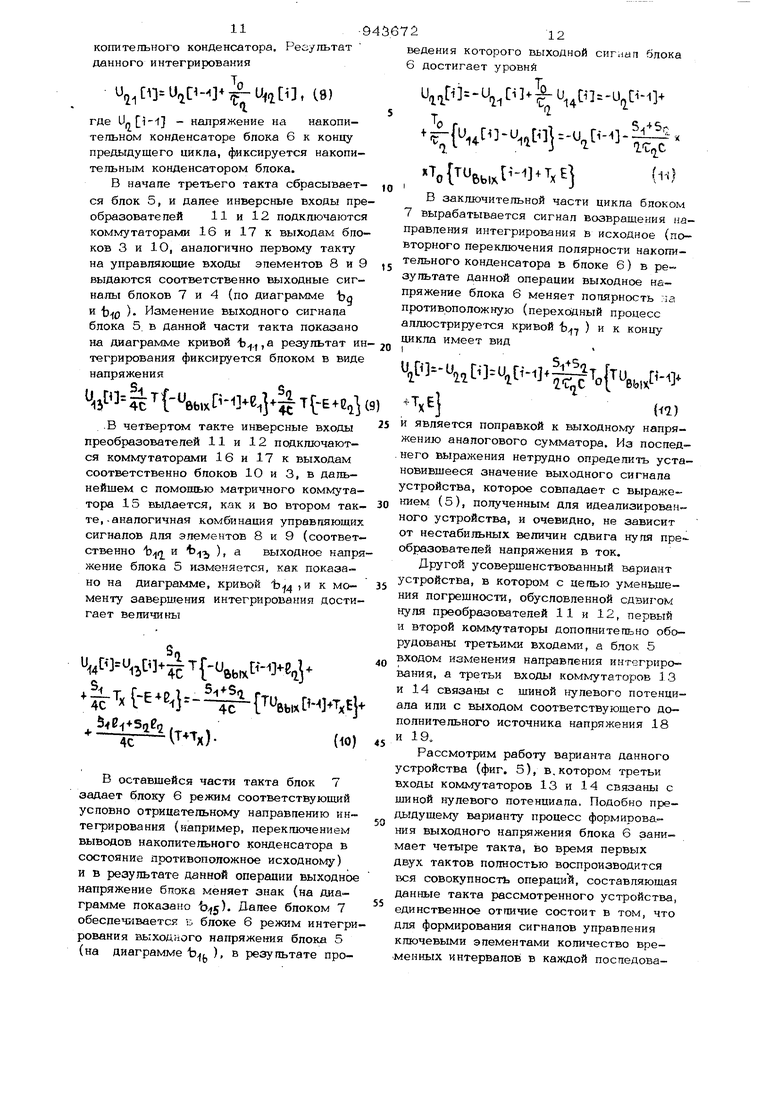

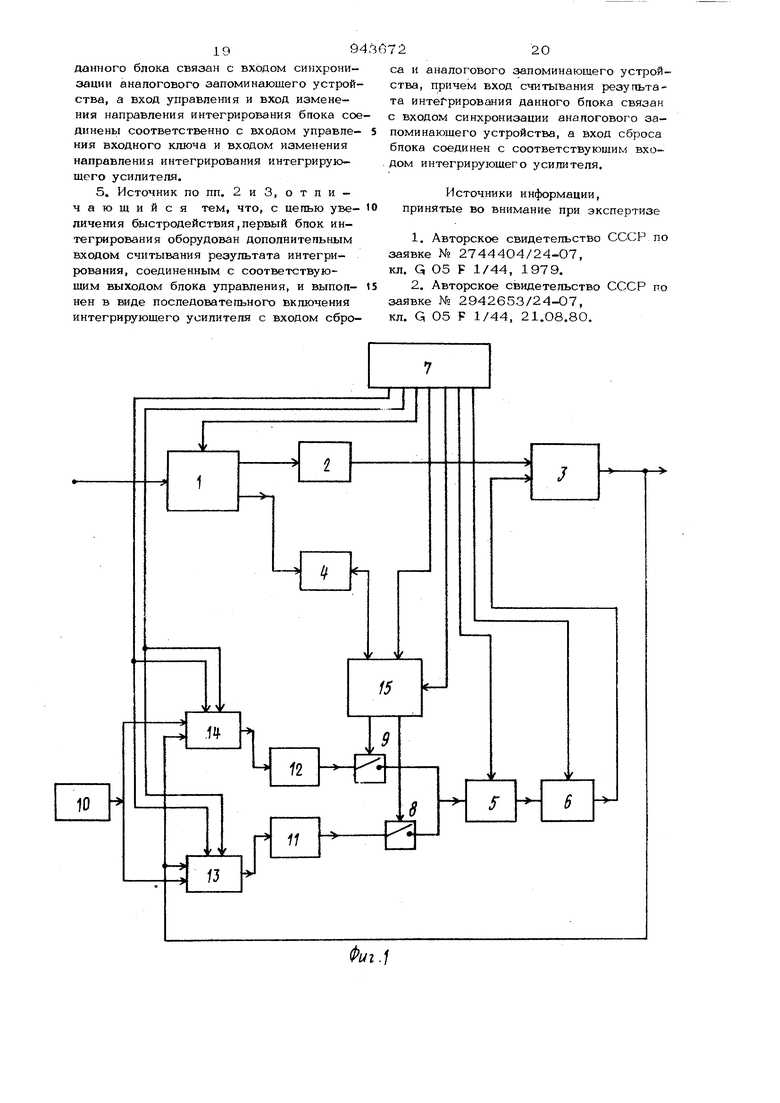

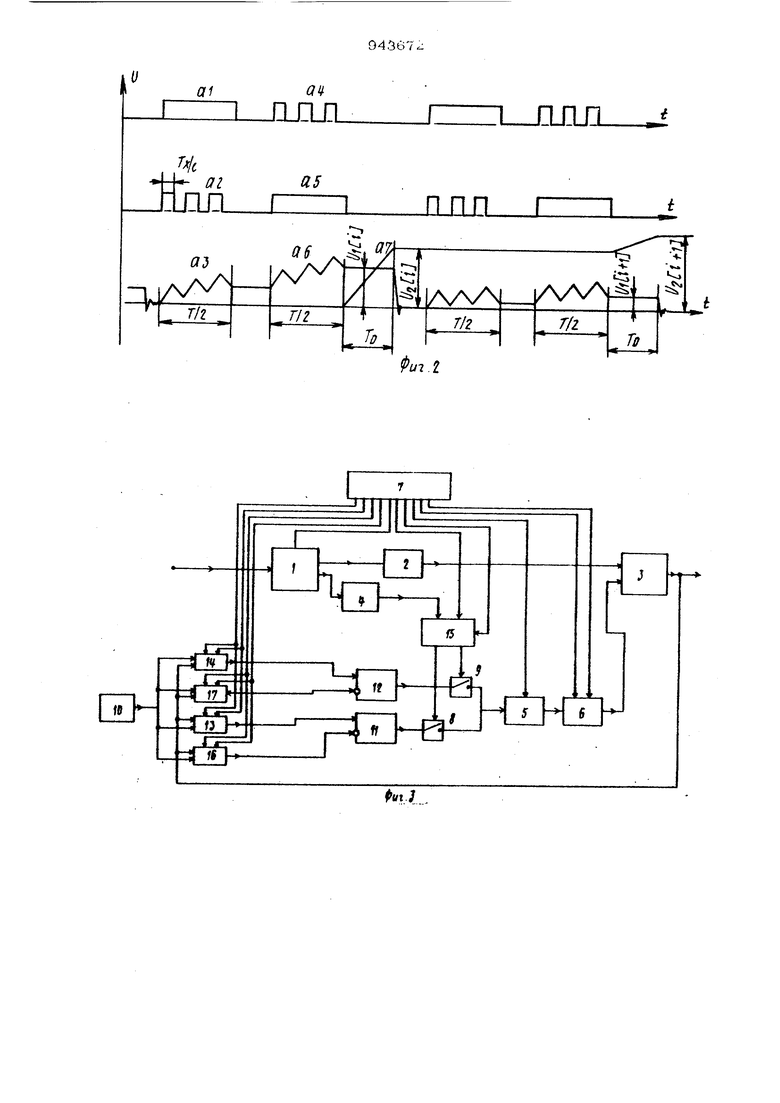

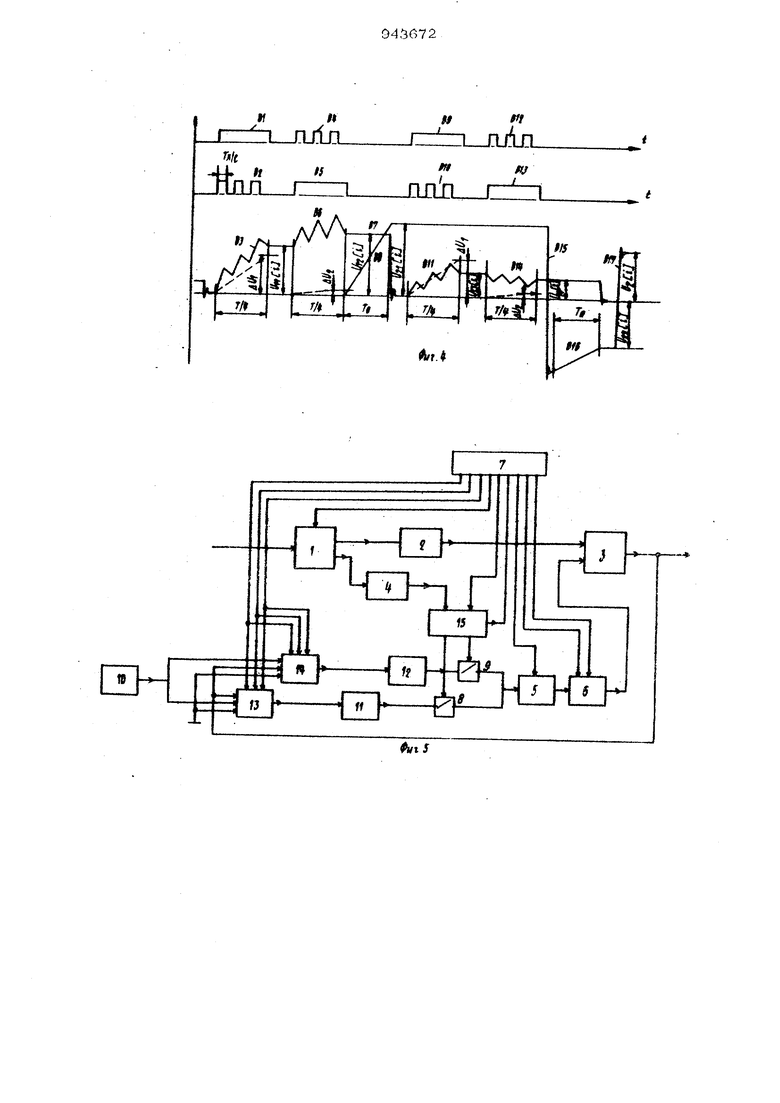

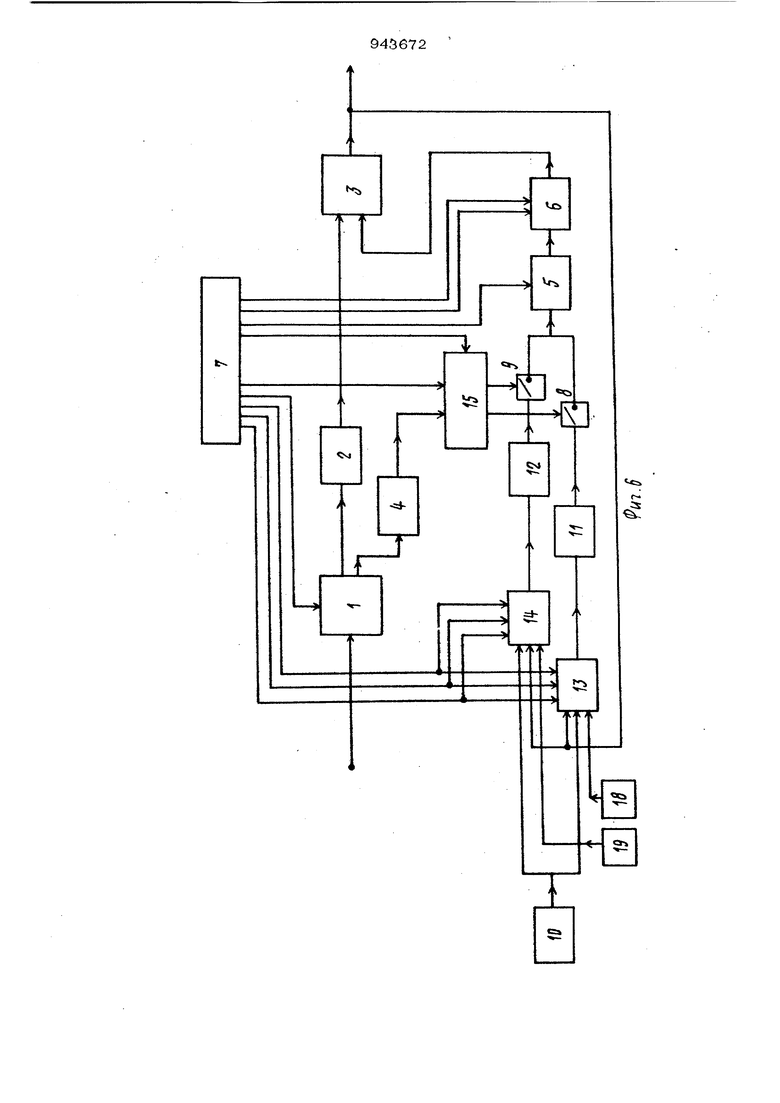

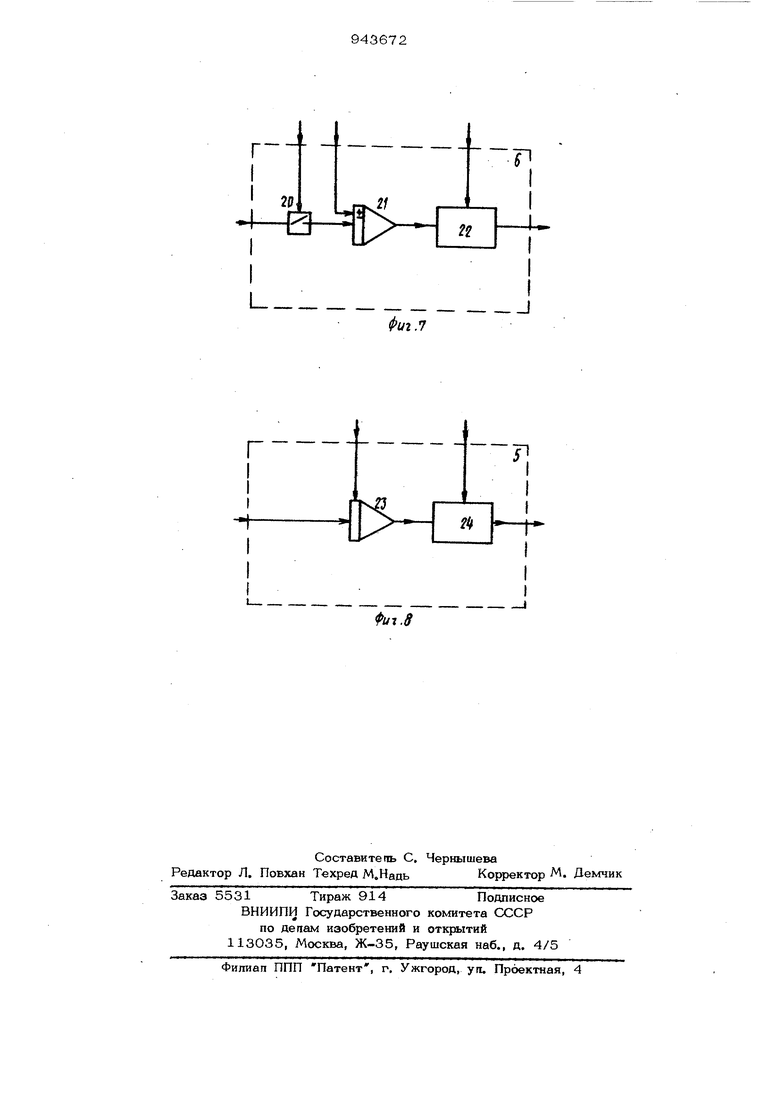

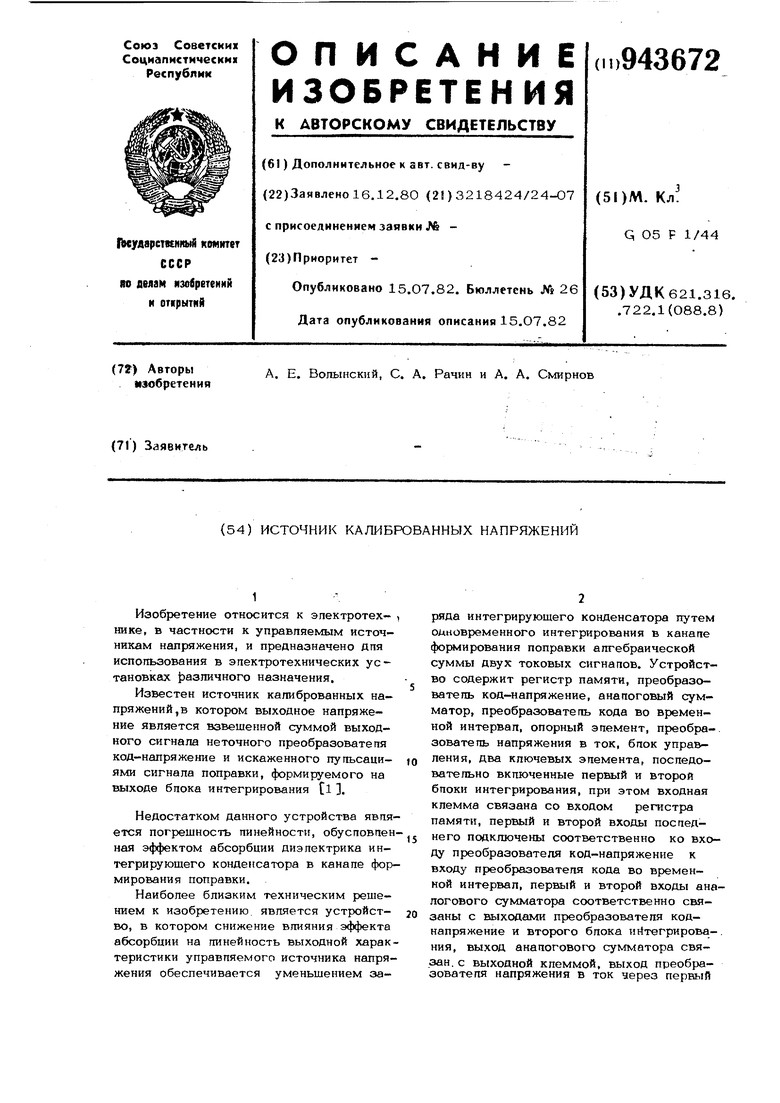

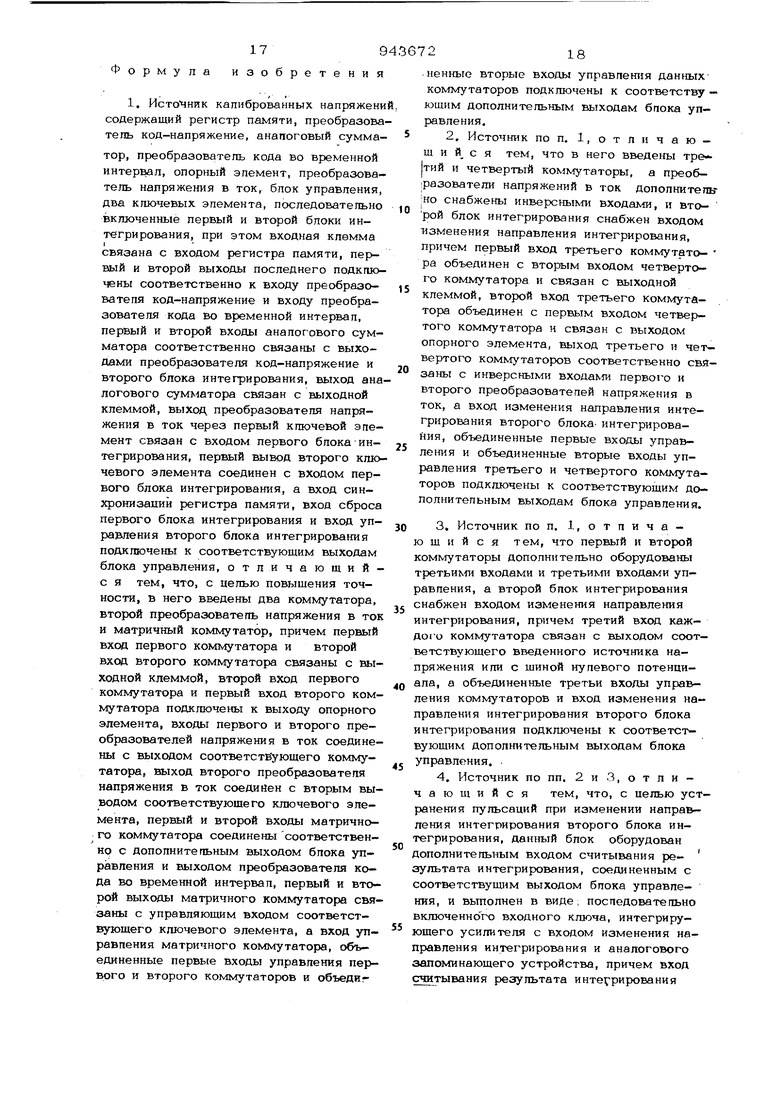

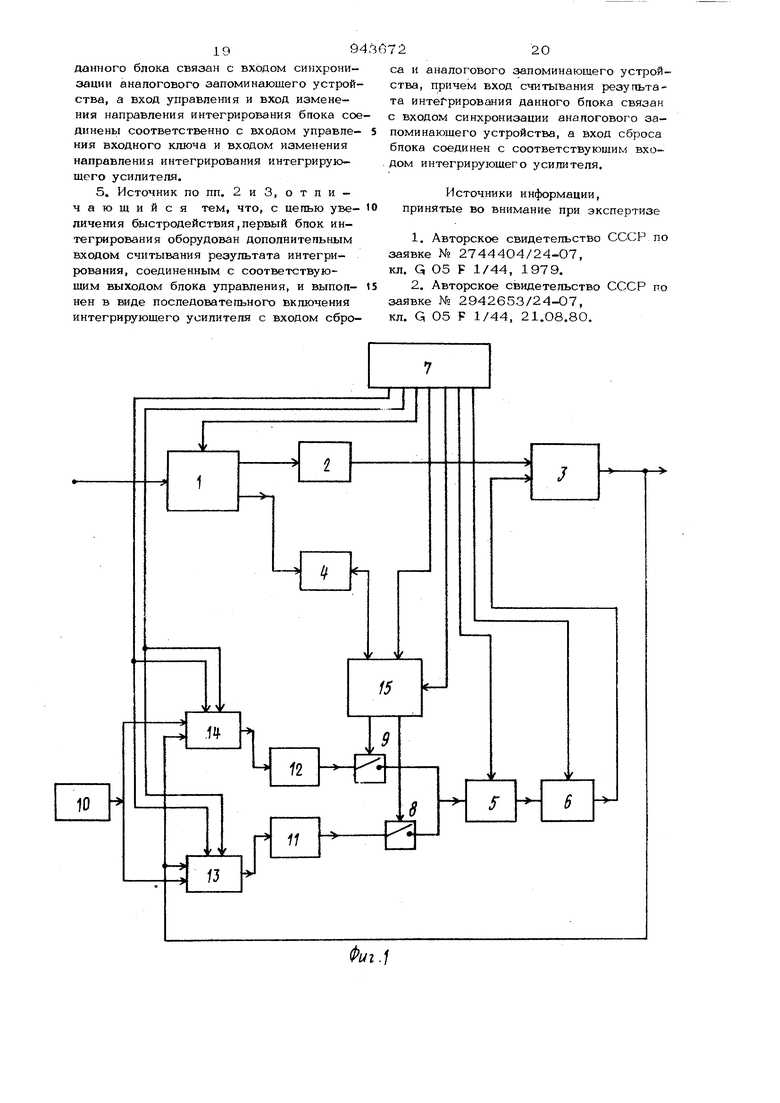

Изобретение относится к эпектротехнике, в частности к управляемым источникам напряжения, и предназначено для использования в электротехнических установках {различного назначения. Известен источник калиброванных напряжений,в котором выходное напряжение является взвешенной суммой выходного сигнала неточного преобразователя код-напряжение и искаженного пульсациями сигнала поправки, формируемого на выходе блока интегрирования fl . Недостатком данного устройства явля ется погрешность линейности, обусловлен ная эффектом абсорбции диэлектрика интегрирующего конденсатора в канале фор мирования поправки. Наиболее близким техническим решением к изобретению является устройство, в котором снижение влияния эффекта абсорбции на линейность выходной харак теристики управляемого источника напря жения обеспечивается уменьшением заряда интегрирующего конденсатора путем одновременного интегрирования в канале формирования поправки алгебраической суммы двух токовых сигналов. Устройство содержит регистр памяти, преобразователь код-напряжение, аналоговый сумматор, преобразователь кода во временной интервал, опорный элемент, преобразователь напряжения в ток, блок управления, два ключевых элемента, последовательно включенные первый и второй блоки интегрирования, при этом входная клемма связана со входом регистра памяти, первый и второй входы поспеднего подкгаочены соответственно ко входу преобразователя код-напряжение к входу преобразователя кода во временной интервал, первый и второй входы аналогового сумматора соответственно связаны с выхсадами преобразователя коднапряжение и второго блока ийтегрирова-. ния, выход аналогового сумматора свя.зан. с выходной клеммой, выход преобразователя напряжения в ток через первый ключевой элемент связан со входом первог-о баска интегрирования, первый вывод второго кшочевого элемента соединен со входом первого блока интегрирования, а вход синхронизации регистра па мяти, вход сброса первого блока интегри рования и вход управления второго бпока интегрирования- подключены к соответствующим выходам блока управления 2. Недостатком этого устройства является невысокая точность. Целью- изобретения- является повышение точности. Поставленная цепь достигается тем, что источник калиброванных напряжений, содержащий регистр памяти, преобразова тель код-напряжет1е, аналоговый сумматор, преобразователь кода во временной интервал, опорный элемент, преобразователь напряжения в ток, блок управления два ключевых элемента, последовательно включенные первый и второй блоки интегрирования, в котором входная клемма связана со входом регистра памяти, первый и второй выходы последнего подключены соответственно ко входу преобразователя код-напряжение и входу преобразователя кода во временной интервап, первый и второй входы аналогового сумматора соотгетственно связаны с выходами преобразователя код-напряжение и второго блока интегрирования, выход ана логового сумматора связан с выходной клеммой, выход преобразователя напряжения в ток через первый ключевой элемент связан со входом первого блока интегрирования, первый вывод второго клю чевого элемента соединен со входом первого блока интегрирования, а вход синхро низации регистра памяти, вход сброса первого блока интегрирования и вход управления второго бпока интегрирования подключены к соответствующим выходам бпока управления, введены два коммутатора, второй преобразователь напряжения в ток и матричный коммутатор, причем первый вход первого коммутатора и второй вход второго коммутатора связань с выходом устройства, второй вход перво го коммутатора и первый вход второго коммутатора подключены к выходу опорного элемента, входы первого и второго преобразователей напряжения в ток соеди нены с выходом соответствующего комму татора, выход второго преобразователя напряжеш1Я в ток соединен со вторым вы водом соответствующего ключевого элемента, первый и второй входы матричноГО коммутатора соединены соответственно с дополни те ль ним выходом блока управления и выходом преобразователя кода во временной интервал, первый и второй выходы матричного коммутатора связаны с управляющим входом соответствующего ключевого элемента, а вход управления матричного коммутатора, объединенные первые входы управления первого и Второго коммутаторов и объединенные вторые входы управления данных коммутаторов подключены к соответствующим дополнительным выходам блока управления. Дальнейшее повышение точности управляемого источника напряжений обеспечивается уменьшением составляющей по грещности устройства, обусловленной сдвигом нуля преобразователя напряжения в ток. Поставленная цель достигается также тем, что в источник калиброванных напряжений дополнительно введены третий и четвертый комк утаторы, преобразователи напряжения в ток дополнительно оборудованы инверсными входами, а второй блок интегрирования снабжен входом изменения направления интегрирования, причем первый вход третьего комKf/татора объединен со вторым входом четвертого коммутатора и связан с выходной клеммой, второй вход третьего KOMN-iyTaTopa объединен с первым входом четвертого коммутатора и связан с выходом блока опорного напряжения, выхо-ды третьего и четвертого комл-гутаторов. соответственно связаны с инверснъми входами первого и второго преобразователей напряжения в ток, а вход измене- ния нш:1равления интегрирования второго блока интегрирования, объединенные первые входы управления и объединенные вторые входы управления третьего и четвертого коммутаторов подкгаочены к соответствующим Дополнительным выходам бпока управления. Повышение точности также может производиться За счет введения дополнительных тактов интегрирования выходных сигналов преобразователей напряжения в ток и вычитания результатов интегрирования из результата интегрирования в рабочих тактах. Поставленная цель достигается и тем, что в источнике калиброванных напряжений первый и второй коммутаторы дополнительно оборудованы третьими входами третьими входами управления, а вто- рой блок интегрирования снабжен входом изменения направпення интегрирования, причем третий вход каждого коммутатора связа с выходом соответствующего дополнительного источника напряжения или с шиной нулевого потенциала, а объединенные третьи входы управления коммутаторов и вход изменения направпения интегрирования второго блока интегрирования подключены к соответствующим дополнительным выходам блока управления. Дальнейшее повышение точности источ ника производится за счет устранения пульсаций на выходе второго блока интегрирювания при изменении направления интегрирования данного блока. Это достигается тем, что в источнике калиброванных напряжений второй блок интегрирования оборудован дополнительным входом считывания результата интегрирования, соединенным с соответствующим выходом блока управпет1я, и вы полнен в виде последовательного включе- ния входного ключа, интегрирующего уси лителя со входом изменения направления интегрирования и аналогового запоминаю щего устройства, причем вход считывания результата интегрирования данного блока связан со входом синхронизации аналогового запоминающего устройства, а вход управления и вход изменения направления интегрирования блока соединены соответственно со входом управления входного ключа и входом изменения направления интегрирования интегрирующего усилителя. Повьпление быстродействия устройства обеспечивается путем сокращения длител ности цикла за счет частичного совмеще ния во времени операций, реализуемых первым и вторым блоками интегрировани Это Достигается тем, что в управоя- емом источнике напряжений первый блок интегрирования оборудован дополнительным входом считывания результата интегрирования, соединенным с соответствующим выходом блока управления, и вы полнен в виде последовательного включения интегрирующего усилителя со входом сброса и аналогового запоминающего уст ройства, причем вход считывания результата интегрирования данного блока связан со входом синхронизации аналогового запоминающего устройства, а вход сброса блока соединен с соответствующим входом интегрирующего усилителя. На фиг. 1 и 2 приведены соответственно структурная схема устройства,поясняющие его работу временные диаграммы; на фиг. 3 и 4 - структурная схема и временные диаграммы устройства, в котором устранена погрешность, обусловленная сдвигами нупя преобразователей напряжения в ток; на фиг. 5 и 6 - возможные выполнения структурной схемы устройства, в котором повышение точности обеспечивается за счет дополнительных тактов интегрирования; на фиг. 7 - вариант выполнения второго блока интегрирования, позволящий устранить пульсации на выходе устройства при изменении направления интегрирования; на фиг. 8 - вариант выполнения первого блока интегрирования, позвопящий повысить быст родействпе управпяемого источника напряжений. Управляемый источник напряжений содержит регистр памяти 1, преобразователь код-напряжение 2, аналоговый сумматор 3, преобразователь кода во временной интервал 4, первый и второй блоки интегрирования 5 и 6 соответственно, блок управления 7, первый и .второй ключевые элеманты 8 и 9 соответственно, опорный элемент Ю, первый и второй преобразователи напряжения в ток 1J. и 12 соответственно, первый и второй коммутаторы 13 и 14 соответственно и матричный коммутатор 15. Вариант устройства, структурная схема которого приведена на фиг. 3, дополнительно содержит третий и четвертый коммутаторы 16 и 17 соответственно. Другой вариант устройства, структурная схема которого показана на фиг. 6, дополнительно содержит первый и второй дополнительные источники напряжения 18 и 19 соответственно. Возможным вариантом выполнения блока 6 является приведенное на фиг. 7 совместное включение входного ключа 20, интегрир)юшего усилителя 21 со входом изменения направления интегрирования и аналогового запоминающего устройства -22, Возможным вариантом выполнения блока 5 является приведенное на фиг, 8 последовательное включение интегрирующего усилителя 23 со входом сброса и анапогового запоминающего устройс-г ва 24, Устройство работает следующим образом. По команде блока 7 входной код переписывается в регистр 1, при этом на выходе преобразователя 2 устанав mi ВОРтся пропорционапьное даннокГу ходу напряжение Е, Выходное напряжение сумматора 3 в произвольный момент времени определяется выражением ( где U(, (t) - напряжение на выходе блока 6; д) коэффициенты передачи сум матора 3 по соответствующим входам. Процесс установпения выходного напряжения устройства носит итерационный характер и осуществляется в течение п циклов, а определение блоком 5 в каждом цикле алгебраической суммы результатов интегрирования опорного и входного сигналов занимает два такта, В начале т -го цикла.бтюк управления 7 производит сброс блока 5. Далее в начале пер вого такта данного цикла блок 7 через коммутатор 13 подключает вход преобра-т зователя 11 к выходу устройства ji через коммутатор 14 - вход преобразователя 12 к выходу блока 1О. На выходах пре образователей 11 и 12 устанавливаются токи, пропорнионапьные выходному и опорному Е напряжениям: , V. где в и S(2 - крутизна преобразователя 11 и 12 соответственно, причем Зл гЗ(1+сЛ), «1. По окончании интервала, достаточного для завершения переходных процессов в преобразователях. 11 и 12 блоком 7, выдается сигнал управления матричному коммутатору 15, по которому последний падкпючает управляющий .вход элемента 8 к дополнительному выходу блока 7, а управляюндай вход клю чевого элемента 9 - к выходу преобразователя, в результате данных псадкпючений элемент 8 замыкается на время Т/1, замкнутое состояние элемента 8 в первом такте условно показано на на фиг. 2,а , а элемент 9 периодически включается с помощью управляющей последовательности из /1 равномерно рас ставленных временных интервалов длительности Tjf/ (йа диаграмме а ). Данная последовательность интервалов вырабатывается преобразователем 4 и предназначена для широтно-имйульсной модуляции выходного тока преобразователя 11. Форми1)уемые таким путем импульсы тока по ступают на вход блока 5 и одновременно с ними на вход блока в течение интервала длитепьности Т/О. подается выхсдной ток преобразователя 12. Аагебраическая сумма токов интегрируется блоком 5, а результат интегрирования в конце первого такта фиксируется в данном бпоке (процесс интегрирования показан ломакой В начале второго такта 7 с помоцсью коммутатора 13 обеспечивается отклонение входа преобразователя 11 от выхода устройства и подключение к выходу блока 1О, аналогично коммутатором 14 отключается вход преобразователя 12 от выхода блока 1О и подключается к выходу управляемого источника напряжений. На выходах преобразователей 11 и 12 устанавливаются соответствующие входные сигнапы тока )ri ll- а бьт З а по окончании переходных процессов в преобразователях блок 7 с помощью матричного коммутатора 15 подкшочает выход преобразователя 4 к управляющему уходу элемента 9. В результате данных операций элемент 8 периодически включается последовательностью управтшющих временных интервалов д)В1тельности Т,/7 (на диаграмме данная последовательность d ), а элемент 9 замыкается на время ТЛ. (на диаграмме Ос ). Аналогично первому такту алгебраическая сумма постоянного и импульсного токов преобразователей 12 и 11 интегрируется блоком 5 (процесс интегрирования показан ломаной ) и суммируется в бпоке с результатом первого такта, Выходное напряжение блока 5 по окончании второго такта ..-«4} ){вы Е -1 1 ЕТ,, (I, где С - емкость интегрирующего кондененсатора блока 5. Последующая работа устройства аналогична работе известного устройства, выходное напряжение блока 5 интегрируется в течении временного интервала длительности Т0 блоком 6 (процесс интегрирования показан кривой O-j ), выполняющим функции накапливающего сумматора поправок, а выходной сигнал блока 6 воспринимается сумматором 3 в качестве поправки данного цикла. К концу цикла выходное напряжение бпока 6 достигает величины ,r,-,(3) где un - постоянная времени интегрирования бпока 6, а на выходе сумматора 3 в соответствии с (1) формируется вы ходной сигнал устройства V«t J i iViti- eb,.°i s,(){V«f- «i .m lV%-l исходное значение сигнала на выходе сумматора 3. Аналогично известному потребуем вы полнения условия I И тогда выходное напряжение устройства сходится в течение нескольких циклов к установившемуся значению «-Е I в данном управляемом источннке напряжений благодаря одновременному интегрированию алгебраической суммы дву токовых сигналов, представляющих опорное и выходное напряжения источника, обеспечивается уменьшение заряда интегрирующего конденсатора первого блока интегрирования, и следовательно, аналогично известному снижается влияние эффекта абсорбции на линейность выходной характеристики устройства в целом. Однако в отличие от известного выходное напряжение данного устройства (5) не зависит от крутизны преобразователей напряжения в ток и определяется лишь опорным сигналом (напряжени ем) и отношением длительности временных интервалов. Предлагается вариант управляемого источника напряжения, структурная схем которого дана на фиг. 3. В каждом цикле данного устройства процесс интегриро вания блоком 5 алгебраической суммы токовых сигналов, соответствующих выходному и опорному напряжениям, занимает четыре такта. Перед началом первого такта сбрасывается блок 5,и далее прямые входы преобразователей 11 и 12 через коммутаторы 13 и 14 подключаются к выходам блоков 3 и 10 со ответственно. В дальнейшем в течение первого такта матричным коммутатором 15 обеспечиватся одновременная выдача на управляющий вход элемента 8 непрерывного интервала длительности Т/4 (кривая Ъ) и на управляющий вход элемента 9 последовательности из Р/4- интервалов длительности Т.|(/В преобразователя 4 (на диаграмме Ь ). Алгебраическая сумма сигналов, формируемых из выходных токов преобразователей 11 и 12 элементами 8 и 9, интегрируется блоком 5 (изменение выходного сигнала блока 5 показано ti ) и фиксируется блоком. РЗыходное напряжение блока 5 при этом J4 7rK. где Е-1 и бл - приведенные ко входам преобразователей 11 и 12 напряжения сдвига нуля. В начале второго такта прямые входы преобразователей 11 и 12 подключай.тся комл утаторами 13 и 14 к выходам соответственно блоков 1О и 3 матричных коммутаторов 15, обеспечивается выдача п ос Ледова те ьн ости интервалов преобразователя 4 на управляющий вход элемента 8 (кривая Ъ ), а непрерывного интервала блока 7 на управляющий вход элемента 9 (на диаграмме Результат интегрирования блоком 5 алгебраической суммы непрерывного и импульсного токовых сигналов суммируется в блоке с величиной U-)/, Ci и к концу второго такта достигает величины tV.,w.|T{%J- 4} V. ,j i fTU6b« iH E + . Vl.(,..,,„ (отклик блока 5 на алгебраическую сумму токовых сигналов во втором такте показан на диаграмме кривой bf, ), В течение интервала длительности Т,, выходное напряжение блока 5 Until остается неизменным (кривая b-j) и интегрируется блоком 6, имеющим постоянную времени f ij (npcMiecc интегрирования показан кривой Ъд ). При этом включено условно положительное направление интегрирования, обеспечиваемое, например, соответствующим включением выводов на11-9копительного конденсатора. Р езультат данного интегрирования , С9) где - напряжение на накопительном конденсаторе блока 6 к концу предыдущего цикла, фиксируется накопительным конденсатором блока. В начале третьего такта сбрасывается блок 5, и дапее инверсные входы пре образоватепей 11 и 12 подключаются коммутаторами 16 и 17 к выходам блоков 3 и Ю, аналогично первому такту на управляющие входы элементов 8 и 9 выдаются соответственно выходные сигналы блоков 7 и 4 (по диаграмме Ъд и ) Изменение выходного сигнала блока 5. в данной части такта показано на диаграмме кривой -Ь.,, а результат ин тегрирования фиксируется блоком в виде напряжения Цз -4 {- выхГ- 4 т(-Е.е, .в четвертом такте инверсные входы преобразователей 11 и 12 подключаются коммутаторами 16 и 17 к выходам соответственно блоков 1О и 3, в дальнейшем с помощью матричного коммутато Тз в щаетсяУ кГк7 такте,-аналогичная комбинация управляющих сигналов для элементов 8 и 9 (соответственно fi и ), а выходное напря жение блока 5 изменяется, как показано на диаграмме, кривой Ъ менту завершения интегрирования достигает величинь «C V 4| Uвьnct- Ц х(,}.-(ти,,,сн№ .,.,,,. В оставшейся части такта блок 7 задает блоку 6 режим соответствующий условно отрицательному направлению интегрирования (например, переключением выводов накопительного конденсатора в состояние противоположное исходному) и в результате данной операаии выходное напряжение бпока меняет знак (на диа-грамме показано , Далее блоком 7 обеспечивается г; блоке 6 режим интегри рования выходного напряжения бпока 5 (на диаграмме Ъ, ), в результате про2ведения которого выходной сигнап блока 6 достигает уровни ,,. {и„СО-и,,,,. Т(,(«) В заключительной части цикла бпоком 7 вырабатывается сигнал возвращения направления интегрирования в исходное (повторного переключения полярности накопиlf l°2°,° ® Р зультате данной операции выходное напряжение блока 6 меняет полярность rsa противоположную (перехсМный процесс алдюстрируется кривой Ъ концу цикла имеет вид и является поправкой к выходному напряжению аналогового сумматора. Из последнего выражения нетрудно определить установившееся значение выходного сигнала устройства, которое совпадает с выраже™ем (5), полученным для идеализированнего устройства, и очевидно, не зависит от нестабильных величин сдвига нуля преобразователей напряжения в ток. Другой усовершенствованный вариант устройства, в котором с цепью уменьшения погрешности, обусловленной сдвигом нуля преобразователей 11 и 12, первый и второй коммутаторы дополнительно оборудованы третьими входами, а блок 5 входом изменения направпения интегрирования, а третьи входы коммутаторов 13 и 14 связаны с шиной нулевого потенциала или с выходом соответствующего дополнительного источника напряжения 18 и 19 Рассмотрим работу варианта данного устройства (фиг. 5), в.котором третьи входы коммутаторов 13 и 14 связаны с шиной нулевого потенциала. Подобно предыдущему варианту процесс формирования выходного напряжения блока 6 занимает четыре такта, во время первых двух тактов полностью воспроизводится вся совокупность операций, составляющая данные такта рассмотренного устройства, единственное отличие состоит в том, что для формирования сигналов управления ключевыми элементами количество временных интервалов в каждой поспедовательности и длительность одиночного интервала увеличены по сравненияю с данным устройством вдвое. В результате к концу второго такта на выходе блока 5 формируется напряжение .b«tH.T,E5 + , . ()j (13J а выходное напряжение блока 6 после ин тегрирования данной величины приобретает вид аналогичный (8). Перед началом третьего такта блоком 7 производится сброс блока 5 и подключение с помощью коммутаторов 13 и 14 входов преобразователей 11 и 12 к шине нулевого потенциала на всю оставшуюся часть цикла Далее, аналогично первому такту, на управляющий вход элемента 8 блоком 7 через коммутатор 15 вьщается одиночный интервал длительности Т/1, а на управляющий вход элемента 9 - последова тельность преобразователя 4, содержащая Р/(1 интервалов дли тельности УС. На выходе блока 5 при этом формируется напряжение .т ||е„т,, И) в четвертом такте блоком 7, как и во втором такте, обеспечивается выдача одиночного управляющего интервала длительности на управляющий вход элемента 9, а на управляющий вход элемен та 8 - указанной ранее последовательно ти преобразователя 4. В результате интегрирования входных сигналов блока 5 напряжение на выходе последнего имеет вид u,4W Vf t|-eiT.,T,. .l(T.T,, „s) В оставшейся части четвертого такта на вход изменения направления интегрирования блока 6 поступает команда бло ка 7, по которой, как и в рассмотренно ранее устройстве, выходное напряжение блока 6 меняет полярность на против положную, далее на вход управления бло ка 6 поступает управляющий интервал длительности TQ , в течение которого вы ходное напряжение блока 5 интегрирует f rr 4t/Q MLlTVTiT nTJf я блоком 6, и результат интегрирования меет вид аналогичный (11). ,1.,.-и (в оставшейся части цикла блоком 7 вырабатывается сигнал повторного измеения направления интегрирования (полярности накопительного конденсатора) блоа 6, в результате которого,иыходнай сигнал блока меняет знак и к концу цикла принимает вид (12). Таким образом, к концу цикла выходой сигнал блока 6, как и в рассмотреном ранее управляемом источнике напряений, не зависит от нестабильных сдвигов уля преобразователей 11 и 12, однако по равнению с предыдущим вариантом даное устройство обеспечивает коррекцию анной составляющей погрешности управ- яемого источника напряжения более протым средством. Рассмотрим работу другого варианта данного устройства (фиг. 6), в котором третьи входы ксмимутаторов 13 и 14 связаны с выходом соответствующего источника напряжения 18 и 19. Как и в рассмотренном предыдущем варианте, формирование выходного напряжения блока 6 занимает в данном устройстве четыре такта, во врюмя которых вырабятывается точно такая же как и в указанном варианте совокупность управляющих сигналов. Специфика данного устройства в том, что в третьем и четвертом тактах в блоке 5 одновременно с интегрированием сдвига нуля преобразователей 11 и 12 производится интегрнро-. вание соответствующей дополнительной составляющей, пропорциональной выходному напряжению источников 18 и 19 и предназначенной для компенсации ошибки, обусловленной неидеальным формированием импульсов тока элементами 8 и 9. Используя прежние обозначения, получают, аналогично предыдущему варианту, выражение для выходного сигнала блока 5 к концу второго такта ,,,Ь--ф9. ..JL (T+dT«j)fE К, L. Ъ. 9 , ,en (Т4Т,). ,)Tx/S()ATxa IC где т и TX - ошибки формирования прямо угольных импульсов, обусповпенные инерь циопностью элементов 8 и 9 соответственно. Обозначив выходное напряжение источников 18 и 19, получают аналогичные выражения для третьего иг четвертого тактов S. г. . , S ,.e,y(,)e,. ) , . т г (T-T,).,u,.,f Задуа 5,йтх,е-, ас Подставив (17) и (19) в (16), получают вьгражение для выходного сигнала 9 пока 6 к концу цикпа и Р --и 1-н -|{и ПЗ-Ц4И - Т4ти8,,5 Поскольку погрешности формирования uTjf постоянны и характеризуют свойства конкретного ключевого элемента, то их влияние может быть скомпенсировано предварительной регулировкой выходного напряжения соответствующего источника 18 и 19, т. е. Обеспечив (21), получают, что выходное напряжение блока 6 к концу цикла, а следовательно, и выходное напряжение устройства не зависят от неидеального формирования импульсов тока ключевыми элементами и от величин сдвига нуля преобразователей 11 и 12, что выгодно отличает данный вариант от рассмотренных ранее. Для устранения пульсаций, вызванных изменением направления интегрирования второго блока интегрирования, последний 7210 снабжен входом считывания результата интегриров-ания,выполнен В виде совместного включения входного ключа 2О, интегрирующего усилителя 21 и аналогового запоминающего устройства 22. Указанное выполнение блока 6 обеспечивает интегрирование и суммирование результатов отдельных тактов с помощью элементов 20 и 21, а выдачу результата суммирования в конце цикла - посредством переписи выходного напряжения усилителя 21 в устройство 22. Такое выполнение блока 6 позволяет развязать его выход с выходом усилителя 21 и благодаря этому устранить пульсации на выходе блока, обусловленные переходными процессами, условно показанными на иаграммах кривыми вида . Для сокращения длительности цикла первый блок интегрирования выполнен в виде последовательного включения интегрирующего усипителя 23 со входом сброса и аналогового запоминающего устройства 24. Достоинство данного выполнения заключается в том, что оно позволяет совместить во времени операции интегрирования блоком 6 выходного напряжения блока 5 и операции интегрирования блоком 5 алгебраической суммы тока. Работа блока 5 в составе данного варианта заключается в периодическом сбросе интегрирующего усилителя 23, интегрировании им алгебраической суммы токов, соответствующих определенному такту и переписи результата (выходного напряжения усилителя 23) в устройство 24. Повыщение быстродействия обеспечивается в указанном варианте одновременным выполнением операций интегрирования бпоками 5 и 6 (так, например, в устройстве (фиг. 3) этим разнесенным во времени опершциям соответствуют кривые -bg и Ц. . Указанное совмещение операций оказывается возможным благодаря тому, что устройство 24 выполняет функции буферного запоминающего устройства, обеспечивающего выдачу постоянного напряжения на вход блока 6. Таким образом, предлагаемое устройство сохраняет присущую известному высокую линейность выходной характеристики, обеспечиваемую параллельным интегрированием токов, соответствующих выходному и опорному сигналам , одновременно позволяет устранить влияние ряда нестабильных величин на выходной сигнал управляемого источника напряжения.

Формула изобретения

вязана с входом регистра памяти, первый и второй выходы последнего подключены соответственно к входу преобразоателя код-напряжение и входу преобразователя кода во временной интервал, первый и второй входы аналогового сумматора соответственно связаны с выходами преобразователя код-напряжение и второго блока интегрирования, выход аналогового сумматора связан с выходной клеммой, выход преобразователя напряжения в ток через первый ключевой эпемент связан с входом первого блока интегрирования, первый вывод второго ключевого элемента соединен с входом первого блока интегрирования, а вход синхронизации регистра памяти, вход сброса первого блока интегрирования и вход управления второго блока интегрирования подключены к соответствующим выходам блока управления, отличающийс я тем, что, с целью повыщения точности, в него введены два коммутатора, второй преобразоватегаь напряжения в ток и матричный коммутатор, причем первый вхсд первого коммутатора и второй вход второго коммутатора связаны с выходной клеммой, второй вход первого коммутатора и первый вход второго коммутатора подключены к выходу опорного элемента, входы первого и второго преобразователей напряжения в ток соединены с выходом соответствующего коммутатора, выход второго преобразователя напряжения в ток соедийен с вторым выводом соответствующего ключевого элемента, первый и второй входы матричного коммутатора соединены соответственно с дополните пьным выходом блока управления и выходом преобразователя коа во временной интервал, первый и второй выходы матричного коммутатора свяаны с управляющим входом соответствующего ключевого элемента, а вход управления матричного коммутатора, объединенные первые входы управления первого и второго коммутаторов и объедиг

ненные вторые входы управления данных комтиутаторов подключены к соответству - юшим дополнительным выходам бгаока управления.

2, Источник по п. 1, о т л и ч а ю щ и й с я тем, что в него введены тре-тий и четвертый коммутаторы, а преоб;разователи напряжений в ток дополнитель|но снабжены HHBepcHbiN-m входами, и вто0рой блок интегрирования снабжен входом изменения направления интегрирования, причем первый вход третьего коммутатора объединен с вторым входом четвертого коммутатора и связан с выходной

5 клеммой, второй вход третьего коммутатора объединен с первым входом четвертого коммутатора и связан с выходом опорного элемента, выход третьего и четвертого коммутаторов соответственно свя0заны с инверсными входами первого и второго преобразователей напряжения в ток, а вход изменения направления интегрирования второго блока- интегрировайия, объединенные первые входы управ5ления и объединенные вторые входы управления третьего и четвертого коммутаторов подключены к соответствующим дополнительным выходам блока управления.

3,Источник по п. 1, о т л и ч а 0ю ш и и с я тем, что первый и второй коммутаторы дополнительно оборудованы тpeтьи rи входами и третьими входами управления, а второй бпок интегрирования снабжен входом изменения направления интегрирования, причем третий вход каждого коммутатора связан с выходом соответствующего введенного источника напряжения или с щиной нулевого потенци-

0 ала, а объединенные третьи входы управления коммутаторов и вход изменения направления интегрирования второго блока интегрирования подключены к соответствующим дополнительным выходам блока управления, .

5

4,Источник по пп. 2иЗ,отличающийся тем, что, с целью устранения пульсаций при изменении направления интегрирования второго блока интегрирования, данный блок оборудован

0 дополнительным входом считывания ре- эультата интегрирования, соединенным с соответству щи м выходом бпока управления, и выполнен в виде, последовательно включенного входного ключа, интегриру5ющего усилителя с входом изменения направления интегрирования и аналогового запоминающего устройства, причем вход считывания результата интегрирования 199 данного блока связан с входом синхронизации аналогового запоминающего устройства, а вход управления и вход изменения направления интегрирования бпока сое динены соответственно с входом управления входного ключа и входом изменения направления интегрирования интегрирующего усилителя. 5. Источник по пп. 2иЗ,отличающийся тем, что, с цепью увепичения быстродействия, первый блок интегрирования оборудован дополнительным входом считывания результата интегрирювания, соединенным с соответствующим выходом блока управления, и выпоииен в виде последовательного включения интегрирующего усилителя с входом сбро7220са и аналогового запоминающего устройства, причем вход считывания резупьтата интеГрирования данного бпока связан с входом синхронизации аналогового запоминающего устройства, а вход сброса блока соединен с соответствующим входом интегрирующего усилителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке № 2744404/24-07, кл. Q О5 F 1/44, 1979. 2.Авторское свидетельство СССР по заявке № 2942653/24-07, кл. Q 05 F 1/44, 21.О8.80.

20

L,I

Г

Т

л

f

« I

Авторы

Даты

1982-07-15—Публикация

1980-12-16—Подача