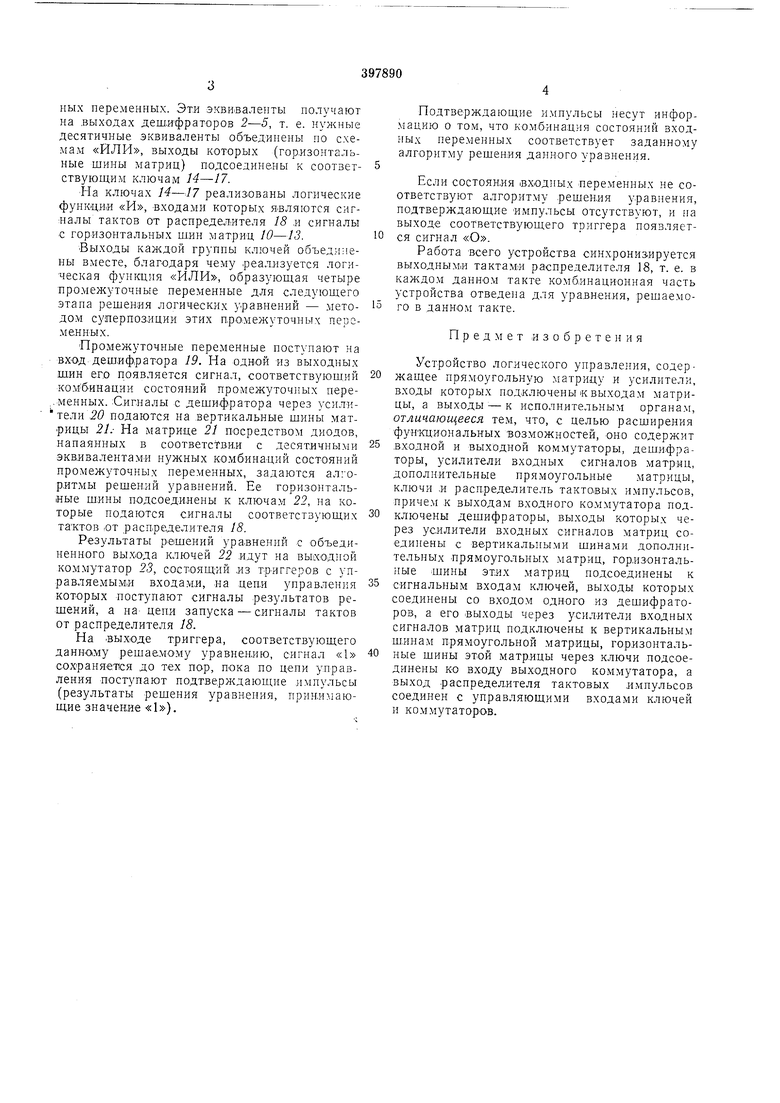

Устройство предназначено для использования в системах управления производствегшыМИ ме.ханизма.ми. Известны устройства логического управлеНИН, содержащие прямоугольную матрицу я усилител.и, входы которых подключены к выходам матрицы, а выходы - к исполнительным органам. Отличие описываемого устройства состоит в том, что оно содержит входной и выходной коммутаторы, дешифраторы, усилители входных сигналов матриц, дополнительные прямоугольные матрицы, ключи и распределитель тактовых импульсов, причем к выходам входпого коммутатора подключены дешифраторы, выходы которых через усилители входных сигналов матриц соединены с вертикальными шинами дополнительных прямоугольных матриц. Горизонтальные шины этих матриц подсоединены ,к сигнальным входам ключей, выходы которых соединены со входом одного из дешифраторов, а его выходы через усилители входных сигналов матриц подключе}1ы к вертикальным шинам нря.моугольной матрицы. Горизонтальные шины этой матрицы через ключи подсоединены ко входу выходного коммутатора, а выход распределителя тактовых импульсов соединен с управляющими входами ключей и коммутатооов. Это позволяет расширить функциональ.шю возможности устройства. На чертеже изобрал ена функциональная схе.ма устройства. Устройство содержит входной коммутатор /, дешифраторы 2-5, усилители 6-9 входных сигналов матриц, дополнительные прямоугольные матрицы 10-13, ключи 14-17, распределитель тактовых имнульсов 18, дешифратор 19. усилители 20. прямоугольную матрицу 21, ключи 22, выходной коммутатор 23. Все входные переменные поступают на коммутатор /, Выдающий на свои выходы в каждом такте работы устройства только те входные переменные, из которых состоит реализуемое ypaBiiesnie, решаемое в данном такте. Выходы коммутатора, группами по четыре или Meiee, подключе 1ы к дешифраторам 2-5. На одной из выходных пп.Г каждого 2 дешифратора появляются оггналы, соответствующ1 е комбинациям состояния входных нереме-шых. Эти оггналы через усилители 6-9 подсоединены к вертикальным шинам матпиц 10-13. Алгоритмы решений уравнений задаются соединением вертикальных шин матриц ./О-13 с горизонтальными -шинами посредством диодов, напаянных в соответствии с десятичными эквивалентами нужных комбинаций входных переменных. Эти эквиваленты иолучают на .выходах дешифраторов 2-5, т. е. нужные десятичные эквиваленты объединены но схемам «ИЛИ, выходы которых (гор.изонтальные шины матриц) подсоединены к соответствующим ключам 14-/7. На ключах 14-17 реализованы логические функции «И, входами которых я-вляются сигналы тактов от распределителя 18 ,и сигналы с горизонтальных Н1ин матриц 10-13. Выходы каждой группы ключей объед.чнепы вместе, благодаря чему .реализуется логическая функция «ИЛИ, образующая четыре промежуточные переменные для следующего этапа рещения логических уравнений - методом суперпозиции этих п,р0:межуточных переменных. Промежуточные переменные поступают на вход дешифратора 19. На одной из выходных щин его появляется сигнал, соответствуюш.ий комбинации состояний промежуточных пере.,.менных.-Сигналы с дешифратора через усили тели 5(9 подаются на вертикальные шины матрицы 2L На матрице 21 посредством диодов, напаянных в cooтвeтctвии с десятичными эквивалентами нужных комбинаций состояний промежуточных переменных, задаются алгоритмы решений уравнений. Ее горизо}1тальные щины подсоедилены к ключам 22, на которые подаются сигналы соответствующих тактов от распределителя 18. Результаты решений уравнений с объединенного выхода ключей 22 идут на выходной коммутатор 25, состоящий из триггеров с управляемыми входа.ми, на цепи управления которых поступают сигналы результатов решений, а на цепи запуска - сигналы тактов от распределителя 18. На -выходе триггера, соответствующего данному решаемОму уравнению, сигнал «1 сохраняемся до тех пор, пока по цепи управления поступают подтверждающие импульсы (результаты решения уравнения, принимающие значение «1). Подтверждающие н.мпульсы несут информацию о том, что комбинация состояний входных неременных соответствует заданному алгоритму решения данного уравнения. ЕСЛИ состояния (ВХОДНЫХ переменных не соответствуют алгоритму решения уравнения, подтверждающие импульсы отсутствуют, и на выходе соответствующего триггера появляется сигнал «О. Работа всего устройства синхронизируется выходными тактами распределителя 18, т. е. в каждо.м данном такте комбинационная часть устройства отведена для уравнения, решаемого в данно.м такте. Предмет изобретения Устройство логического управления, содержащее нрямоугольную матрицу и усилители, входы которых подключены «выходам матрицы, а выходы - к исполнительным органам, отличающееся тем, что, с целью расширения функциональных возможностей, оно содержит входной и выходной коммутаторы, дешифраторы, усилители входных сигналов матриц, дополнительные пря.моугольные матрицы, ключи и распределитель тактовых импульсов, причем к выходам входного коммутатора подключены дешифраторы, выходы которых через усилители входных сигналов матриц соединены с вертикальными шинами дополнительных -прямоугольных матриц, горизонтальные шины этих матрид подсоединены к сигнальным входам ключей, выходы которых соединены со вх-одом одного из дешифраторов, а его выходы через усилители входных сигналов матриц подключены к вертикальным шинам прямоугольной матрицы, горизонтальные шины этой матрицы через ключи подсоединены ко входу выходного коммутатора, а выход -распределителя тактовых -импульсов соединен с управляющими входами ключей и коммутатор-ов.

j i i I ,

) 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННЫЙ АДРЕСНЫЙ АВТОМАТ ДЛЯ ПРОГРАММНОГО | 1968 |

|

SU231228A1 |

| Устройство для многоканальной магнитной записи и воспроизведения последовательности импульсов | 1987 |

|

SU1483482A1 |

| Телеизмерительная система | 1982 |

|

SU1099322A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Управляющий автомат цифрового устройства числового управления | 1972 |

|

SU507153A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для измерения амплитуды импульсных сигналов | 1984 |

|

SU1223154A1 |

| ПОЛИМАГНИТНЫЙ ТЕРАПЕВТИЧЕСКИЙ АППАРАТ | 1992 |

|

RU2007198C1 |

| Устройство индикации измерительного прибора | 1984 |

|

SU1262395A1 |

Авторы

Даты

1973-01-01—Публикация