Предлагаемое изобретение относится к логическим устройствам, применяемым в вычислительной технике и автоматике, в частности, к пороговым логическим элементам.

Известны многопороговые логические устройства, использующие в качестве многопорогового дискриминатора туннельные диоды.

Однако использовать туннельные диоды в монолитных интегральных схемах затруднительно, поскольку при их изготовлении для получения желаемой величины тока /макс необходимо травление участка кристалла, в котором размещен туннельный диод. Кроме того, трудности возникают из-за хрупкости готового туннельного диода. Кремний, служащий материалом подложек для больщинства интегральных схем, не позволяет получать диоды, характеристики которых были бы столь же хороши, как и у диодов, изготовленных из германия и арсенида галлия. Следовательно, перспективы применения туннельных диодов в интегральных схемах, по крайней мере на ближайщее будущее, ограничены гибридными схемами.

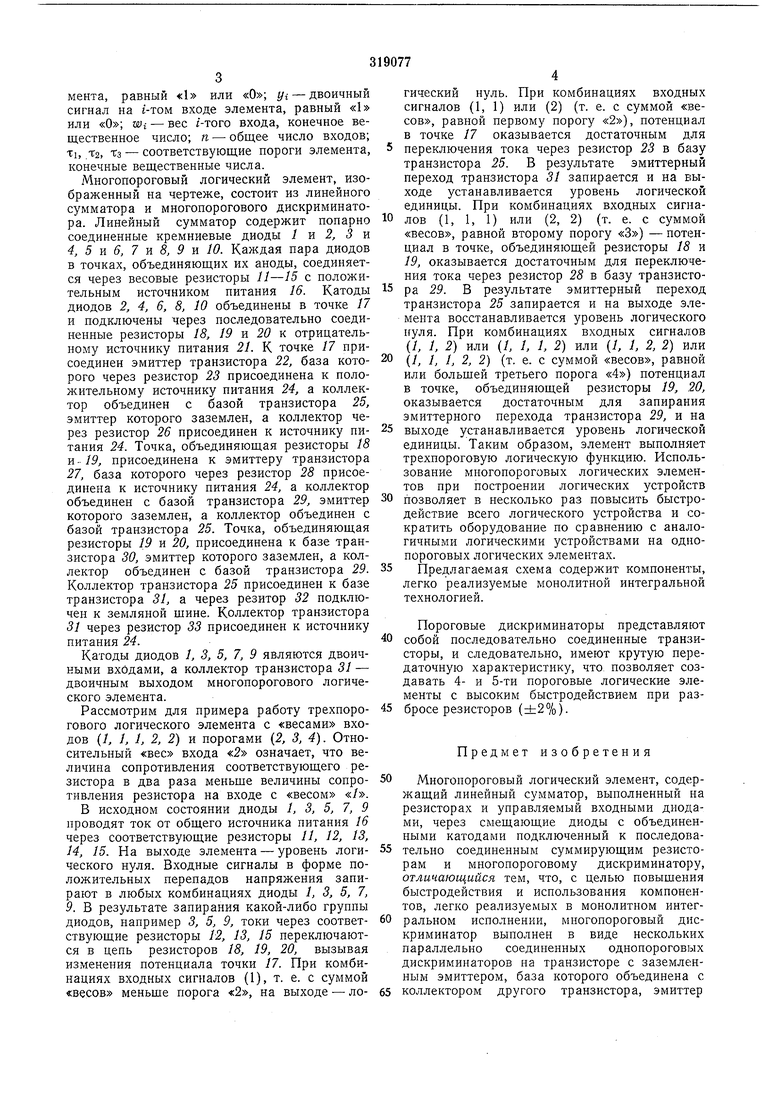

Цель предлагаемого изобретения заключается в том, чтобы создать быстродействующий многопороговый логический элемент на компонентах, легко реализуемых в монолитном интегральном исполнении. Для достижения этого многопороговый дискриминатор, представляющий собой несколько параллельно соединенных однопороговых дискриминаторов, каждый из которых выполнен на транзисторе с заземленным эмиттером, база транзистора объединена с коллектором другого

транзистора, эмиттер которого присоединен к соответствующему суммирующему резистору, развязывая тем самым каждый последующий дискриминатор с ббльщим значением порога от предыдущего, а коллектор присоедипен к базе аналогичного транзистора в предыдущем дискриминаторе.

Это позволяет получить многопороговую логическую функцию на коллекторе транзистора в дискриминаторе с минимальным порогом, являющимся выходом элемента.

На чертеже представлена принципиальная схема предлагаемого многопорогового логического элемента, выполняющего трехпороговую логическую функцию, т. е.

если

G 0,

если Wiiji

, i

,

если 2lVii/ii j,

i l , е /G - двоичный сигнал на выходе элемента, равный «1 или у г - двоичный сигнал на t-том входе элемента, равный «1 или Wi - вес /-того входа, конечное вещественное число; п - общее число входов; TI, Т2, тз - соответствующие пороги элемента, 5 конечные вещественные числа. Многопороговый логический элемент, изображенный на чертеже, состоит из линейного сумматора и многопорогового дискриминатора. Линейный сумматор содержит попарно Ю соединенные кремниевые диоды 1 и 2, 3 w. 4, 5 я 6, 7 н 8, 9 и 10. Каждая пара диодов в точках, объединяющих их аноды, соединяется через весовые резисторы 11-15 с положительным источником питания 16. Катоды 15 диодов 2, 4, 6, 8, 10 объединены в точке 17 и подключены через последовательно соединенные резисторы 18, 19 vi 20 к отрицательному источнику питания 21. К точке 17 присоединен эмиттер транзистора 22, база кото- 20 рого через резистор 23 присоединена к положительному источнику питания 24, а коллектор объединен с базой транзистора 25, эмиттер которого заземлен, а коллектор через резистор 26 присоединен к источнику пи- 25 тания 24. Точка, объединяющая резисторы 18 и-19, присоединена к эмиттеру транзистора 27, база которого через резистор 28 присоединена к источнику питания 24, а коллектор объединен с базой транзистора 29, эмиттер 30 которого заземлен, а коллектор объединен с базой транзистора 25. Точка, объединяющая резисторы 19 и 20, присоединена к базе транзистора 30, эмиттер которого заземлен, а коллектор объединен с базой транзистора 29. 35 Коллектор транзистора 25 присоединен к базе транзистора 31, а через резитор 32 подключен к земляной щине. Коллектор транзистора 31 через резистор 33 присоединен к источнику питания 24. Катоды диодов 1, 3, 5, 7, 9 являются двоичными входами, а коллектор транзистора 31 - двоичным выходом многопорогового логического элемента. Рассмотрим для примера работу трехпоро- 45 гового логического элемента с «весами входов (/, /, 1, 2, 2) и порогами (2, 3, 4). Относительный «вес входа «2 означает, что величина сопротивления соответствующего резистора в два раза меньще величины сопро- 50 тивления резистора на входе с «весом «/. В исходном состоянии диоды /, 3, 5, 7, 9 проводят ток от общего источника питания 16 через соответствующие резисторы 11, 12, 13, 14, 15. На выходе элемента - уровень логи- 55 ческого нуля. Входные сигналы в форме положительных перепадов напряжения запирают в любых комбинациях диоды /, 3, 5, 7, 9. В результате запирания какой-либо группы диодов, например 3, 5, 9, токи через соответ- 60 ствующие резисторы 12, 13, 15 переключаются в цепь резисторов 18, 19, 20, вызывая изменения потенциала точки 17. При комбинациях входных сигналов (1), т. е. с суммой «весов меньще порога «2, на выходе - ло- 65 40 гический нуль. При комбинациях входных сигналов (1, 1) или (2) (т. е. с суммой «весов, равной первому порогу «2), потенциал в точке 17 оказывается достаточным для переключения тока через резистор 23 в базу транзистора 25. В результате эмиттерный переход транзистора 31 запирается и на выходе устанавливается уровень логической единицы. При комбинациях входных сигналов (1, 1, 1) или (2, 2) (т. е. с суммой «весов, равной второму порогу «3) - потенциал в точке, объединяющей резисторы 18 и 19, оказывается достаточным для нереключения тока через резистор 28 в базу транзистора 29. В результате эмиттерный переход транзистора 25 запирается и на выходе элемента восстанавливается уровень логического пуля. При комбинациях входных сигналов (1, 1, 2) или (1, 1, 1, 2) или (1, 1, 2, 2) или (у д д 2, 2) (т. е. с суммой «весов, равной или большей третьего порога «4) потенциал в точке, объединяющей резисторы 19, 20, оказывается достаточным для запирания эмиттерного перехода транзистора 29, и на выходе устанавливается уровень логической единицы. Таким образом, элемент выполняет трехпороговую логическую функцию. Использование многопороговых логических элементов при построении логических устройств позволяет в несколько раз повысить быстродействие всего логического устройства и сократить оборудование по сравнению с аналогичными логическими устройствами на однопороговых логических элементах. Предлагаемая схема содержит компоненты, легко реализуемые монолитной интегральной технологией. Пороговые дискриминаторы представляют собой последовательно соединенные транзисторы, и следовательно, имеют крутую передаточную характеристику, что позволяет создавать 4- и 5-ти пороговые логические элементы с высоким быстродействием при разбросе резисторов (±2%). Предмет изобретения Многопороговый логический элемент, содержащий линейный сумматор, выполненный на резисторах и управляемый входными диодами, через смещающие диоды с объединенными катодами подключенный к последовательио соединенным суммирующим резисторам и многопороговому дискриминатору, отличающийся тем, что, с целью повышения быстродействия и использования компонентов, легко реализуемых в монолитном интегральном исполнении, многопороговый дискриминатор выполнен в виде нескольких параллельно соединенных однопороговых дискриминаторов на транзисторе с заземленным эмиттером, база которого объединена с коллектором другого транзистора, эмиттер

которого подключен к соответствующему суммирующему резистору, а коллектор присоединен к базе аналогичного транзистора в предыдущем дискриминаторе.

16 о-

1/2

7

73

75

Даты

1971-01-01—Публикация