1

Изобретение относится к функциональным узлам вычислительных устройств.

Известные делители частоты повторения импульсов на четыре недостаточно экономичны и надежны.

Для повышения экономичности и надежности в предлагаемом устройстве нулевая шипа соединена со схема.ми совпадения нечетных триггеров, а единичная шина - со схемами совпадения четных триггеров, нулевой выход второго триггера соединены со схемами совпадения третьего триггера, а единичный выход - со схемами совпадения первого триггера, нулевой выход первого триггера соединен со схе.мой совнадения нулевого входа третьего триггера и первой схемой совпадения нулевого входа и второй схемой совпадения единичного входа второго триггера, единичный ВЫХОД первого триггера соединен со схемой совпадения единичного входа третьего триггера и второй схемой совпадения нулевого входа и первой схемой совпадения единичного входа второго триггера, нулевой выход третьего триггера соединен со схемой совпадения единичного входа первого триггера и вторыми схемами совпадения единичного и нулевого входа второго триггера, единичный выход третьего триггера соединен со схемой совпадения нулевого входа первого триггера и первыми схемами совпадения нулевого и

единичного входа второго триггера, первая И вторая схемы совпадения как нулевого, так и единичного входа второго триггера осуществляют между собой логическую операцию

«ИЛИ.

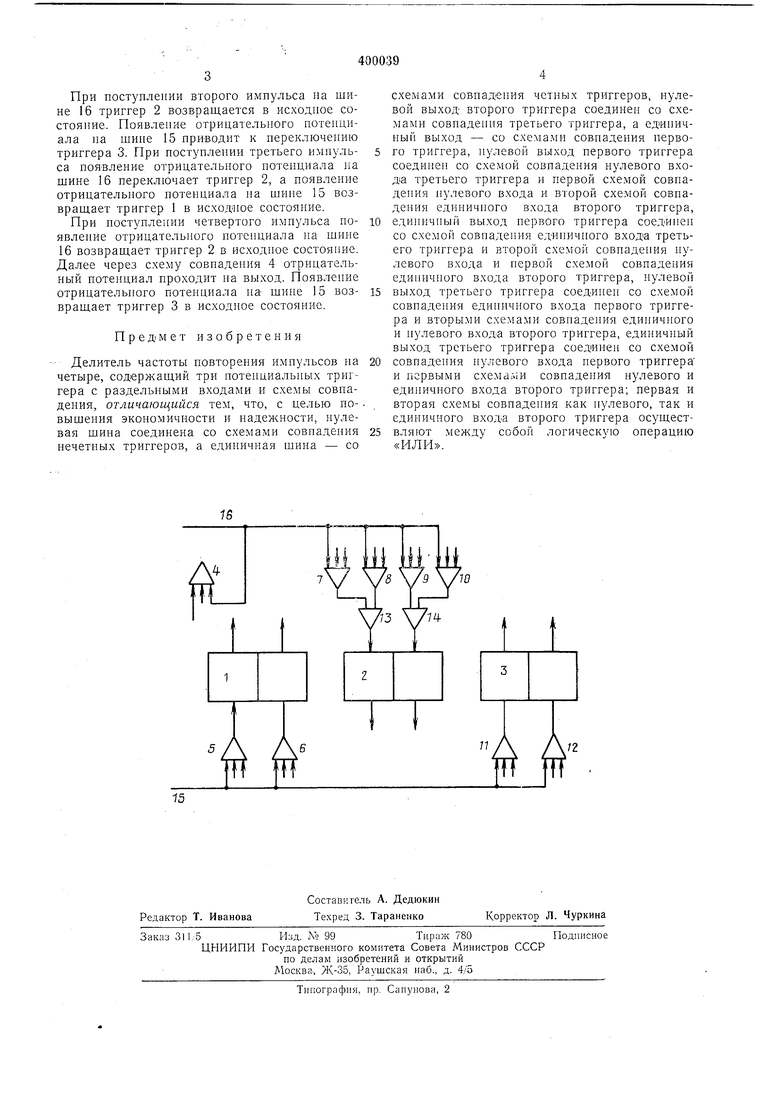

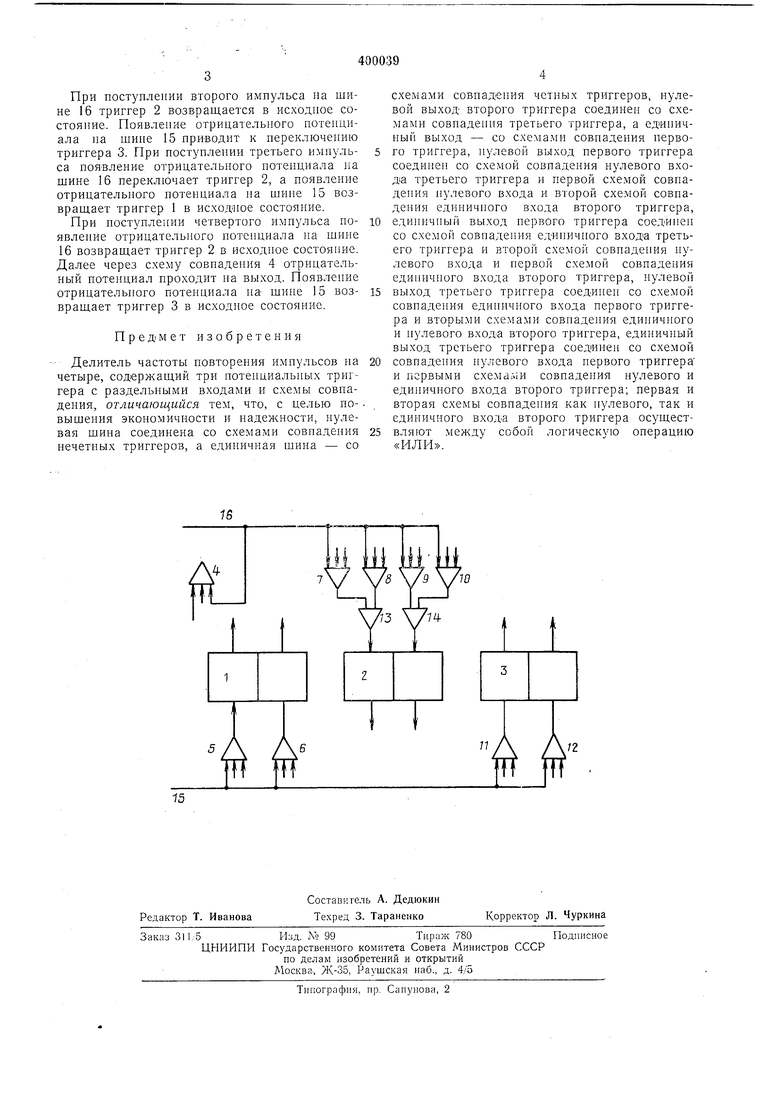

На чертеже изображена схема предлагаемого устройства.

В устройство входят потенциальные триггеры 1, 2 и 3, схемы совпадения 4-12, схемы

разделения 13 и 14, нулевая 15 и единичная 16 шины.

Схемы разделения 13 и 14 могут быть реализованы при помощи одного из диодов схемы совпадения, подсоединенного к входу

«ИЛИ потенциального триггера.

Иотенцнальиые триггеры, которые входят в делитель, переключаются двумя сериями счетных импульсов, сдвинутых по фазе на 180°. Если имеется только одна серия счетных

импульсов, то реализация второй серии возможна схемами, которые выполнены на элементах, представляющих собой инверторы. Исходным состоянием устройства является наличие отрицательного (единичного) потенциала на нулевых выходах триггеров и на шине 15.

Ири появлении отрицательного нотенциала па шипе 16, триггер 2 меняет свое состояние, а появление отрицательного потенциала на

шине 15, изменяет состояние триггера 1.

3

При поступлении второго импульса па шине 16 триггер 2 возвращается в исходное состояпие. Появление отрицательного потенциала па шине 15 приводит к переключению триггера 3. При поступлепии третьего импульса появление отрицательного потенциала на шине 16 переключает триггер 2, а появление отрицательного потенциала на шине 15 возвращает триггер 1 в исходное состояние.

При ностунлении четвертого имнульса ноявление отрицательного потенциала на шнне 16 возвращает триггер 2 в исходное состояние. Далее через схему совнадения 4 отрицательный потенциал проходит на выход. Появление отрицательного потенциала на- шине 15 возвращает триггер 3 в исходное состояние.

Предмет изобретения

Делитель частоты повторения импульсов на четыре, содержащий три потенциальных триггера с раздельными входами н схемы совпадения, отличающийся тем, что, с целью повышения экономичности и надежности, нулевая шина соединена со схемами совпадения нечетных триггеров, а единичная шина - со

4

схемами совнадения четных триггеров, нулевой выход второго триггера соединен со схемами совнадення третьего триггера, а единичный выход - со схемами совнадения первого триггера, нулевой выход первого триггера соединен со схемой совпадения нулевого входа третьего триггера и первой схемой совпадения нулевого входа и второй схемой совпадення единичного входа второго триггера, единичный выход нервого триггера соединен со схемой совпадения единичного входа третьего триггера и второй схемой совнадения нулевого входа и первой схемой совпадения единичного входа второго триггера, нулевой выход третьего триггера соединен со схемой совнадения единичного входа первого триггера и вторыми схемами совнадения единичного и нулевого входа второго триггера, единичный выход третьего триггера соединен со схемой совпадения нулевого входа нервого триггера и первыми схемалш совпадения нулевого и единичного входа второго триггера; первая и вторая схемы совпадения как нулевого, так и единичного входа второго триггера осуществляют между собой логическую операцию «ИЛП.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕГИСТР ЦИФРОВОГО АВТОМАТИЧЕСКОГО ПРИБОРА С ПОРАЗРЯДНЫМ ВЗВЕШИВАНИЕМ | 1970 |

|

SU277019A1 |

| УСТРОЙСТВО для ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1973 |

|

SU405126A1 |

| Десятичный сумматор | 1973 |

|

SU486319A1 |

| Формирователь импульсов | 1979 |

|

SU813733A1 |

| Устройство для управления шаговым двигателем | 1972 |

|

SU437051A1 |

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1967 |

|

SU216130A1 |

| Делитель частоты повторения импульсов на четыре | 1975 |

|

SU534873A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1967 |

|

SU194423A1 |

| Устройство синхронизации | 1971 |

|

SU478429A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1972 |

|

SU341030A1 |

Л

LI

Г

Авторы

Даты

1973-01-01—Публикация