1

Изобретение относится к телеграфной связи и может быть использовано для замера и контроля параметров дискретного канала связи.

Известно устройство для определения достоверности контрольной двоичной информации, содержащее схему циклового фазирования, выход которой подключен к одному входу клапана через датчик контрольной последовательности и сумматор по модулю два, ко второму входу клапана - через динамический триггер, а к счетчику циклов опробирования - непосредственно. Известное устройство позволяет вести анализ синфазности контрольной последовательности, поступающей из канала связи, с последовательностью импульсов, генерируемых автономным датчиком, установленным на приемном конце. При этом определение расфазирования производится по анализу результатов сравнения канальной и .местной контрольных последовательностей.

Однако известное устройство не может однозначно установить расфазирование между приемником и передатчиком контрольных последовательностей.

Целью изобретения является повышение точности.

Для этого между выходом схемы циклового фазирования и датчиком контрольной последовательности включена схема выделения од2

ной первой единицы, а к выходу схемы циклового фазирования дополнительно подключена цепь из последовательно соединенных дополнительных датчика контрольной последовательности, сумматора по модулю два и клапана, выход которого подключен ко вторым входам динамического триггера и схемы выделения одной первой единицы и является выходом устройства, причем ко вторым входам

дополнительных сумматора по модулю два и клапана подключены выходы датчика контрольной последовательности и динамического триггера соответственно, а выходы счетчика циклов опробирования подключены ко вторым

входам схемы циклового фазирования и клапана.

В предложенном устройстве дополнительный датчик контрольной последовательности

импульсов периодически фазируется с контрольной последовательностью, поступающей из канала связи, и после фазирования производит позначное сравнение с последовательностью, вырабатываемой основным датчиком

контрольной последовательности. Синфазное положение последовательностей, генерируемых основным и дополнительным датчнком, определяет, что во время между передачамн двух посылок синхронизации расфазирования не

было.

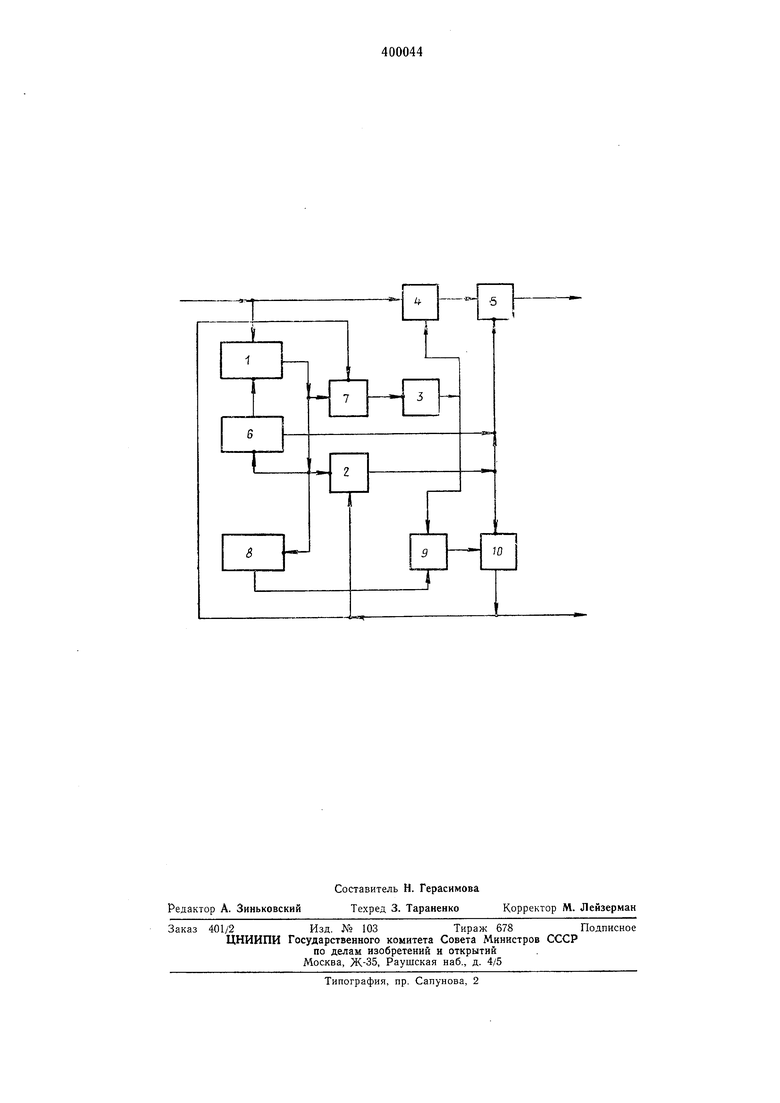

На чертеже приведена функциональная блок-схема устройства.

Устройство для определения достоверности контрольной двоичной информации содержит схему 1 циклового фазирования, динамический триггер 2, датчик 3 контрольной последовательности, сумматор 4 но модулю два, клапан 5, счетчик 6 циклов опробирования, схему 7 выделения одной первой единицы, дополнительный датчик 8 контрольной последовательности, сумматор 9 по модулю два и клапан 10.

Устройство работает следующим образом.

Процесс первоначального пуска устройства аналогичен процессу при расфазировании. Данное состояние характеризуется тем, что триггер 2 запущен, в результате чего закрыты клапаны 5 и 10, схема 1 циклового фазирования установлена в положение поиска начала цикла и схема 7 выделения одной первой единицы сфазирована в исходное состояние.

После успешного фазирования сигнал со схемы 1 циклового фазирования, определяющий начало цикла, пройдя через схему 7 выделения первой единицы, произведет фазирование (перефазирование) датчика 3, произведет сброс триггера 2 и фазирование (нерефазирование) датчика 8 и запустит счетчик 6 циклового опробирования. В результате синхронного запуска двух датчиков 8 и 3 с последовательностью сигналов, поступающих из канала связи, сигналы, поступающие на входы сумматоров 4 и 9, будут совпадать. Сигналы с сумматора 4, пройдя через открытый клапан 5, поступают а счетную часть прибора как «ошибка, на сигналы с сумматора 9 характеризуют синфазность последовательностей, генерируемых датчиками 3 и 8.

В устройстве один раз в цикл в канал связи передается посылка синхронизации. Для обеспечения ее нриема сигнал с выхода счетчика 6 производит установку схемы 1 циклового фазирования в положение поиска фазы. Кроме этого, на время передачи посылки синхронизации производится блокировка ложных знаков «ошибка на клапане 5, для чего с выхода счетчика 6 в течение времени поступления посылки синхронизации на кланан 5 поступает запрещающий сигнал.

При успешном приеме посылки синхронизации, сигнал о выходе схемы 1 циклового фазирования поступит на подтвержение состояния триггера 2 и на физирующий вход датчика 8. Фазирование датчика 3 при этом не производится, так как схема 7 не пропускает сигнал со схемы 1 циклового фазирования. При этом, в случае, если за время цикла замера последовательность, поступающая из канала связи, и последовательность, генерируемая

датчиками 3 и 8, не были расфазированы, датчик 8 не будет перефазироваться (сигнал со схемы циклового фазирования подтверждает его фазовое положение) и с сумматора 9 через кланан 10 будут поступать нули. В случае, если за цикл замера было расфазирование, то очередным приемом фазы цикла схемы 1 циклового фазирования датчик 8 будет зафазирован с фазой канальной последовательности, после чего последовательности с датчиков 3 и 8 не будут совпадать и с сумматора 9 через клапан 10 начнут поступать сигналы единиц, определяющие расфазирование. Сигнал с клапана 10 поступит сигналом расфазирования на сигнализацию расфазирования и на перезапуск устройства в режим полного перефазирования. Таким образом, за счет периодического фазирования датчика 8 один раз в цикл, определяемый счетчиком 6, осуществляется проверка фазового положения канальной последовательности и последовательности, генерируемой датчиком 3. В результате этого факт расфазирования обнаруживается сразу же после приема фазы цикла схемой 1

циклового фазирования, а расфазирование устанавливается однозначно, независимо от длительности обрыва канала связи и плотности потока ошибок.

Предмет изобретения

Устройство для определения достоверности контрольной двоичной информации, содержащее схему циклового фазирования, вы.ход которой подключен к одному входу клапана через датчик контрольной последовательности и сумматор по модулю два, ко второму входу клапана - через динамический триггер, а к счетчику циклов опробирования - непосредственно, отличающееся тем, что, с целью повышения точности, между выходом схемы циклового фазирования и датчиком контрольной последовательности включена схема выделения одной первой единицы, а к выходу схемы циклового фазирования дополнительно подключена цепь нз последовательно соединенных дополнительных датчика контрольной последовательности, сумматора по модулю два и клапана, выход которого подключен ко вторым входам динамического триггера и схемы выделения одной первой единицы и является выходом устройства, нричем ко вторым входам дополнительных сумматора по модулю два и клапана подключены выходы датчика контрольной последовательности и динамического

триггера соответственно, а выходы счетчика циклов опробирования подключены ко вторым входам схемы циклового фазирования и клапана.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| Устройство фазирования по циклам | 1988 |

|

SU1601773A1 |

| Устройство фазирования циклов многоканальной системы передачи дискретной информации | 1980 |

|

SU896782A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| ПАТЕНТНО ТЕХНЯНГ К** | 1972 |

|

SU344597A1 |

| МОДУЛЬ УПЛОТНЕНИЯ РЕЧЕВЫХ СООБЩЕНИЙ ПАКЕТАМИ ДАННЫХ | 1995 |

|

RU2103825C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство контроля дискретного канала связи | 1984 |

|

SU1246392A1 |

| Устройство для измерения достоверности передачи информации по дискретному каналу связи | 1982 |

|

SU1113892A1 |

| Устройство избирательного вызова и передачи кодограмм | 1983 |

|

SU1136326A1 |

Авторы

Даты

1973-01-01—Публикация