Изобретение относится к технике связи и может найти применение в аппаратуре повышения достоверности передачи информации.

В известном устройстве цикловой синхронизации при приеме двоичной информации, передаваемой непрерывными (цепными) кодами, содержащем регистр информационных символов, регистр проверочных символов, регистр обнаружения ошибки, сумматор по модулю 2, выходной сумматор и схему «И, имеют место: ввод дополнительной избыточной информации, которая, снижая скорость передачи полезной информации, не используется для повышения ее достоверности; наличие переменных задержек в передаче ийформации; большое время вхождения в синхронизм.

В предлагаемом устройстве, с целью уменьшения времени вхождения в синхронизм, выход регистра информационных символов подключен через дополнительный регистр к одному из входов дублирующего сумматора, к двум другим входам которого подключены соответствующие выходы регистра проверочных символов, а выход дублирующего сумматора подключен к анализатору, кроме того, выход сумматора по модулю 2 подключен одновременно ко входу другого анализатора и ко входу дополнительного сумматора, ко второму входу которого подключен датчик посылок

синхронизации, а выход дополнительного сумматора подключен ко входу регистра обнаружения ошибок.

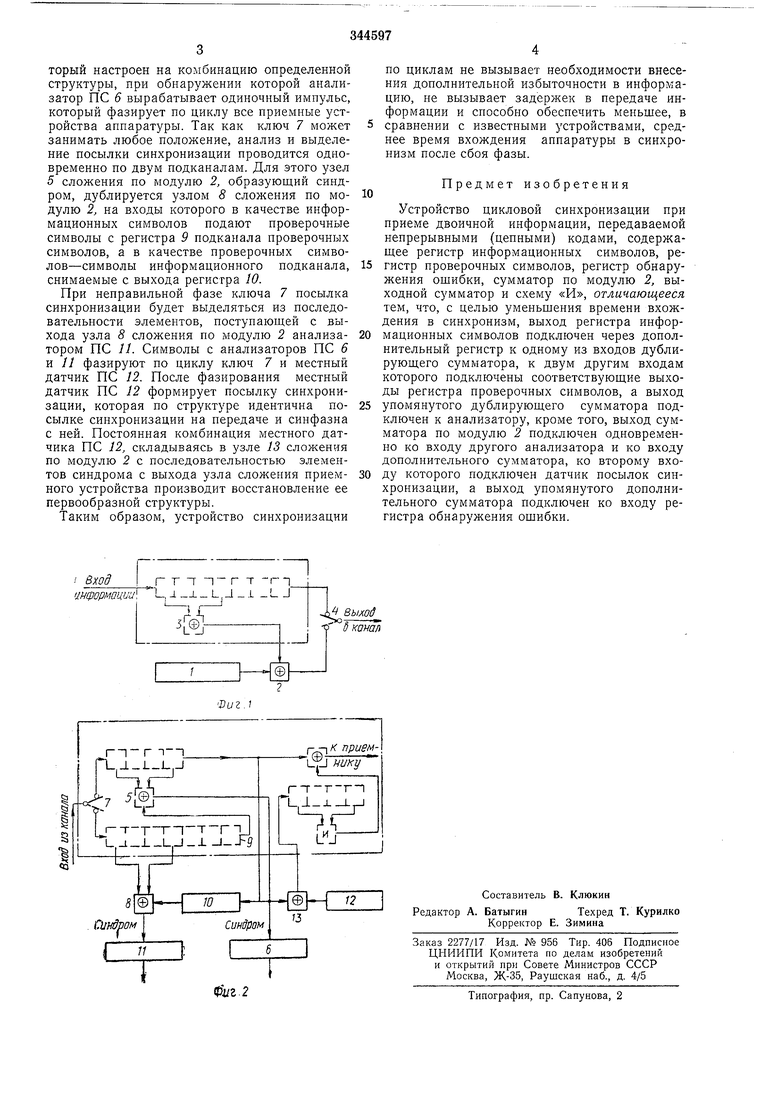

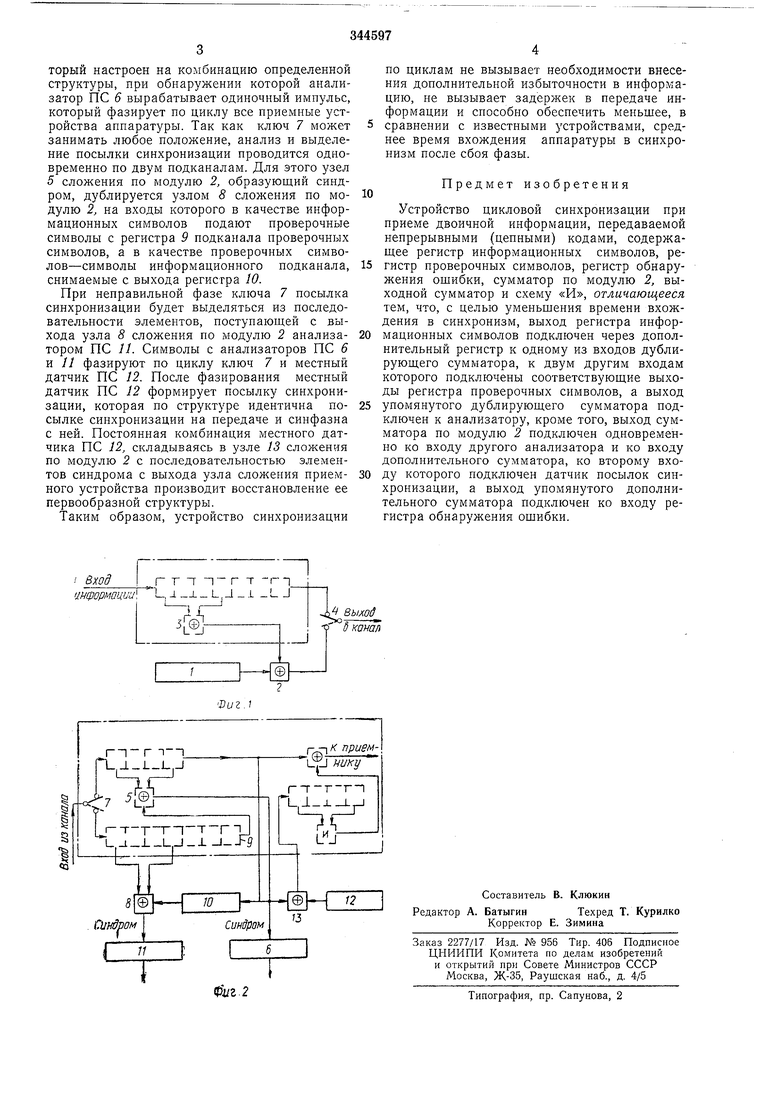

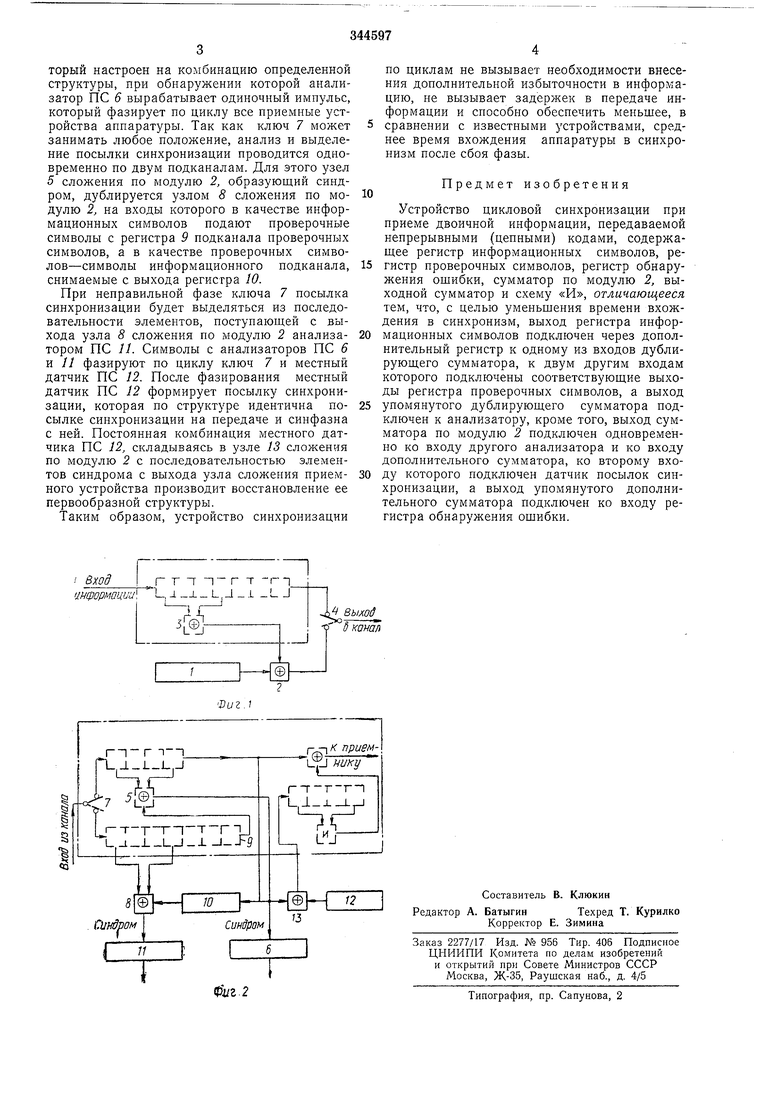

На фиг. I показана блок-схема передающей части предлагаемого устройства; на фиг. 2 - блок-схема приемной части предлагаемого устройства.

На передаче посылка синхронизации, сформированная датчиком / посылки синхронизации, складывается в узле 2 сложения по модулю 2 с проверочными символами цепного кода, идущими с устройства 3, и далее, через ключ 4, поступает в канал связи. Посылки синхронизации поступают непрерывно и длина их выбирается кратной длине кодовой комбинации информации.

Сложение по модулю 2 посылки синхронизации с проверочными символами эквивалентно их искажению. Поэтому на приеме с выхода узла 5 сложения по модулю 2 будет получена последовательность элементов проверок (синдром), структура которой одинакова со структурой посылки синхронизации при отсутствии искажений в принимаемой последовательности сигналов, обусловленных помехами в канале связи.

торый настроен на комбинацию определенной структуры, при обнаружении которой анализатор ПС 6 вырабатывает одиночный импульс, который фазирует по циклу все приемные устройства аппаратуры. Так как ключ 7 может занимать любое положение, анализ и выделение посылки синхронизации проводится одновременно по двум подканалам. Для этого узел 5 сложения по модулю 2, образующий синдром, дублируется узлом 8 сложения по модулю 2, на входы которого в качестве информационных символов подают проверочные символы с регистра 9 подканала проверочных символов, а в качестве проверочных символов-символы информационного подканала, снимаемые с выхода регистра 10.

При неправильной фазе ключа 7 посылка синхронизации будет выделяться из последовательности элементов, поступающей с выхода узла 8 сложения по модулю 2 анализатором ПС 11. Символы с анализаторов ПС 6 и 11 фазируют по циклу ключ 7 и местный датчик ПС 12. После фазирования местный датчик ПС 12 формирует посылку синхронизации, которая по структуре идентична посылке синхронизации на передаче и синфазна с ней. Постоянная комбинация местного датчика ПС 12, складываясь в узле 13 сложения по модулю 2 с последовательпостью элементов синдрома с выхода узла сложения приемного устройства производит восстановление ее первообразной структуры.

Таким образом, устройство синхронизации

по циклам не вызывает необходимости внесения дополнительной избыточности в информацию, не вызывает задержек в передаче информации и способно обеспечить меньшее, в сравнении с известными устройствами, среднее время вхождения аппаратуры в синхронизм после сбоя фазы.

Предмет изобретения

Устройство цикловой синхронизации при приеме двоичной информации, передаваемой непрерывными (цепными) кодами, содержащее регистр информационных символов, регистр проверочных символов, регистр обнаружения ошибки, сумматор по модулю 2, выходной сумматор и схему «И, отличающееся тем, что, с целью уменьшения времени вхождения в синхронизм, выход регистра ипформационных символов подключен через дополнительный регистр к одному из входов дублирующего сумматора, к двум другим входам которого подключены соответствующие выходы регистра проверочных символов, а выход

упомянутого дублирующего сумматора подключен к анализатору, кроме того, выход сумматора по модулю 2 подключен одновременно ко входу другого анализатора и ко входу дополнительного сумматора, ко второму входу которого подключен датчик посылок синхронизации, а выход упомянутого дополнительного сумматора подключен ко входу регистра обнаружения ошибки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приемо-передачи двоичной информации | 1982 |

|

SU1019654A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Пороговый декодер сверточного кода | 1989 |

|

SU1667264A1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1988 |

|

SU1555902A2 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| УСТРОЙСТВО ВРЕМЕННОГО УПЛОТНЕНИЯ АСИНХРОННЫХ | 1973 |

|

SU385399A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

| Устройство третьей решающей схемы ускоренного поиска и эффективного приема широкополосных сигналов | 2019 |

|

RU2718753C1 |

| ПРИЕМНО-ПЕРЕДАЮЩЕЕ УСТРОЙСТВО ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2123761C1 |

б/дг г т-г п I-г

12Нформаци , J. .j. LJ J i L J

,(|i

Даты

1972-01-01—Публикация