Изобретение относится к области элекгроизм е р и те л ЬН о и тех н №к и.

Известный Цифровой частотомер, содержащий реверсивный -счетчик, делитель опорной частоты, набор .схем совпааения л собирателыную цепь, .ктеризуе1ч;я пони.жетенымИ то-чно,стыо и быотрадействием, суженными ф ункцЯ он а л ь н ьг.м и в оз мо ж н остя-м н, ОТ у тс твием возможностей устранения пульсаций из.мерявмой частоты и получения ум.ножемиого значен я входной частоты.

Предлагаемый частотомер для ПОВЫШВИРЕЯ точности и быстродействия, а также расширения функционалыных возможностей снабл еН регистрам памяти, входы которого соединены с выходами рев&рсннного счетч.ика, выходы - с входами пепей со-згпа.дения, а вход управлеиня занисыо кода - с выходом делителя опорной частоты.

Для уст-ранения влИяния на результат измере гия иу.льсац.нй измеряемой частоты частотомер снабжен триггеров и -ключом, выход которого соединен с входом управления записью кода регистра памяти, вход - с источни-ком сигнала, модулирующего измеряемую частоту, и первым входом триггера, вто(рой вход которого 1гюдключен к выходу делителя опорной частоты, а выход - к управляюи1,ему входу ключа.

того, предложенный частотомер снабжен )Л и ключо.м, выход которого соединен с входом хправления записью кода регистра пам;:ти, вход - с входной клеммой, старшими разрядами -реверсив-ного счетчика и

нервы.м входом трнтгера, второй вход которого иодключо} к выходу дел.ителя опор-ной частоты, а выход - к управляющему входу ключа, что иозволяст повысить быстродействие н обеспечить получение х-м гюжеиного значения входi:oi частоты.

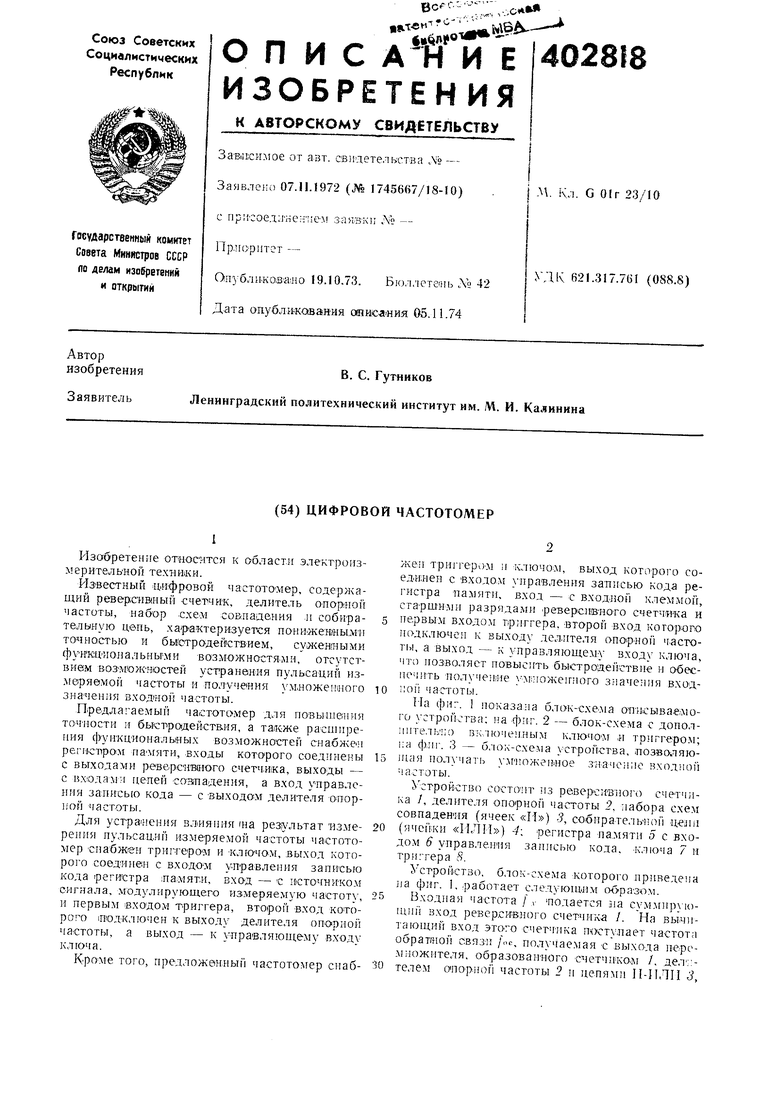

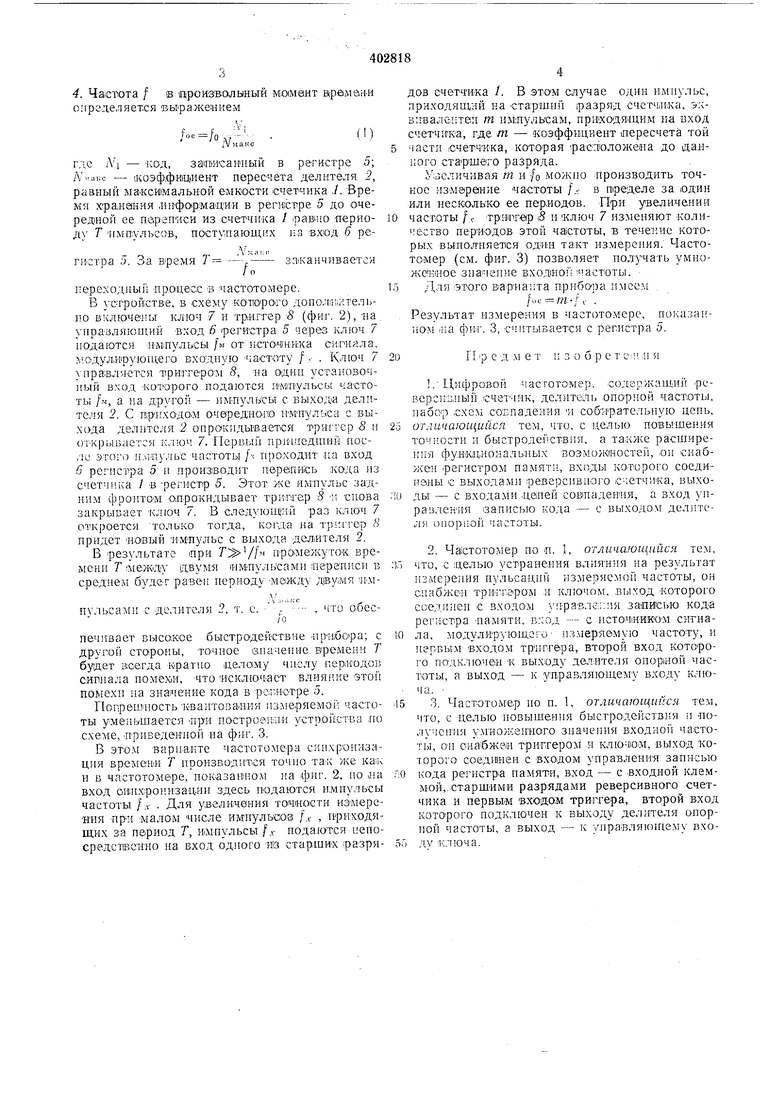

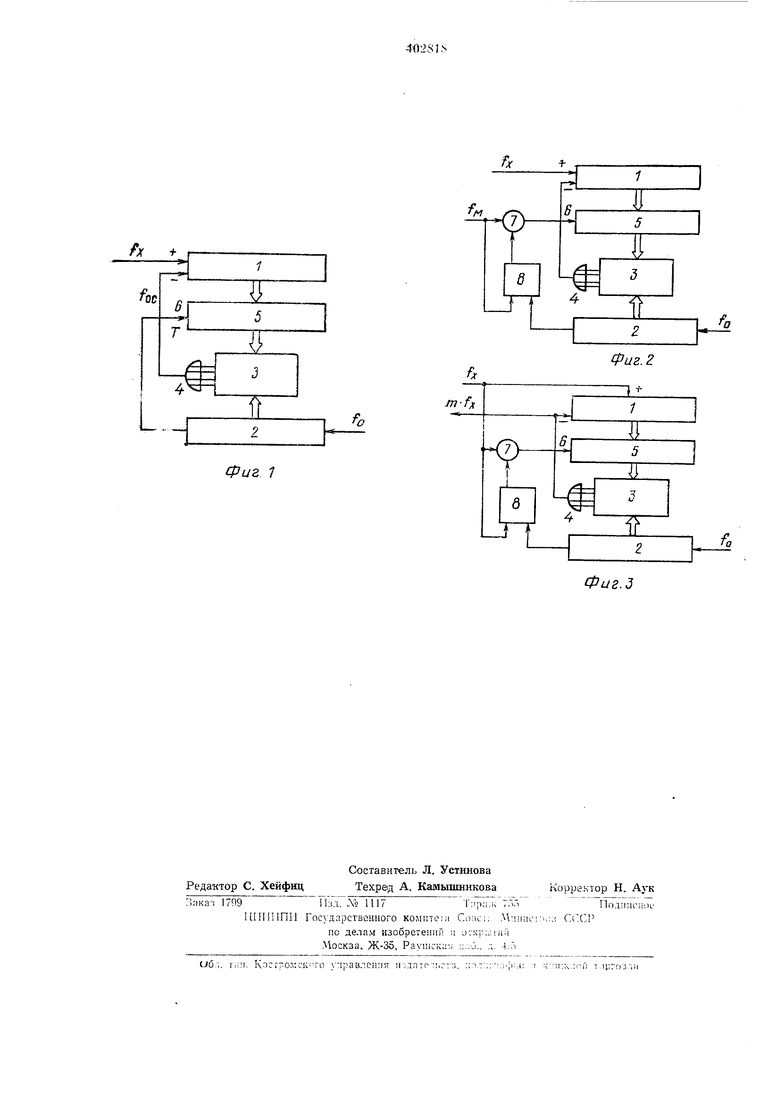

Ма фиг. 1 ноказана блок-схе ма откываемого устройства: на фиг. 2 - блок-схема с дополшггельпо вк;1ючеиным ключоМ и триггеро.м; i:a ф.нг. 3 - блок-схема устройства, лозйоляюии1Я получать у.миожеи«ое значение нходуюй частоты.

Устройство состо.мт из реверсивпого счетчика /, делителя опорной частоты 2, набора схем совпадения (ячеек «И) 3, собпрателыни цезш

(ячейки «ИЛИ) 4; регистра иа,мяти 5 с входом 6 управления заинсью кода, ключа 7 и триггера 8.

Устройство, блок-схема которого нриведе 1а иа фиг. 1,;работает следующим абразом.

Входная частота /г подается ла суммируюHuni вход реверсивпого счетчик.а /. Иа вычитзтщий вход этого счетчика поступает частота обрат/ной связи , получаемая -с выхода перомножителя, образованного счетчико..м /, дел::телем тЮрпой частоты 2 н цеиялгн И-ИЛИ 3,

4. Частота / в рроизволыный момент ареман-и определяется сыражеиием

/0

iV м а к с

где Ai - ico-д, за1гвисан ый в регистре 5; Лчакс - (Коэффициент пересчета делителя 2, равный максимальной емкости счетчика J. Время Хра,не1кия .информации в регистре 5 до очередной ее пе;реписи из счетчика / равчю периоду Т Импульсов, nocTvaaioutHx lia вход 6 регМСтра 5. За время 7 --. зп1ка} чивается

/о

переходньп ; npoiuecc л -частотомере.

В устройстве, в схему Которо-го доно-гпиятель 0 включены ключ 7 и триггер 8 (фиг. 2), на унрайляюнцп вход 6 регистра 5 через ключ 7 иодаются и-м пульсы м от источ Н:И:ка ск:гнала, мс-дул.И1руюи№го входную Частоту / . Ключ 7 уиравляется трнатеро м 8, на один установочный вход -которого подаются Им:пульсы частоты /м, а другой - иМПульсы с выход-а делителя 2. С шрИходОМ ОЧереднопо н-м-нулуса с вы.хада делителя 2 опракидывается триггер 8 н открывается 7. Первый прищеднтий после этого и:ч;пу,иьс частоты j-- Г1)оходит -на вход 6 регистра 5 и нроизводит перепись кода из счетчика 1 -в регистр 5. Этот же имнульс задним фронтом ол-рокидывает тркаа-ер 8 -и сн-ова закрывает к;поч 7. В следуюнскй раз ключ 7 откроется только тогда, ivoivta на трмтер 8 придет НОВЫЙ импульс с выхода дел1ителя 2.

В результате при нроаюжуток времени Т меж1Д:у двум-я (импульсами переписи в среднем будег равен периоду -меикду двумя , что о;беспульсами с делителя 2, т. с.

печивает высокое быстродействие ирИ;бора; с другой стороны, точное впаченне времени 7 будет всегда кратно целому числу г.ер иодов сигиала помехгИ, что -исключ-ает влияние зтой помехи иа зна1чение кода в рсл-истре 5.

Попрешность кваитовааши измеряемо ; частоты уменьшается нр-и построе нии устройства -по схеме, ириведеипой па фиг. 3.

В этом частотомера синхронизаЩ1Я времени Т производится точно та-к же каоч и в частотомере, показап ном иа фиг. 2, по ла вход оиихрон.изац.ии здесь иодаются и.мпульсы частоты /л- . Для увеличения точности измерения при :малом числе илгпульсоз f.,- , прикодящих за п&риод Т, импульсы f ,, подаются непосредствсино на вход одного ш старших разрядов счетчика /. В этом случае один имнульс, приходящий на старший .разряд счетч|Ика, эквн-валентем т имлульсам, приходящим на вход счетч: -Ка, где т - коэффи-циепт лересчета той

части счетчика, которая раслоложеиа до даипого старшего разряда.

Увеличивая т и /о можно Нроизводить точное из-ме реиие частоты /.v в пределе за один или несколько ее периодов. При увеличении

частоты fr тр:И 1те1р 8 и .ключ 7 изменяют количество периодов этой частоты, в течение которых выполняется один та.кт измерения. ЧастотоМер (см. фиг. 3) позволяет получать умноженное значеиие входной частоты. 71,ля этого вариаита прибо-ра имеем

/ос--m-/v .

Результат измерения в частотомере, показан iOM Ilia фиг. 3, считывается с регистра 5.

Г ip с д Л1 е т II 3 о б -р е т с i. -и я

;.Цифровой частотСмер, содержащи; -реверси1;иый счет-и-гк, делител) опо-рн-ой ч.а-стоты, набор схем соБпадения и собИрательную цегь,

отличающийся тем, что, с 1ельк) повышения то--|ности и быстродействия, а та-кже расширения фуикил-шнальных воэмо- юностей, он снабжен регистром памяти, вхо-ды которого соединоны с выходами реверсивного счетчика, выходы - с входами допей совнадения, а вход управления 1записью кода - с выходом дел1ггеля оиорн-ой частоты.

2. Частотомер по п. 1, отличающийся тем,

что, с целью устранения влияния на результат измерения пульсацнй измеряемой частоты, он снабжен. триг-геро.м и ключом, выход которого соедилеп с входОМ хиравле;;:) записью кода регистра цамятн, вход - с источНИКОМ си-гнала, модулирующего- 3л1еря©мую частоту, и первым входом Tpiirrepa, второй вход которого подключай К выходу делителя оиор1ной частоты, а выход - к управляющему входу ключа. 3. Частотомер но п. 1, отличающийся тем, что, с целью повышения быстродействия и получепня у-Множйнио-го значения входной частоты, он снабже н триггером и ключо:м, выход которого соедшнеи с входом управления заннсью

кода perHCTpia памяти, вход - с входной клеммой,.старш-ими разрядами реверсивного счетч-ика и первым входом триггера, второй вход которого подключен к выходу делителя опорной частоты, а выход - к управляюнхему входу ключа.

Фиг 1

М

Jn-fx

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| Устройство для измерения частоты | 1983 |

|

SU1170373A1 |

| Цифровой частотомер | 1985 |

|

SU1247771A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Цифровой частотомер мгновенных значений | 1990 |

|

SU1783451A1 |

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ И ФАЗЫ ЭЛЕКТРИЧЕСКИХ КОЛЕБАНИЙ | 1973 |

|

SU375575A1 |

| Управляемый делитель частоты следования импульсов | 1983 |

|

SU1088136A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

Даты

1973-01-01—Публикация