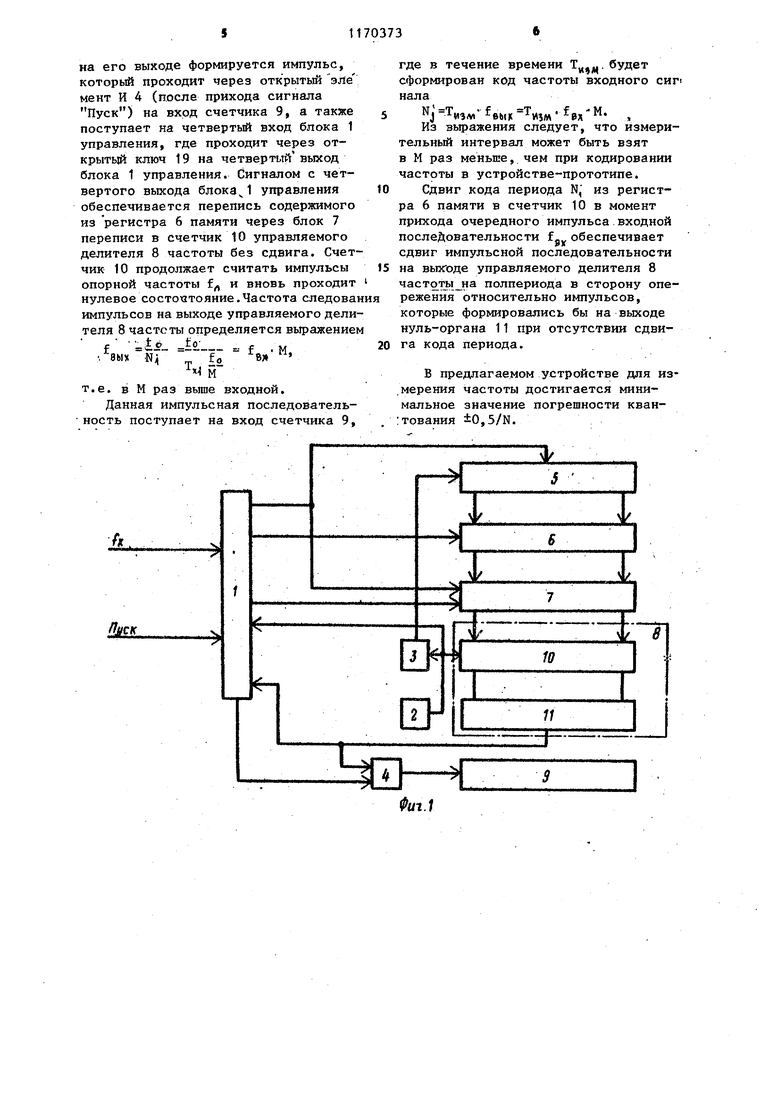

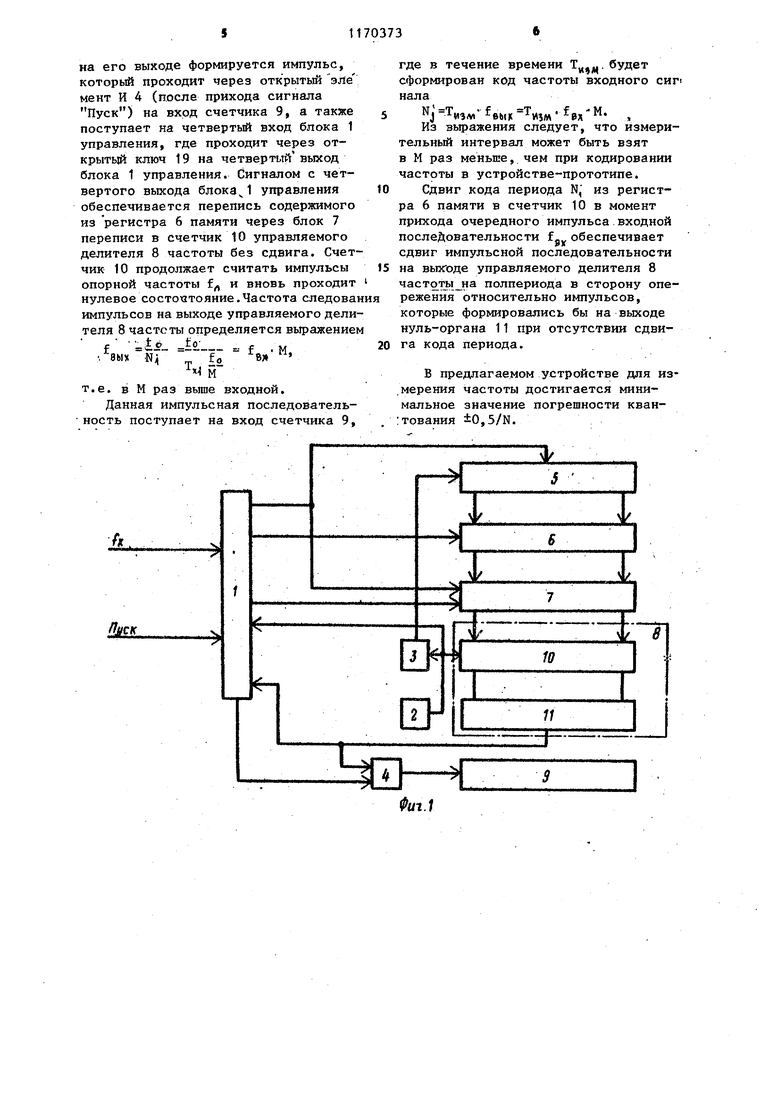

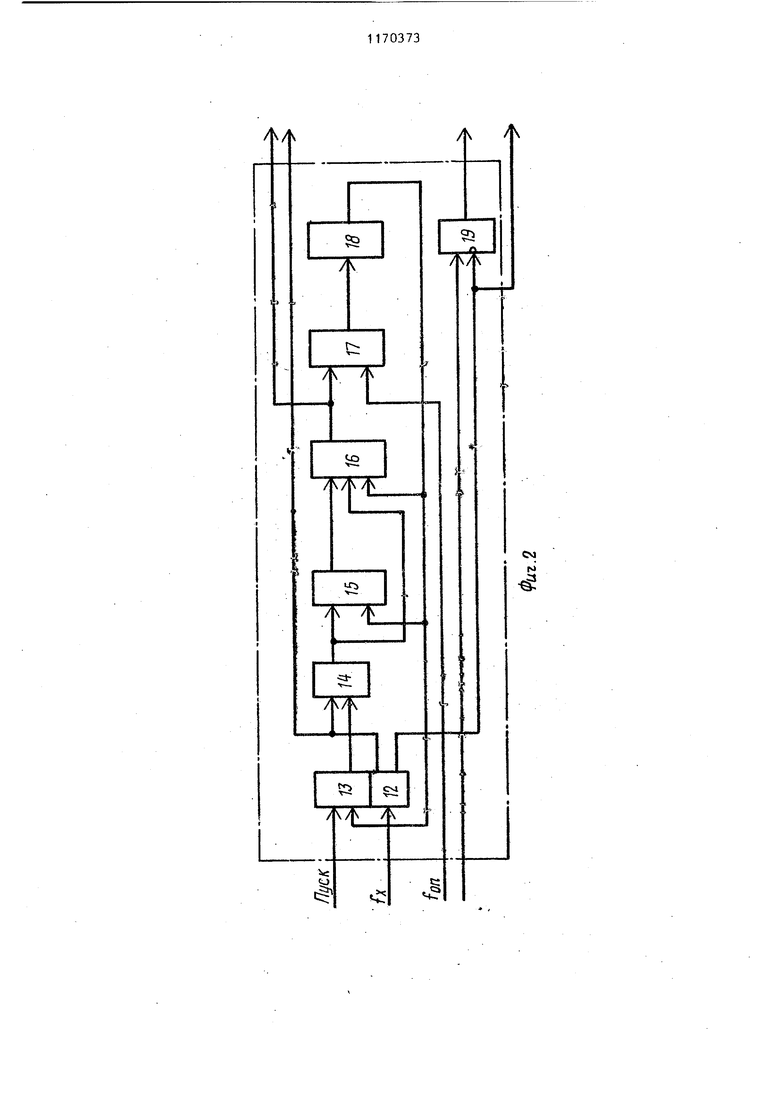

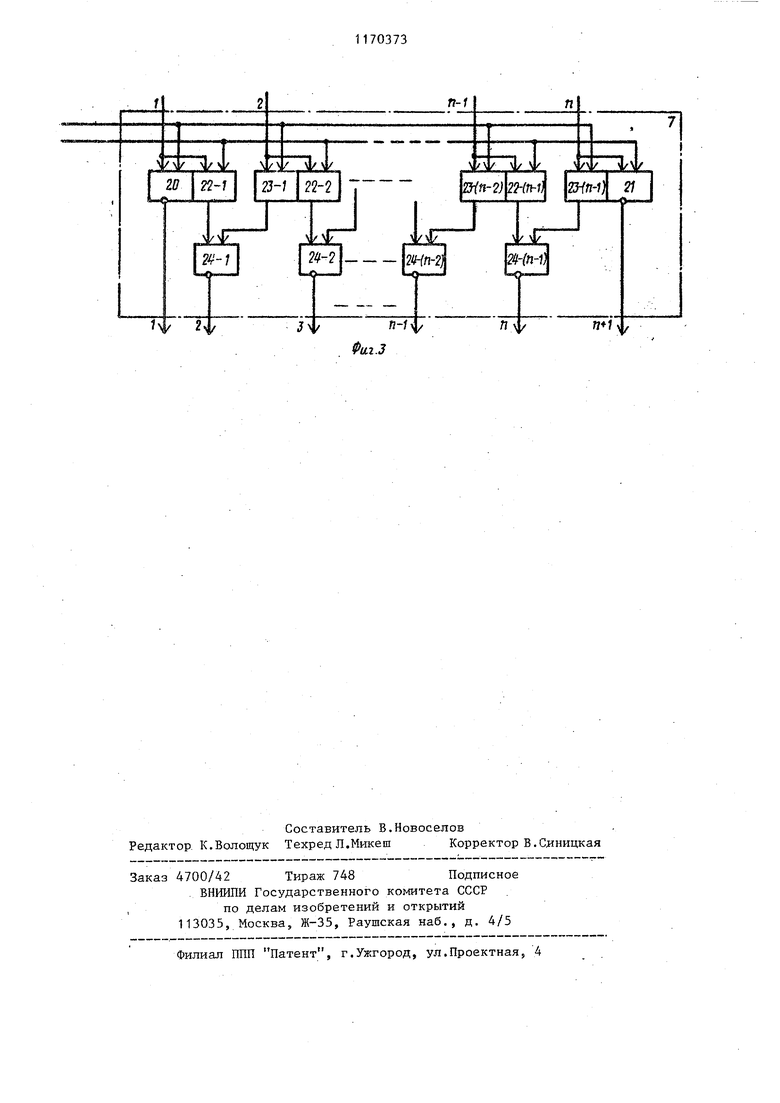

Изобретение относится к информа, ционно-измерительной и вычислительной технике и может быть использова при построении быстродействующих пр образователей частоты следования им пульсов в код. Цель изобретения - повьппение точ ности измерения частоты инфранизкочастотных и низкочастотных сигналов путем уменьшения погрешности кванто вания. На фиг. 1 представлена структурная схема устройства для измерения частоты; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока переписи. Устройство (фиг. 1) содержит . ;блок 1 управления, генератор 2 сов эталонной частоты, делитель 3 частоты, элемент И 4, счетчик 5 импульсов, регистр 6 памяти, блок 7 переписи, управляемый делитель 8 частоты, счетчик 9 импульсов. При этом, вход устройства подключен к пе вому входу блока 1 управления, первый выход которого связан с вторым входом элемента И 4, второй вход которого объединен с выходом управляемого делителя 8 частоты и подклю чен к четвертому входу блока 1 упра ления, второй вход которого подключен к шине Пуск., третий вход подключен к выходу генератора 2 опорно частоты, связанному с входом делите ля 3 частоты и счетным входом управ ляемого делителя 8 частоты, четвертьй вход подключен к объединенным между собой выходом управляемого де лителя 8 частоты и первым входом элемента И 4, второй вход которого связан с первым выходом блока 1 упра ления, второй выход которого подключен к синхровходу регистра памят третий выход связан с первым управлякшрм входом блока 7 переписи и установочным входом первого счетчика 5, информационные выходы которог подключены к информационным входам регистра 6 памяти, п информационных выходов которого подключены к входам блока 7 переписи, второй управляюпщй вход которого соединён с четвертым управляиицим выходом бло ка 1 управления, причем (п+1) выходов блока 7 переписи подключены к (п+1) информационным входам управ ляемого делителя 8 частоты, а выход импу 732 :элемента И 4 связан со счетным входом второго счетчика 9. Управляемый делитель частоты, структурная схема которого представлена на фиг. 2, содержит счетчик 10 и нуль-орган 11, при этом (п+1) информационные входы счетчика 10 связаны с информационным входом управляемого делителя 8 частоты, счетный вход которого соединен со счетным входом счетчика 10, выходы которого подключены к входам нуль-органа 11, выход которого связан с выходом управляемого делителя 8 частоты. Структурная схема блока 1 управления представлена на фиг. 2. Блок 1 |управления содержит формирователь 12 импульсов, триггер 13, ключ 14, , триггеры 15 и 16, ключа 17, делитель 18, ключ 19. Первый вход блока 1 управления соединен с входом формирователя 12, первый выход которого подключен одновременно к второму выходу блока 1 управления и к первому входу ключа 14, второй вход которого соединен с выходом триггера 13, выход ключа 14 соединен одновременно с синхровходами триггеров 16 и 15, выход последнего подключен к информационному входу триггера 16, вькод которого соединен одновременно с первым выходом блока 1 управления и с первым входом ключа 17, второй вход которого подключен к третьему входу блока 1 управления, четвертый вход которого соединен с первым входом ключа 19, выход которого подключен к третьему выходу блока 1 управления, четвертый выход которого соединен с инверсным входом ключа 19 и подключен к второму выходу формирователя 12, выход ключа 17 соединен с входом делителя 18, выход которого подключен одновременно к второму установочному входу триггера 13, к установочным входам триггеров 15 и 16, первый установочный вход триггера 13 соединен с вторым входом блока управления. Структурная схема блока переписи 7 представлена на фиг. 3. Блок переписи 7 содержит элементы И-НЕ 20 и 21, группу элементов И 22-1...22-(п-1), группу элементов И 23-1...23-(п-1), группу элементов lillH-HE 24-1...24(п-1). Первый информационный вход блока 7 переписи подключен одновременно к первым входам элементов И-НЕ 20 и И 22-1, 2...(п-1) информационные входы подключены соответственно к пе вым входам элементов И 22-2...22(п-1), а также элементов И 23-1...23 (п-2), п-й информационный вход соединен с первыми входами элементов И 23-(п-1) и И-НЕ 21, выходы элементов И 22-1...22-(п-1), И 23-1... 23(п-1) подключены к первым и вторым входам элементов ИЛИ-НЕ 24-1...24(п-1) соответственно, выходы последних связаны с 2...П информационными выходами блока переписи 7, I и (п+1) выходы которого подключены к выходам элементов И-НЕ 20 и И-НЕ 21, первый управляющий вход блока 7 переписи со динен с вторыми входами элементов И-НЕ 20, И 23-1...23-(п-1), второй управляющий вход соединен с вторыми входами элементов И 22-1...2(п-1), И-НЕ 21. Устройство для измерения частоты работает следующим образом. По сигналу Пуск взводится триггер 13 блока 1 управления, разрешающий сигнал с выхода которого открыва ет ключ 14. В момент поступления первого после сигнала Пуск импульса измеряемой частоты f по его переднему фронту на первом выходе формирователя 12 формируется сигнал, который проходит через открытьш ключ 14 и взводит триггер 15. Одновременно данный импульс поступает на вход синхронизации регистра 6 памяти, обеспечивая перепись содержимо го из счетчика 5. По заднему фронту входного импульса f формирователь 12 формрфует импульс, который поступает на инверсный вход ключа 19 и закрывает его. Кроме того, импульс с второго выхода формирователя поступает на установочный вход счетчи. ка 5 (устанавливая его в нулевое состояние) и на первый управляющий вход блока 7 переписи, обеспечивая перепись содержимого регистра 6 памяти в счетчик 10 управляемого делителя 8 частоты со сдвигом на один .разряд в сторону старших разрядов. Собственно сам процесс кодирования начинается в момент прихода второго импульса входной последовательности fX. При этом по переднему фронту импульса fx происходит перевод триггера 16 в противоположное состояние (на рабочем входе которого выставлена логическая единица с выхода триггера 15). Разрешающий сигнал с выхода триггера 16 открывает ключа 17 и элемент И 4. Импульсная последовательность опорной частоты через открытый ключ 17 начинает, поступать на вход делителя 18., пересчетный коэффициент которого выбирается таким, чтобы период следования импульсов на выходе делителя соответствовал заданному (выбранному) измерительному интервалу N, . ол период следования импульсов опорной частоты f ; N - коэффициент пересчета делителя. Б момент формирования импульса на выходе делителя 18 производится сброс в исходное состояние триггеров 13, 15 и 16. Триггер 16 при этом закрьшает элемент И 4. Импульсная последовательность с выхода генератора 2 опорной частоты поступает на счетный вход счетчика 10 управляемого делителя 8 частоты и на вход делителя 3 частоты. Как рассматривалось выше, пе1)иод следования управляющих импульсов, поступающих на соответствующие входы счетчика 5, регистра 6 памяти и блока 7 переписи, определяется периодом следования импульсов входной последовательности fj(. При этом к моменту окончания (текущего периог да входной последовательности) в счетчике 5 будет сформирован кодовый эквивалент данного периода . М - коэффициент деления делит еля 3 частоты. В момент времени, соответствующий ; окончанию Т , блок 1 управления фор мирует управляющие сигналы, которые обеспечивают следующее продвижение информации. Код N| из счетчика 5 переписывается в регистр 6 памяти, затем счетчик 5 обнуляется, а содержимое регистра 6 памяти переписывается со сдвигом на 1 разряд в сторону старших разрядов в инверсном коде в счетчик 10 управляемого делителя 8 частоты. Счетчик 10 считает поступающие на его счетный вход импульсы опорной частоты, нуль-орган 11 фиксирует момент перехода счетчика 10 через нулевое состояние. При этом. на его выходе формируется импульс, который проходит через открытый эле мент И 4 (после прихода сигнала Пуск) на вход счетчика 9, а также поступает на четвертьй вход блока 1 управления, где проходит через открытый ключ 19 на четвертыйвыход блока 1 управления. Сигналом с четвертого выхода блока 1 управления обеспечивается перепись содержимого из регистра 6 памяти через блок 7 переписи в счетчик 10 управляемого делителя 8 частоты без сдвига. Счетчик 10 продолжает считать импульсы опорной частоты f и вновь проходит нулевое состоатояние. Частота следова импульсов на выходе управляемого дели теля 8 частоты определяется вьфажение - it о. f о;.. f , м гSS .«. Г fo « 8ЫХ Е Ч-1 н т.е. в М раз вьппе входной. Данная импульсная последовательность поступает на вход счетчика 9, где в течение времени Tj,,. будет сформирован код частоты входного сиг нала ,-feb,Tj,,.fp,-M. , Из выражения следует, что измерительный интервал может быть взят в М раз меньше, чем при кодировании частоты в устройстве-прототипе. Сдвиг кода периода N, из регистра 6 памяти в счетчик 10 в момент прихода очередного импульса входной последовательности „ обеспечивает сдвиг импульсной последовательности на вьпсоде управляемого делителя 8 частоть1 на полпериода в сторону опережения относительно импульсов, которые фop шpoвaлиcь бы на выходе нуль-органа 11 при отсутствии сдвига кода периода. В предлагаемом устройстве для измерения частоты достигается минимальное значение погрешности кван;тования iO,5/N,

Cvi

го

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения частоты | 1988 |

|

SU1550434A1 |

| Умножитель частоты | 1987 |

|

SU1448394A2 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Преобразователь частоты в код | 1977 |

|

SU746922A1 |

| Генератор сигналов сложной формы | 1980 |

|

SU983692A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| УСТРОЙСТВО АВТОВЫБОРА ДИСКРЕТНОГО КАНАЛА | 2011 |

|

RU2488222C1 |

| Устройство для измерения скорости изменения частоты | 1989 |

|

SU1620952A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ, содержащее блок управления, два счетчика импульсов, элемент И, управляемый делитель частоты, генератор импульсов эталонной частоты, ш 1ходом соединенный с входом делителя частоты, отличающеес-я тем, что, с целью повьшения точности измерения частоты, в него введены последовательно соединенные регистр памяти и блок перепиЬи, при этом первый вход блока управления подключен к входной шине устройства, второй вход - к шине пуска, третий вход к выходу генератора опорной частоты, четвертый вход подключен к выходу управляемого делителя частоты и к первому входу элемента И, второй вход которого подключен к первому выходу блока управления, второй выход которого соединен с синхровходом регистра памяти, третий выход подключен к первому управляющему входу блока переписи и к установочному входу первого счетчика, информащюнные выходы которого подключены к информационным входам регистра паS мяти, второй управлякйций вход блока переписи подключен к четвертому выходу блока управления, а информационные выходы блока переписи соединены 1с информационными входами управляемого делителя частоты, счетный вход .которого подключен к выходу генерато-, ра импульсов опорной частоты, выход элемента И соединен с входом второго счетчика. СО со

| Шляндин В.М | |||

| Цифровые измерительные преобразователи и приборы | |||

| М., 1973, с | |||

| Катодное реле | 1918 |

|

SU159A1 |

| Цифровой измеритель инфранизких и низких частот | 1976 |

|

SU573768A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-07-30—Публикация

1983-06-24—Подача