1

Изобретение относится к вычислительной технике и предназначено для преобразования кодов.

Известны преобразователи двоичного кода в циклический с постоянным числом п единиц Из р, в которых лри используются сложные логические схемы, а при - диодные Матрицы большой размерности; кроме того, количество единиц п в кодовой группе в таких устройствах не может быть изменено, что ограничивает их функциональные возможности.

Предлагаемое устройство, с целью его упрощения, содержит преобразователь «код- аналог и логическую нороговую схему, выход которой соединен со входом служебного регистра, вход преобразователя «код - аналог соединен с выходом счетного ; -разрядИого регистра, а выход - со входом логической пороговой схемы, выход генератора такТовых импульсов соединен со- входом счетного р-разрядного регистра, выход которого соединен со входом блока промежуточной памяти.

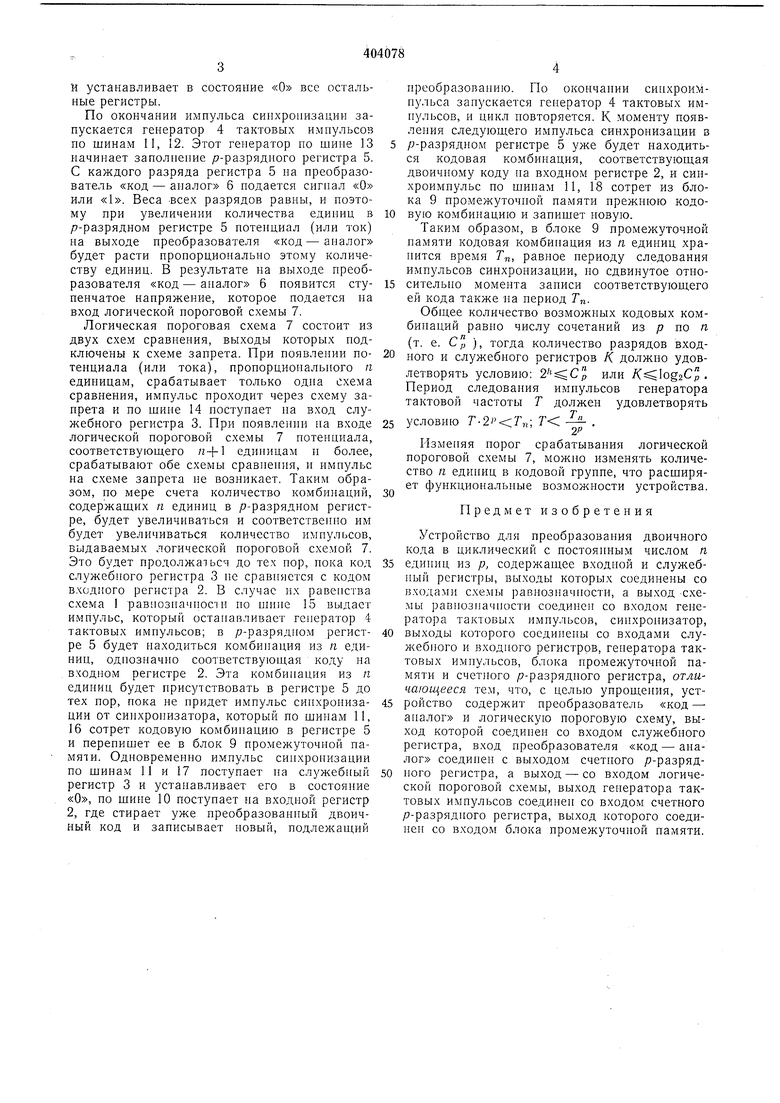

На чертеже представлена схема предлагаемого устройства.

На схему 1 равнозначности подаются сигналы с входного регистра 2 и со служебного регистра 3, имеющих одинаковое количество К разрядов. Схема 1 равнозначности управ2

ляет генератором 4 тактовых импульсов, который заполняет счетный р-разрядный регистр 1. К выходу счетного р-разрядного регистра 5 подключен преобразователь «код - аналог 6, напряжение (или ток) на выходе которого пропорционально количеству единиц в кодовой комбинации р-разрядного регистра 5. Выход преобразователя «код--аналог подключен к логической пороговой схеме 7, которая генерирует импульс только в том случае, если на ее входе присутствует потенциал, соответствующий п единицам в /9.-разрядном регистре 5. Импульсы с логической пороговой схемы 7 подаются на вход служебного регистра 3 до тех нор, пока его код не сравняется с кодом регистра 2... В момент равенства этих кодов схема 1 равнозначности останавливает генератор 4, и р-разрядный регистр больще не заполняется. Через время, определяемое синхронизатором 8, перепишется код из регистра 5 в блок 9 промежуточной памяти, все узлы установятся в исходное состояние, запишется новый код в регистр 2, и цикл начнется снова. На входной регистр 2 коды, подлежащие преобразованию, ноступают с периодом Г„. С этим же периодом синхронизатор генерирует импульсы синхронизации, которые разрешают запись кода во входной регистр 2 по шине 10 И устанавливает в состояние «О все остальные регистры. По окончании импульса синхронизации запускается генератор 4 тактовых импульсов по шинам 11, 12. Этот генератор но шине 13 начинает заполнение /5-разрядного регистра 5. С каждого разряда регистра 5 на преобразователь «код - аналог 6 нодается сигнал «О или «1. Веса -всех разрядов равны, и поэтому при увеличении количества единиц в 7-разрядном регистре 5 потенциал (или ток) на выходе преобразователя «код - аналог будет расти пронорционально этому количеству единиц. В результате на выходе преобразователя «код - аналог 6 появится ступенчатое напряжение, которое подается на вход логической пороговой схемы 7. Логическая пороговая схема 7 состоит из двух схем сравнения, выходы которых нодключены к схеме запрета. При появлении потенциала {или тока), пропорциоиального п единицам, срабатывает только одна схема сравнения, импульс проходит через схему запрета и по шипе 14 поступает на вход служебного регистра 3. При появлении на входе логической пороговой схемы 7 потенциала, соответствующего единицам и более, срабатывают обе схемы сравнения, и импульс на схеме запрета не возникает. Таким образом, но мере счета количество комбинаций, содержаших п единиц в р-разрядном регистре, будет увеличиваться и соответственно им будет увеличиваться количество имнульсов, выдаваемых логической пороговой схемой 7. Это будет продолжаться до тех нор, пока код служебного регистра 3 не сравняется с кодом входного регистра 2. В случае их раве 1ства схема 1 равнозначности по нише 15 выдает импульс, который останавливает генератор 4 тактовых импульсов; в уО-разрядном регистре 5 будет находиться комбинация из п единиц, однозначно соответствующая коду на входном регистре 2. Эта комбииация из п единиц будет присутствовать в регистре 5 до тех нор, пока не нридет нмпульс синхронизации от синхронизатора, который по шинам 11, 16 сотрет кодовую комбииацию в регистре 5 и перепишет ее в блок 9 промежуточной памяти. Одновременно импульс синхронизации по шина.м И и 17 поступает на служебный регистр 3 и устанавливает его в состояние «О, но шине 10 поступает па входной регистр 2, где стирает уже преобразованный двоичный код и записывает повый, подлежащий нреобразованию. По окончании сипхроимну.тьса запускается генератор 4 тактовых имнульсов, и цикл повторяется. К моменту появления следующего импульса синхронизации в /J-разрядном регистре 5 уже будет находиться кодовая комбинация, соответствующая двоичному коду на входном регистре 2, и синхроимпульс по шинам 11, 18 сотрет из блока 9 промежуточной памяти прежнюю кодовую комбинацию и запишет новую. Таким образом, в блоке 9 промежуточной намяти кодовая комбинация из п единиц хранится время Тп, равное периоду следования импульсов синхронизации, но сдвинутое относительно момента записи соответствующего ей кода также на период ТпОбщее количество возможных кодовых комбинаций равно числу сочетаний из р по ft (т. е. с }, тогда количество разрядов входного и служебного регистров /С должно удовлетворять условию: или K logzCp . Период следования импульсов генератора тактовой частоты Т должен удовлетворять условию ,г; 7 порог срабатывания логической пороговой схемы 7, можно изменять количество п единиц в кодовой группе, что расширяет функциональные возможности устройства. Предмет изобретения Устройство для преобразования двоичного кода в циклический с постоянным числом п единиц из р, содержащее входной и служебный регистры, выходы которых соединены со входами схемы равнозначности, а выход схемы равнозначности соединен со входом генератора тактовых импульсов, синхронизатор, выходы которого соединены со входами служебного и входного регистров, генератора тактовых имнульсов, блока нромежуточной памяти и счетного / -разрядпого регистра, отличающееся тем, что, с целью упрощения, устройство содержит преобразователь «код - аналог и логическую пороговую схему, выход которой соединен со входом служебного регистра, вход преобразователя «код-апалог соединен с выходом счетного р-разрядного регистра, а выход - со входом логической пороговой схемы, выход генератора тактовых импульсов соединен со входом счетного /7-разрядпого регистра, выход которого соединен со входом блока промежуточной намяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь моментов времени в код | 1979 |

|

SU855995A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| Комплекс декаметровой радиосвязи | 2020 |

|

RU2737763C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для воспроизведения мно-гОКАНАльНОй МАгНиТНОй зАпиСи | 1979 |

|

SU836662A1 |

| Способ передачи и приема дискретных сообщений в комплексе декаметровой радиосвязи | 2020 |

|

RU2743233C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1982 |

|

SU1115219A1 |

Авторы

Даты

1973-01-01—Публикация