Изобретение относится к оиластл авто.матики н вычислительной те.хники и предназначено для преобразования последовательны.х двоичных кодов в параллельные.

Известны преобразователи последовательного кода в параллельный, содержащие регистр сдвига, генератор тактовых импульсов и блок формирования сигиала «конец кодовой комбинации, вход которого соединен с выходом генератора тактовых импульсов, дешифратор, коммутатор, триггер режима, триггер выбора комбииации, счетный триггер и элемент задержки.

Предложеииый преобразователь отличается тем, что выход блока формирования сигнала «коиец кодовой комбииации соединен с унравляющнм входом счетного триггера и через элемент задержки - со входами триггера режима и триггера выбора комбииации, выход которого соединен со входами счетного триггера и дешифратора; выход триггера режима соединен с управляющими входами коммутатора и дешифратора, счетиый вход счетного триггера соединеи с выходом генератора тактовых импульсов, выход счетного триггера через коммутатор соедииеи со входом регистра сдвига, выход которого соединеи со входом дешнфратора.

Это позволяет расширить область применения устройства за счет возможности контроля его работоспособиостн и исиользовання его, таким образом, в системах с повышенными требованиями к надежности фуикциоиирования.

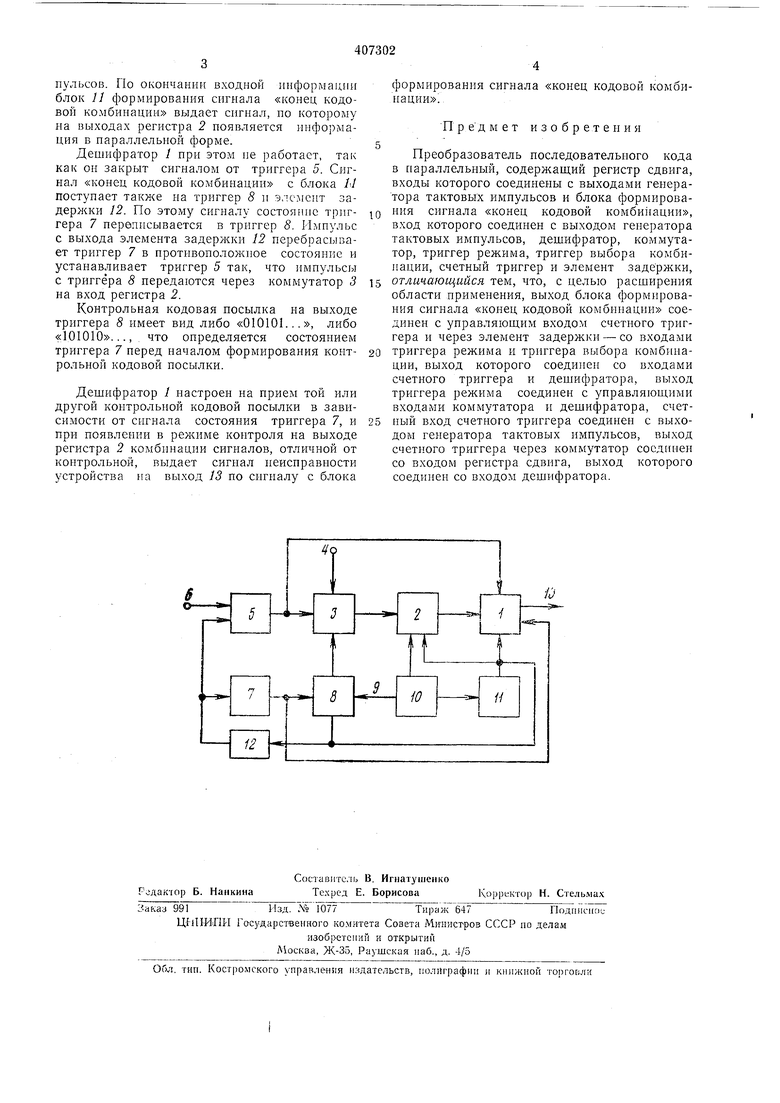

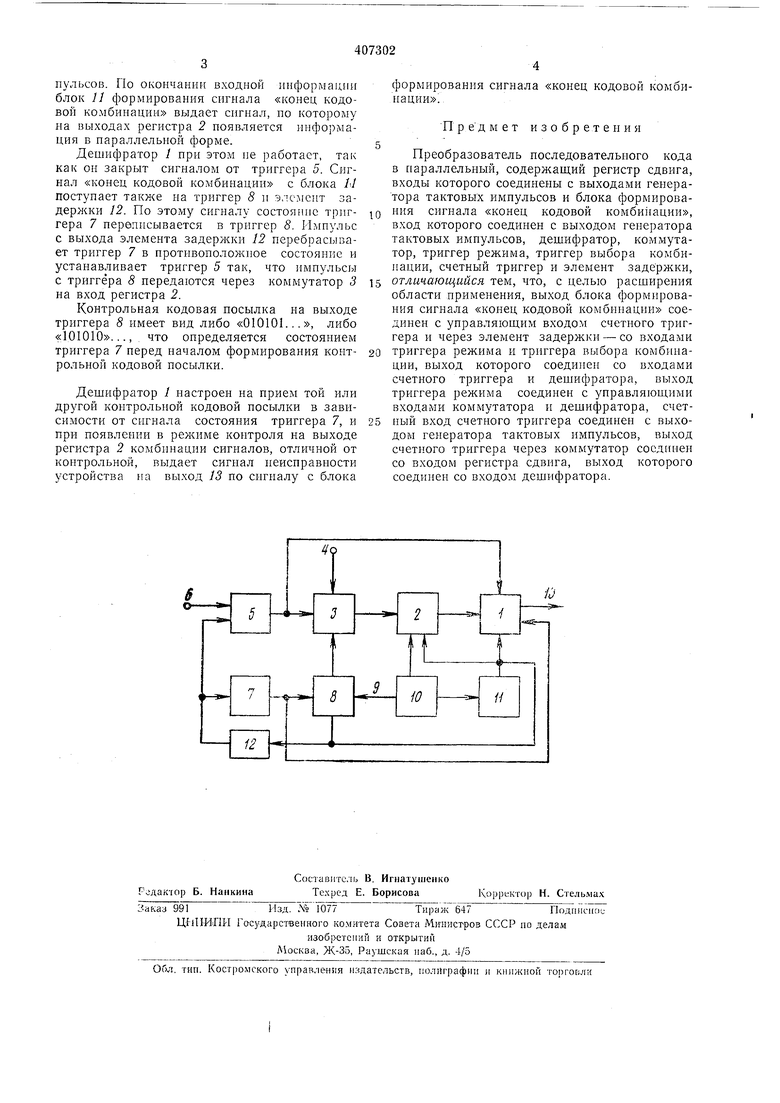

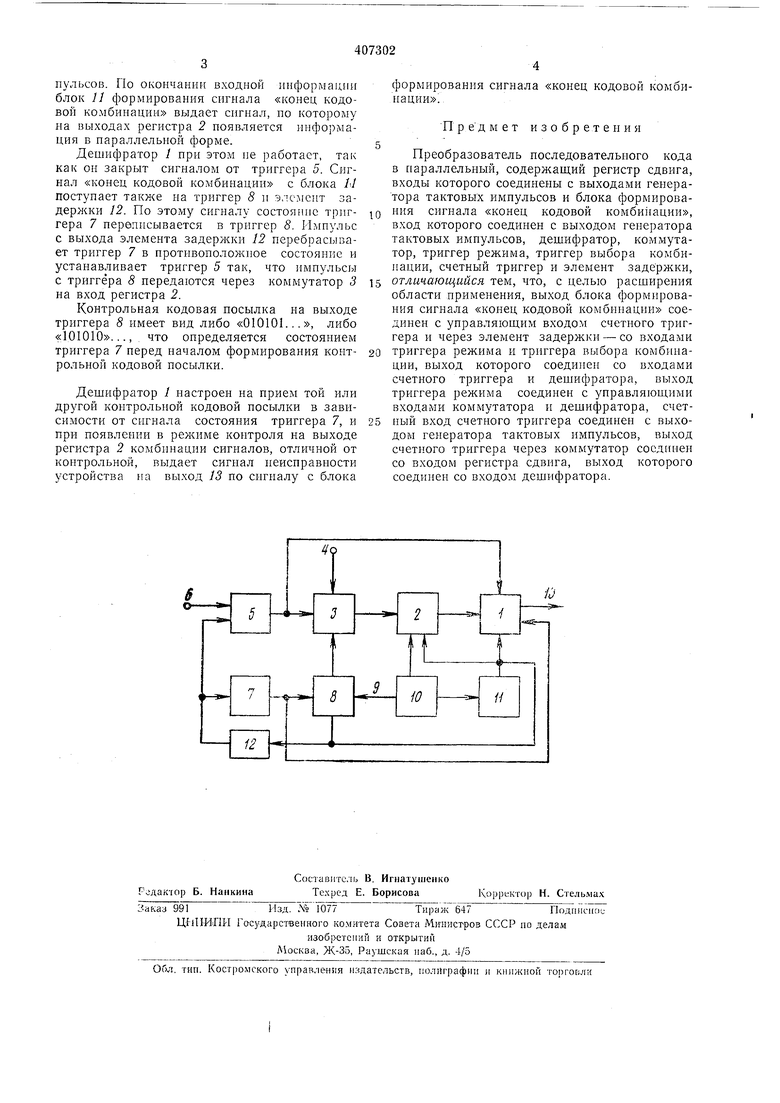

Схема устройства изображена иа чертеже. Устройство содержит дешифратор / (для дешифрации коитрольных состояиий устройства), регистр сдвига 2, коммутатор 3 со входом 4 для подачи входной информации, триггер режима 5 со входом 6 для подачи сигнала «начало сообщения, триггер 7 выбора комбинации, счетный триггер 8 со счетны.м входом 9, генератор 10 тактовых импульсов, блок // формирования сигиала «конец кодовой комбинации, элемент задержки 12 и контрольный выход 13.

Коммутатор 3 коммутирует информационный вход регистра сдвига 2 либо на вход 4, через который на устройство передается нреобразуемый последовательный код, либо на выход счетного триггера 6, в зависимости от состояния триггера режима 5.

Устройство работает следующим образом. При лодаче сигиала «начало сообщения

на вход 6 триггера 5 коммутатор 3 переключается иа прием кодовой комбинации со входа 4, и информация пропускается на вход регистра сдвига 2. Импульсы входиой ииформации запоминаются в регистре сдвига при помои1,и нмиульсов генератора 10 тактовых им

пульсов. По окончании входной ннформакин блок // формирования сигнала «конец кодовой комбинации выдает сигнал, по которому иа выходах регистра 2 появляется информация в иараллельной форме.

Дешифратор I ири этом не работает, так как он закрыт сигналом от триггера 5. Сигнал «конец кодовой комбинации с блока Ы поступает также на триггер 8 и элемент задержки 12. По этому сигналу состояние триггера 7 переписывается в триггер 8. Импульс с выхода элемента задержки 12 перебрасывает триггер 7 в протнвоположпое состояние и устанавливает триггер 5 так, что импульсы с триггера 8 передаются через коммутатор 3 на вход регистра 2.

Контрольная кодовая посылка на выходе триггера 8 имеет вид либо «010101..., либо «101010..., что определяется состоянием триггера 7 перед началом формирования контрольной кодовой посылки.

Дешифратор / настроен на прием той или другой контрольной кодовой посылки в зависимости от сигнала состояния триггера 7, и при появлении в режиме контроля на выходе регистра 2 комбинации сигналов, отличной от контрольной, выдает сигнал неисправности устройства на выход 13 по сигналу с блока

формирования сигнала «конец кодовой комбинации.

П р е д м е т изобретения

Преобразователь последовательного кода в параллельный, содержаш,ий регистр сдвига, входы которого соединены с выходами генератора тактовых импульсов и блока формирования сигнала «конец кодовой комбинации, вход которого соединен с выходом генератора тактовых импульсов, дешифратор, коммутатор, триггер режима, триггер выбора комбинации, счетный триггер и элемент задержки, отличающийся тем, что, с целью расширения области применения, выход блока формирования сигнала «конец кодовой комбннацин соединен с управляющим входом счетного триггера и через элемент задержки - со входами 0 триггера режима и триггера выбора комбииации, выход которого соединен со входами счетного триггера и дешифратора, выход триггера режима соединен с управляющими входами коммутатора и дешифратора, счетный вход счетного триггера соединен с выходом генератора тактовых импульсов, выход счетного триггера через коммутатор соединен со входом регнстра сдвнга, выход которого соединен со входом дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| Устройство для записи и анализа циклограмм дискретных блоков | 1985 |

|

SU1313221A1 |

| Устройство для формирования знаков на экране телевизионного индикатора | 1980 |

|

SU940212A2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

Авторы

Даты

1973-01-01—Публикация