(21)4328426/24-24

(22)05.10.87

(46) 28.02.90. Бкш. W 8

(72) Л.И.Севастов и В.В.Кузнецов

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 119002, кл. Н 03 М 9/00, 1983.

Авторское свидетельство СССР 1270897, кл. Н 03 М 9/00, 1984.

(54)ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обмена информацией с контролем передаваемого кода. Целью изобретения является повышение достоверности преобразуемого кода. Преобразователь содержит генератор 1 импульсов, первый и второй счетчики 2 и 3, схему 4 сравнения, коммутатор 5, блок 6 памяти, первый - третий элементы И-НЕ 7-9, первый и второй регистры 10 и 11 i сдвига, дешифратор 12 нуля, первый - третий триггеры 13-15, элемент ИЛИ 16, первую и вторую группы элементов РАВНОЗНАЧНОСТЬ 17 и 18, первый и второй генераторы 19 и 20 одиночных импульсов, первый и второй элементы 21 и 22 задержки, элемент НЕ 23, тактовый и информационные входы 24 и 25, входы 26-28 пуска, записи и сбро- а са, информационный 29 и контрольный 30 выходы. 1 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1270897A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Устройство для тестового диагностирования | 1982 |

|

SU1045230A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Устройство для регистрации временных и информационных процессов | 1986 |

|

SU1363258A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обмена информацией с контролем передаваемого кода. Целью изобретения является повышение достоверности преобразуемого кода. Преобразователь содержит генератор 1 импульсов, первый и второй счетчики 2 и 3, схему 4 сравнения, коммутатор 5, блок 6 памяти, первый - третий элементы И-НЕ 7-9, первый и второй регистры 10 и 11 сдвига, дешифратор 12 нуля, первый - третий триггеры 13-15, элемент ИЛИ 16, первую и вторую группы элементов РАВНОЗНАЧНОСТЬ 17 и 18, первый и второй генераторы 19 и 20 одиночных импульсов, первый и второй элементы 21 и 22 задержки, элемент НЕ 23, тактовый и информационные входы 24 и 25, входы 26-28 пуска, записи и сброса, информационный 29 и контрольный 30 выходы. 1 ил.

ся

4 Ч О Ч

Од

3154

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обмена информацией с контролем передаваемого кода.

Целью изобретения является повышение достоверности преобразуемого кода.

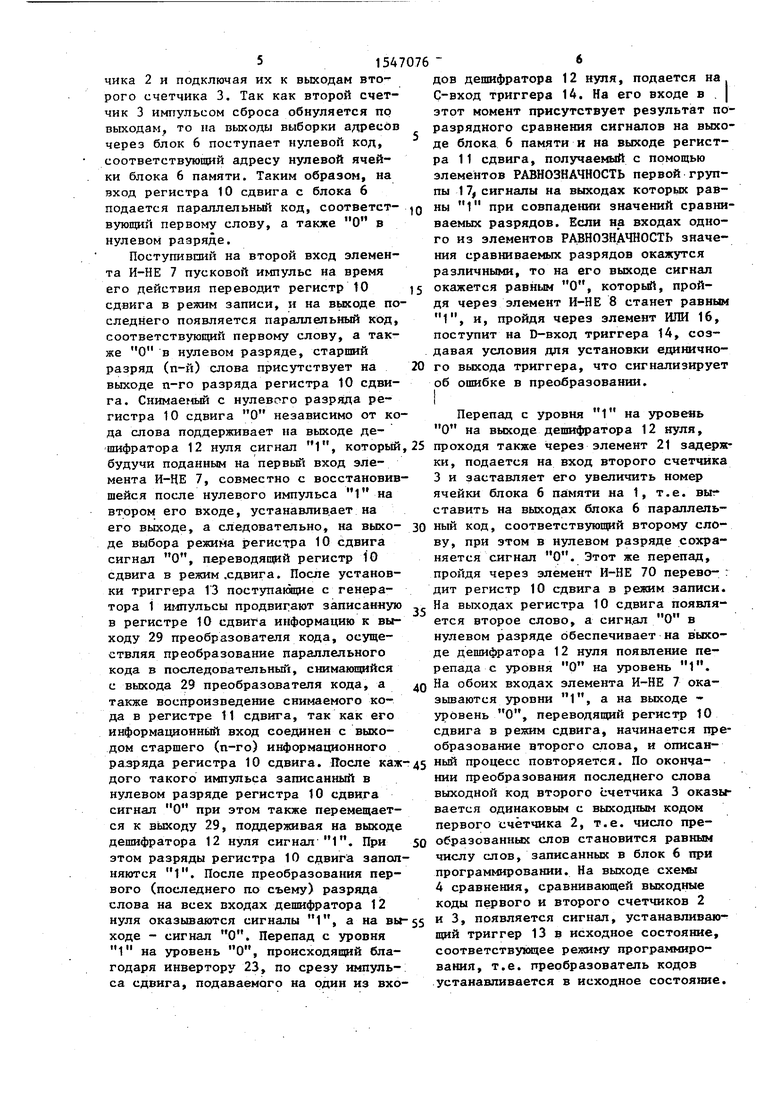

На чертеже представлена функциональная схема преобразователя.

Преобразователь содержит генератор 1 импульсов, первый 2 и второй 3 счетчики , схему 4 сравнения, коммутатор 5, блок 6 памяти, первый - тре JTHU элементы И-НЕ 7, 8 и 9, первый 10 и второй 11 регистры сдвига, дешифратор 12 нуля, первый - третий триггеры 13, 14 и 15, элемент ИЛИ 16, первую 17 и вторую 18 группы элементов РАВНОЗНАЧНОСТЬ, первый 19 и второй 20 генераторы одиночных импульсов, первый 21 и второй 22 элементы задержки, элемент НЕ 23, тактовый 24 и информационные 25 входы, входы 26, 27 и 28 пуска, записи и сброса, информационный 29 и контрольный 30 выходы.

Преобразователь работает следующим

образом.

Перед программированием на вход 28 сброса преобразователя подается сигна сброса на первый счетчик 2 и триггер 13, заставляя последний переключаться на режим программирования, при кото

ром сигнал с его единичного выхода, п подаваемый на вход коммутатора 5, заставляет последний подключить выходы первого счетчика 2 к входам выборки адресов блока 6 памяти, а сигнал с нулевого выхода триггера 13 отключает выходы второго счетчика 3 от входом выборки адресов блока 6 и заставляет генератор 1 прекратить выдачу импульсов. Программирование заключается в том, что на входы 25 преобразователя хода подается n-разрядное слово в па реллельном коде, которое при подаче на вход 27 записи сигнала записи записывается в ячейку блока 6 с нулевым адресом, причем в ьулевой разряд блока 6 записывается О. По переднему фронту сигнала записи генератор 20 генерирует одиночный импульс, сбрасывающий триггеры 14 и 15, а элемен- том 22 задержки этот одиночный импуль сдвигается на время, достаточное для завершения переходных процессов в блоке 6 памяти, второй группе 18 элемен

0

тов РАВНОЗНАЧНОСТЬ и элементе И-НЕ 9 и подается на С-вход триггера 15, вырабатывающего на своем единичном выходе сигнал достоверности произведенной записи: при поразрядном сравнении сигналов, присутствующих на входах и выходах блока 6 памяти, осуществляемом двухвходовыми элементами РАВНОЗНАЧНОСТЬ второй группы 18 элементов РАВНОЗНАЧНОСТЬ, на выходах последних в случае правильности произведенной за- лнси окажутся 1, которые, пройдя (врез элемент И 9, подадут сигнал О на D-вход триггера 15, единичный выход которого окажется равным О, в случае неправильной произведенной записи по крайней мере на одном из выходов двухвходовых элементов второй группы 18 элементов РАВНОЗНАЧНОСТЬ окажется О, что послужит причиной

5

0

40

45

50

подачи на D-вход триггера 15 1, л единичный выход его установится в ej +- чичное положение. При подаче в процессе программирования на вход первого счетчика 2 импульса последний увеличивает свой выходной код на единицу, который через коммутатор 5 подается на входы выборки адресов блока 6.

Таким образом, блок 6 подготавливается для записи второго слова в ячейку с адресом, равным единице. Запись второго слова в блок 6 и определение

достоверности записи производятся аналогично описанному, причем в нулевой разряд блока 6 снова записывается О Таким образом, массив данных в параллельном коде, состоящий из данного числа слов, записывается в ячейки блока 6, причем в нулевые разряды последнего всегда записывается О независимо от кодовой комбинации, состав- шяющей информационное слово. После записи в блок 6 последнего слова массива данных на вход первого счетчика подается импульс и преобразователь кода оказывается готовым к преобразованию записанного массива данных.

Для запуска режима преобразования на вход 26 преобразователя подается отрицательтлй импульс, который поступает также на второй вход элемента И-НЕ 7, на сброс второго счетчика 3 и на вход установки в 1 триггера 13, логические сигналы на выходах которого, подаваемые на вторые входы коммутатора 5, изменяются на противоположные, отключая входы выборки адресов блока 6 от выходов первого счетчика 2 и подключая их к выходам второго счетчика 3. Так как второй счетчик 3 импульсом сброса обнуляется по выходам, то на выходы выборки адресов через блок 6 поступает нулевой код, соответствующий адресу нулевой ячейки блока 6 памяти. Таким образом, на вход регистра 10 сдвига с блока 6 подается параллельный код, соответствующий первому слову, а также О в нулевом разряде.

Поступивший на второй вход элемента И-НЕ 7 пусковой импульс на время его действия переводит регистр tO сдвига в режим записи, и на выходе последнего появляется параллельный код, соответствующий первому слову, а также О в нулевом разряде, старший разряд (n-й) слова присутствует на выходе n-го разряда регистра 10 сдвига. Снимаемый с нулевого разряда регистра 10 сдвига О независимо от кода слова поддерживает на выходе дешифратора 12 нуля сигнал 1, который,25 проходя также через элемент 21 задерж- будучи поданным на первый вход эле- ки, подается на вход второго счетчика мента И-ЦЕ 7, совместно с восстановив- 3 и заставляет его увеличить номер шейся после нулевого импульса 1 на ячейки блока 6 памяти на 1, т.е. вы- втором его входе, устанавливает на ставить на выходах блока 6 параллель- его выходе, а следовательно, на выхо- 30 ный код, соответствующий второму сло- де выбора режима регистра 10 сдвига ву, при этом в нулевом разряде сохрасигнал О, переводящий регистр 10 сдвига в режим .сдвига. После установки триггера 13 поступающие с генератора 1 импульсы продвигают записаняую в регистре 10 сдвига информацию к выходу 29 преобразователя кода, осуществляя преобразование параллельного кода в последовательный, снимающийся с выхода 29 преобразователя кода, а также воспроизведение снимаемого кода в регистре 11 сдвига, так как его информационный вход соединен с выходом старшего (n-го) информационного

35

няется сигнал О. Этот же перепад, пройдя через элемент И-НЕ 70 перево- дит регистр 10 сдвига в режим записи. На выходах регистра 10 сдвига появляется второе слово, а сигнал О в нулевом разряде обеспечивает на выходе дешифратора 12 нуля появление перепада с уровня О на уровень 1, ДО На обоих входах элемента И-НЕ 7 оказываются уровни 1, а на выходе - уровень О, переводящий регистр 10 сдвига в режим сдвига, начинается преобразование второго слова, и описан- разряда регистра 10 сдвига. После каж-дз ньг процесс повторяется. По оконча- дого такого импульса записанный в нии преобразования последнего слова

выходной код второго счетчика 3 оказывается одинаковым с выходным кодом первого счётчика 2, т.е. число пре- 50 образованных слов становится равным числу слов, записанных в блок 6 при

нулевом разряде регистра 10 сдвига сигнал О при этом также перемещается к выходу 29, поддерживая на выходе дешифратора 12 нуля сигнал 1. При этом разряды регистра 10 сдвига заполпрограммировании. На выходе схемы 4 сравнения, сравнивающей выходные коды первого и второго счетчиков 2

няются Г1. После преобразования первого (последнего по съему) разряда слова на всех входах дешифратора 12 нуля оказываются сигналы 1, а на вы-55 и , появляется сигнал, устанавливаю- ходе - сигнал О. Перепад с уровня щий триггер 13 в исходное состояние, 1 на уровень О, происходящий бла- соответствующее режиму программиро- годаря инвертору 23, по срезу импуль- вания, т.е. преобразователь кодов са сдвига, подаваемого на один из вхо- устанавливается в исходное состояние.

дов дешифратора 12 нуля, подается на С-вход триггера 14. На его входе в | этот момент присутствует результат поразрядного сравнения сигналов на выходе блока 6 памяти и на выходе регистра 11 сдвига, получаемый с помощью элементов РАВНОЗНАЧНОСТЬ первой группы 1 7, сигналы на выходах которых равны 1 при совпадении значений сравниваемых разрядов. Если на входах одного из элементов РАВНОЗНАЧНОСТЬ значения сравниваемых разрядов окажутся различными, то на его выходе сигнал

5 окажется равным О, который, пройдя через элемент И-НЕ 8 станет равным 1, и, пройдя через элемент ИЛИ 16, поступит на D-вход триггера 14, создавая условия для установки единично0 го выхода триггера, что сигнализирует об ошибке в преобразовании.

Перепад с уровня 1 на уровень О на выходе дешифратора 12 нуля,

няется сигнал О. Этот же перепад, пройдя через элемент И-НЕ 70 перево- дит регистр 10 сдвига в режим записи. На выходах регистра 10 сдвига появляется второе слово, а сигнал О в нулевом разряде обеспечивает на выходе дешифратора 12 нуля появление перепада с уровня О на уровень 1, На обоих входах элемента И-НЕ 7 оказываются уровни 1, а на выходе - уровень О, переводящий регистр 10 сдвига в режим сдвига, начинается препрограммировании. На выходе схемы 4 сравнения, сравнивающей выходные коды первого и второго счетчиков 2

и , появляется сигнал, устанавлива щий триггер 13 в исходное состояние соответствующее режиму программиро- вания, т.е. преобразователь кодов устанавливается в исходное состояни

;1547

Формула изобретения

Преобразователь параллельного кода в последовательный, содержащий блок памяти, информационные входы и вход з&писи которого являются соответственно информационными входами и входом записи преобразователя, выходы блока памяти соединены с одноименными входами первого регистра сдвига, выходы младших п разрядов которого подключены к одноименным входам депгиф- ратора нуля, выход (п+1}-то разряда первого регистра сдвига является вы- ходом преобразователя, первый счетчик сметный вход которого является тактовым входом преобразователя, вход с|броса первого счетчика объединен с первым нулевым входом триггера и является входом сброса преобразователя, выходы первого счетчика соединены с соответствующими первыми входами ком- 4у Јтора и схемы сравнения, выход ко- т)ооой соединен с вторым нулевым вхо- Дом триггера, выходы которого соединены с соответствующими вторыми входами коммутатора, второй счетчик, ход сброса которого объединен с пер- йым входом первого элемента И-НЕ и фпнничным входом первого триггера и f , j входом пуска преобразовате- 4я, выходы второго счетчика соединены 4 соответствующими третьими входами оммутатора и вторыми входами схемы Сравнения, выходы коммутатора соедине ны с соответствующими адресными входа IJJH блока памяти, счетный вход второго Счетчика объединен с вторым входом г Первого элемента И-НЕ, выход которого соединен с входом режима первого регистра сдвига, генератор импульсов, Выход которого соединен с тактовым Входом первого регистра сдвига, отличающийся тем, что, с це- лью повышения достоверности преобразу емого хода, в преобразователь введены ав группы элементов РАВНОЗНАЧНОСТЬ и второй и третий элементы И-НЕ, элемент ИЛИ, генераторы одиночных импульсов, элементы задержки, элемент НЕ, второй и третий триггеры и второй

o

76

- 5 „

0

5

0

8

регистр сдвига, последовательный вход

которого соединен с выходом n-го разряда первого регистра сдвига, тактовый вход объединен с входом элемента НЕ и подключен к выходу генератора импульсов, управляющий вход которого соединен с инверсным выходом первого триггера, выход элемента НЕ соединен с входом дешифратора нуля, выход которого соединен с входом первого элемента задержки и входом первого генератора одиночных импульсов, выход которого соединен с С-входом второго триггера, инверсный выход которого соединен с его инверсным единичным входом, выход первого элемента задержки соединен с входом обнуления второго счетчика, выходы второго регистра сдвига соединены с первыми входами соответствующих элементов РАВНОЗНАЧНОСТЬ первой группы, вторые входы которых объединены с первыми входами соответствующих элементов РАВНОЗНАЧНОСТЬ Bio- рой группы и соединены с соответствующими выходами блока памяти, выходи элементов РАВНОЗНАЧНОСТЬ первой группы соединены с входами второго элемента К-НЕ, выход которого соединен с первым входом элемента ИЛИ, выход т-- торого соединен с D-входом второго триггера,, вторые входы элементов РАВНОЗНАЧНОСТЬ второй группы соединены с соответствующими информационными входами блока памяти, выходы соединены с соответствующими входами третьего элемента И-НЕ, выход которого соединен с D-входом третьего триггера, инверсный выход которого соединен с его инверсным единичным входом, прямой выход третьего триггера соединен с вторым входом элемента ИЛИ, вход второго генератора одиночных импульсов соединен с входом записи блока памяти, выход второго генератора одиночных импульсов соединен с инверсными нулевыми входами второго и третьего триггеров и входом второго элемента задержки s инверсный выход которого соединен с С-входом третьего триггера, прямой выход второго триггера является контрольным выходом преобразователя.

Авторы

Даты

1990-02-28—Публикация

1987-10-05—Подача