го регистра, выход третьей схемы ИЛИ через вторую схему задержки подключен ко вторым входам вентилей четвертой группы, выходы которой соединены с соответствующими входами четвертой схемы ИЛИ, выход которой соединен со входом сумматора, выходы которого подключены к соответствующим входам схемы сравнения, выход которой соединен со вторыми входами вентилей щестой и восьмой групп, выходы которых подключены к соответствующим выходам устройства, третьи входы вентилей второй группы подключены к выходу первого триггера и второму входу второго вентиля, выход которого подключен к соответствующим входам первого блока памяти и ко вторым входам вентилей седьмой группы, выходы которой соединены с соответствующими входами второй и третьей схем ИЛИ, один вход схемы сравнения соединен со входом схемы задания координат, с третьим входом первого распределителя синхросигналов и с одним выходом пятого блока памяти, другой выход которого соединен с четвертым входом первого распределителя синхросигналов, первый выход которого соединен с первым входом пятой схемы ИЛИ и с первыми входами вентилей десятой группы, второй выход первого распределителя синхросигналов соединен со вторым входом пятой схемы ИЛИ и с первыми входами вентилей одиннадцатой группы, выход пятой схемы ИЛИ подключен к соответствующим входам пятого блока памяти, вторые входы одноименных вентилей десятой и одиннадцатой групп подключены к соответствующим выходам пятого блока памяти, выходы вентилей десятой и одиннадцатой групп подключены ко входам соответственно второй и шестой схем ИЛИ, третий выход второго распределителя синхросигналов соединен с соответствующим входом третьей схемы ИЛИ, четвертый выход второго распределителя синхросигналов соединен со вторыми входами вентилей пятой группы и с соответствующими входами пятого и шестого блоков памяти, выходы вентилей пятой группы подключены к соответствующим входам шестого блока памяти, выходы которого подключены к соответствующим входам пятого блока памяти, выходы вентилей первой, второй и третьей групп подключены соответственно ко входам третьего и второго блоков памяти и четвертой схемы ИЛИ, входы щестой схемы ИЛИ соединены с соответствующими выходами первого, третьего и четвертого блоков памяти, соответствующие входы второй схемы ИЛИ подключены к соответствующим выходам второго блока памяти, входы счетчиков подключены к соответствующим выходам схемы задания координат, единичный вход второго триггера и соответствующие входы схемы сравнения соединены с соответствующими входами устройства, единичный вход первого триггера соединен с нулевым входом второго триггера и с соответствующим выходом четвертого блока памяти, выход щестой

схемы ИЛИ соединен со входом первого регистра.

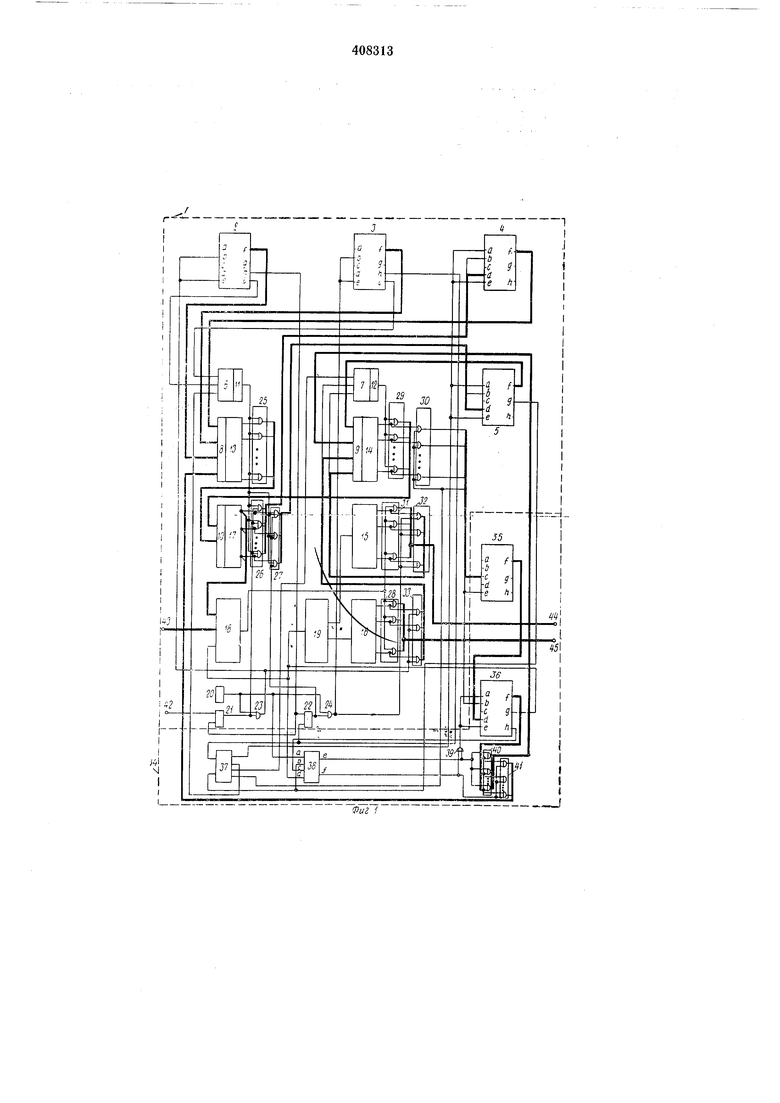

Изобретение пояснено чертежами.

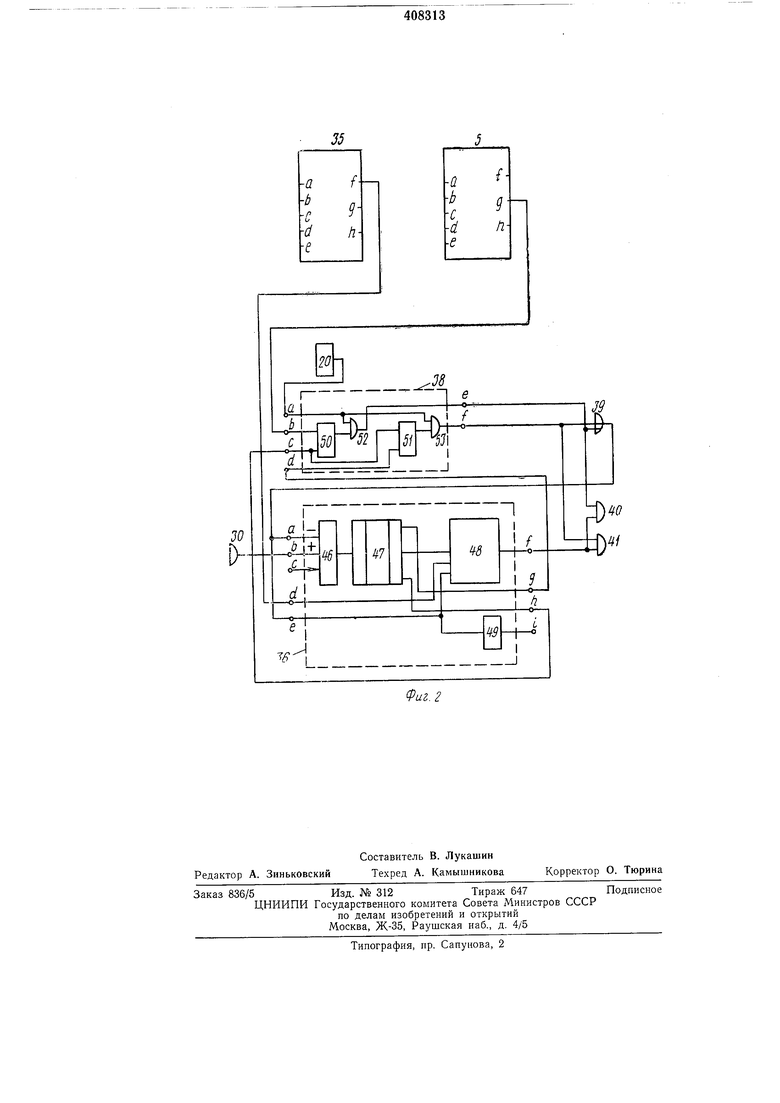

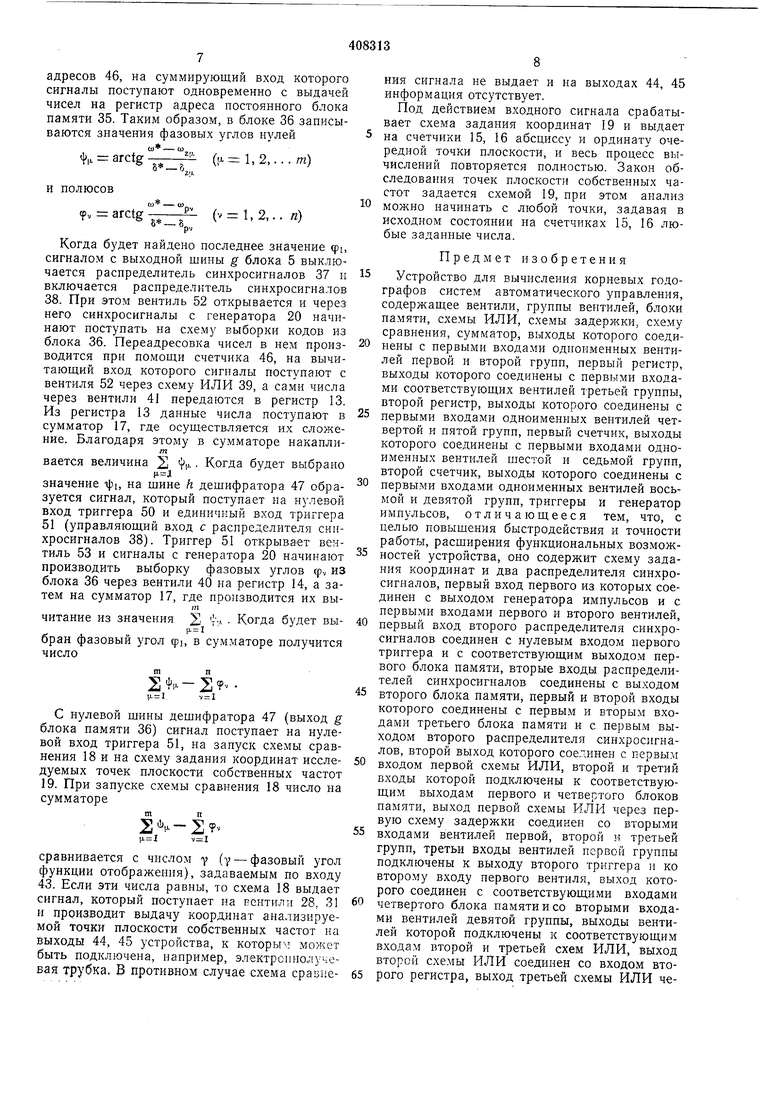

На фиг. I приведена блок-схема устройства; на фиг. 2 - функциональные схемы блока памяти и распределителя синхросигналов и их взаимосвязи.

Устройство для вычисления корневых годографов систем автоматического управления содержит блок исследования плоскости собственных частот 1, состоящий из блоков памяти 2, 3, 4 и 5, схем ИЛИ 6, 7, 8, 9 и 10, схем задержки 11 и 12, регистров 13 и 14, счетчиков 15, 16, сумматора 17, схемы сравнения 18, схемы задания координат 19, генератора импульсов 20, триггеров 21, 22, вентилей 23, 24 и групп вентилей 25, 26, 27, 28, 29 30, 31,32 и 33, и блок формирования фазовых углов 34, состоящий из блоков памяти 35, 36, распределителей синхросигналов 37, 38, схемы ИЛИ 39, групп вентилей 40 и 41.

Входы устройства обозначены цифрами 42 и 43, а выходы его - 44 и 45.

Кроме того, входы блоков памяти и распределителей синхросигналов обозначены через а, Ь, с, d, е, а их выходы (шины) через , g, h, i.

На фиг. 2 дополнительно приведены входящие в состав блока памяти 36 счетчик адресов 46, дешифратор 47, матрица 48, выполненная, например, на ферритах, схема задержки 49 и входящие в состав распределителя синхросигналов 38 триггеры 50, 51 и вентили 52, 53.

Устройство работает следующим образом.

Иеред запуском устройства все регистры,

счетчики, триггеры устанавливают в иуль.

В блок памяти 2 вводят абсциссы полюсов

8pv (, 2, ... л) и нулей бг, (, 2, ...

т) передаточной функции разомкнутой цепи

Р{Р}

/7 Лрч (Р - i) (.Р - ) - (/ - гш) (p - Pi)(p - Ps) ( -Рп

ЫР)

к

ФП(Р)

где К - общий коэффициент усиления систе50мы автоматического управления

(САУ), фтСр)-ПОЛИНОМ степени т; Zi, Zz, ... Zm -

его нули,

Фп{р) - полином степени п; pi, pz, ... Рп - его 55нули, являющиеся одновременно полюсами функции F{p); р .

В блок иа.мяти 3 перед началом работы вводятся ординаты полюсов сор, и нулей cozij. 60 передаточной функции F(p). Блок памяти 35 является постоянным и значения фазовых углов Kj в него вводятся при изготовлении, причем их адресами служат числа .

По входу 43 в устройство задается значе65 ние фазового угла у функции отображения

плоскости собственных частот р на плоскость свободного параметра К., равной

Д- Фп(/)

(Р}

Если необходимо строить корневой годограф Теодорчика - Эванса, то угол у равен

f yv.r, Л 0, ±1, ±2,...

Для корневого годографа фазовых углов угол Y может быть произвольным. В исходном положении блоки памяти 4, 5, 36 должны быть очищены от информации.

Корневые годографы строятся на основании соотношения

джот.,,

У arctg- -fi - У arctg--,

-Spv S -в

где б, соответственно абсцисса и ордината заданной исследуемой точки плоскости собственных частот, V, «V--абсциссы и ординаты полюсов передаточной функции разомкнутой цепи, игр. г.1- абсциссы И ординаты нулей этой

функции.

Запуск устройства осуществляют путем подачи сигнала на вход 42, с которого сигнал поступает на единичный вход триггера 21. При переходе триггера 21 в единичное состояние вентиль 23 и вентили группы 26 открываются. Синхросигнал от генератора 20 проходит вентиль 23 и производит выдачу абсциссы бр, иа блока памяти 2 по его кодовым щинам / в регистр 13. При этом на выходе I возникает сигнал, который, пройдя схемы ИЛИ 6, 10 и задержки 11, выдает эту абсциссу через вентили 25 в сумматор 17. Кроме этого, синхросигнал с вентиля 23 поступает на вентили 33 и производит опрос кода счетчика 16, где при помощи схемы задания координат yO. обследуемых точек плоскости собственных частот р задается абсцисса . Эта абсцисса поступает через вентили 33 в регистр 14, после чего сигналом со схемы ИЛИ 7 через вентили 29 она передается на сумматор 17, где производится вычитание

A8, St-8p,

Эта разность A6i через вентили 26 записывается в блок памяти 4, на счетчике адресов которого предварительно записывается код единица.

Второй сигнал генератора, пройдя аналогичные цепи, обеспечит получение разности

ДВ Sj - Spj

и запись ее в блок памяти 4. Подобным образом действия будут повторяться до тех пор, пока не будет вычислена последняя разность

Si - §2п,

и записана в блок памяти 4. После этого сигнал с выходной щины h дещифратора адреса

блока памяти 2 устанавливает триггер 21 в нулевое, а триггер 22 в единичное состояние. В результате вентиль 23 закрывается, а вентиль 24 и вентили 27 открываются. Очередной сигнал генератора 20 проходит вентиль 24 и производит выдачу ординаты мр, блока памяти 3 по его кодовым щинам f в регистр 13 и выдачу ординаты ш заданной точки р плоскости р из счетчика 15 через вентили 32 в

регистр 14, а затем в сумматор 17 через вентили 29. Задержанный синхросигнал с выхода t блока 3 производит выдачу ординаты «р, через вентили 25 в сумматор 17, где вычисляется разность

AcUj 0)1 - СОр,.

Эта разность Дм через вентили 27 заносится в блок памяти 5, на счетчике адресов которого через вход b предварительно записывается код единица. Следующий имнульс генератора производит те же действия, и на сумматоре вычисляется разность

AtBj (ui - (Upj.

Последующие сигналы с генератора 20 обеспечивают нахождение остальных разностей между ординатой м обследуемой точки и ординатами всех полюсов и нулей передаточной функции разомнутой цепи и запись этих разностей в блок памяти 5. После этого сигнал с выхода h блока 3 устанавливает триггер 22 в нулевое состояние и производит запуск блока формирования фазовых углов 34, запуская распределитель синхросигналов 37.

При запуске блока 34 распределитель синхросигналов 37 начинает выдавать сигналы на схемы выборки кодов из блоков памяти 4, 5 и на схемы ИЛИ 6 и 7 регистров 13, 14 для деления считываемых кодов. Первый сигнал

распределителя 37 производит выборку разности Лбп+га из блока 4 и запись ее в регистр 13, а также разности Acon+m из блока памяти 5 и запись ее в регистр 14. Второй и третий выходы распределителя 37 обеспечивают выдачу управляющих сигналов для выполнения операции деления и нахождения частного на регистре 14

А, п + т -

50

1 - Szra

Четвертый сигнал распределителя синхросигналов 37 обеспечивает передачу частного от деления из регистра 14 через вентили 30 в регистр адреса постоянного блока памяти 35 по входу с и опрос его по входу е, благодаря чему из блока 35 выбираются соответствующие значения фазовых углов

а. - arctgA,. i i

В частности, для Лп+т находят значение

Cn+m тВыбранные значения фазовых углов записываются в блок памяти 36, переадресовка в котором осуществляется при помощи счетчика

адресов 46, на суммирующий вход которого сигналы поступают одновременно с выдачей чисел на регистр адреса постоянного блока памяти 35. Таким образом, в блоке 36 записываются значения фазовых углов нулей

((Л 1,2,... т)

ф|, - arctg

и полюсов

D - с

p.

(v l,2,.. я)

arctg

.

рКогда будет найдено последнее значение ф1, сигналом с выходной шины g блока 5 выключается распределитель синхросигналов 37 и включается распределитель синхросигналов 38. При этом вентиль 52 открывается и через него синхросигналы с генератора 20 начинают поступать на схему выборки кодов из блока 36. Переадресовка чисел в нем производится при помощи счетчика 46, на вычитающий вход которого сигналы поступают с вентиля 52 через схему ИЛИ 39, а сами числа через вентили 41 передаются в регистр 13. Из регистра 13 данные числа поступают в сумматор 17, где осуществляется их сложение. Благодаря этому в сумматоре накаплит

Бается величина 2 Когда будет выбрано

(

значение i|3b на шине h дешифратора 47 образуется сигнал, который поступает на нулевой вход триггера 50 и единичный вход триггера 51 (управляющий вход с распределителя синхросигналов 38). Триггер 51 открывает вентиль 53 и сигналы с генератора 20 начинают производить выборку фазовых углов cpv из блока 36 через вентили 40 на регистр 14, а затем на сумматор 17, где производится их выm

читание из значения 2 - Когда будет выр- 1

бран фазовый угол фь в сумматоре получится число

mп

2 ф|х - 2

,v l

С нулевой щины дешифратора 47 (выход g блока памяти 36) сигнал поступает на нулевой вход триггера 51, на запуск схемы сравнения 18 и на схему задания координат исследуемых точек плоскости собственных частот 19. При запуске схемы сравнения 18 число на сумматоре

mп

2 - 2

H.

сравнивается с числом 7 (v - фазовый угол функции отображения), задаваемым по входу 43. Если эти числа равны, то схема 18 выдает сигнал, который поступает на вентили 28, 31 и производит выдачу координат анализируемой точки плоскости собственных частот на выходы 44, 45 устройства, к которым может быть подключена, например, электроннолучевая трубка. В противном случае схема сравнения сигнала не выдает и на выходах 44, 45 информация отсутствует.

Под действием входного сигнала срабатывает схема задания координат 19 и выдает

на счетчики 15, 16 абсциссу и ординату очередной точки плоскости, и весь процесс вычислений повторяется полностью. Закон обследования точек плоскости собственных частот задается схемой 19, при этом анализ

можно начинать с любой точки, задавая в исходном состоянии на счетчиках 15, 16 любые заданные числа.

Предмет изобретения

Устройство для вычисления корневых годографов систем автоматического управления, содержащее вентили, группы вентилей, блоки памяти, схемы ИЛИ, схемы задержки, схему сравнения, сумматор, выходы которого соедийены с первыми входами одноименных вентилей первой и второй групп, первый регистр, выходы которого соединены с первыми входами соответствующих вентилей третьей группы, второй регистр, выходы которого соединены с

первыми входами одноименных вентилей четвертой и пятой групп, первый счетчик, выходы которого соединены с первыми входами одноименных вентилей шестой и седьмой групп, второй счетчик, выходы которого соединены с

первыми входами одноименных вентилей восьмой и девятой групп, триггеры и генератор импульсов, отличающееся тем, что, с целью повышения быстродействия и точности работы, расширения функциональных возможностей устройства, оно содержит схему задания координат и два распределителя синхросигналов, первый вход первого из которых соединен с выходом генератора импульсов и с первыми входами первого и второго вентилей,

первый вход второго распределителя синхросигналов соединен с нулевым входом первого триггера и с соответствующим выходом первого блока памяти, вторые входы распределителей синхросигналов соединены с выходом

второго блока памяти, первый и второй входы которого соединены с первым и вторым входами третьего блока памяти и с первым выходом второго распределителя синхросигналов, второй выход которого соединен с первым

входом первой схемы ИЛИ, второй и третий входы которой подключены к соответствующим выходам первого и четвертого блоков памяти, выход первой схемы ИЛИ через первую схему задержки соединен со вторыми

входами вентилей первой, второй и третьей групп, третьи входы вентилей первой группы подключены к выходу второго триггера и ко второму входу первого вентиля, выход которого соединен с соответствующими входами

четвертого блока памяти и со вторыми входами вентилей девятой группы, выходы вентилей которой подключены к соответствующим входам второй и третьей схем ИЛИ, выход второй схемы ИЛИ соединен со входом второго регистра, выход третьей схемы ИЛИ через вторую схему задержки подключен ко вторым входам вентилей четвертой группы, выходы которой соединены с соответствующими входами четвертой схемы ИЛИ, выход которой соединен со входом сумматора, выходы которого подключены к соответствующим входам схемы сравнения, выход которой соединен со вторыми входами вентилей шестой и восьмой групп, выходы которых подключены к соответствующим выходам устройства, третьи входы вентилей второй группы подключены к выходу первого триггера и второму входу второго вентиля, выход которого подключен к соответствующим входам первого блока памяти и ко вторым входам вентилей седьмой группы, выходы которой соединены с соответствующими входами второй и третьей схем ИЛИ, один вход схемы сравнения соединен со входом схемы задания координат, с третьим входом первого распределителя синхросигналов и с одним выходом пятого блока памяти, другой выход которого соединен с четвертым входом первого распределителя синхросигналов, первый выход которого соединен с первым входом пятой схемы ИЛИ и с первыми входами вентилей десятой группы, второй выход первого распределителя синхросигналов соединен со вторым входом пятой схемы ИЛИ и с первыми входами вентилей одиннадцатой группы, выход пятой схемы ИЛИ подключен к соответствующим входам пятого блока памяти, вторые входы одноименных вентилей десятой и одиннадцатой

групп подключены к соответствующим выходам пятого блока памяти, выходы вентилей десятой и одиннадцатой групп подключены ко входам соответственно второй и щестой схем

ИЛИ, третий выход второго распределителя синхросигналов соединен с соответствующим входом третьей схемы ИЛИ, четвертый выход второго распределителя синхросигналов соединен со вторыми входами вентилей пятой

группы и с соответствующими входами пятого и щестого блоков памяти, выходы вентилей пятой группы подключены к соответствующим входам щестого блока памяти, выходы которого подключены к соответствующим входам

пятого блока памяти, выходы вентилей первой, второй и третьей групп подключены соответственно ко входам третьего и второго блоков памяти и четвертой схемы ИЛИ, входы щестой схемы ИЛИ соединены с соответствующими выходами первого, третьего и четвертого блоков памяти, соответствующие входы второй схемы ИЛИ подключены к соответствующим выходам второго блока памяти, входы счетчиков подключены к соответствующим выходам схемы задания координат, единичный вход второго триггера и соответствующие входы схемы сравнения соединены с соответствующими входами устройства, единичный вход первого триггера соединеи с нулевым входом второго триггера и с соответствующим выходом четвертого блока памяти, выход щестой схемы ИЛИ соединен со входом первого регистра.

-а

{

-и

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отношения сигнал/шум канала связи | 1981 |

|

SU993163A1 |

| Устройство для вычисления корневыхгОдОгРАфОВ СиСТЕМ АВТОМАТичЕСКОгОупРАВлЕНия | 1979 |

|

SU830395A1 |

| Устройство для вычисления корневых годографов систем автоматического управления | 1981 |

|

SU987584A1 |

| Устройство для вычисления корневых годографов систем автоматического управления | 1977 |

|

SU660058A1 |

| Устройство для вывода графической информации | 1979 |

|

SU930355A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1709355A1 |

| Устройство для формирования адресных сигналов | 1978 |

|

SU769619A1 |

| УСТРОЙСТВО для ПОСТРОЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1973 |

|

SU397914A1 |

| Устройство для распознавания образов | 1989 |

|

SU1709359A1 |

| Кольцевое пересчетное устройство | 1981 |

|

SU993482A1 |

Авторы

Даты

1973-01-01—Публикация