изменения содержимого и регистр фиксации результатов логических операций, первые входы которых подключены к первому выходу блока управления, вторые входы, исключая регистр фиксации результатов логических операций, - к выходу накопителя. Выходы регистра адреса поля оперативной памяти, первого и второго регистров адреса начальной границы массива, регистра длины массива и регистра адреса конечной границы массива соединены со входами арифметического блока с пятого по девятый. Выход регистра длины поля оперативной памяти подключен к управляющим выходным шииам устройства. Выход регистра иризнака изменения содержимого соединен со вторым входом блока управления, третий вход которого подключен к первому выходу регистра фиксации результатов логических операций, вторые вход и выход которого соединены соответственно с четвертым выходом арифметического блока и управляющими выходными шинами.

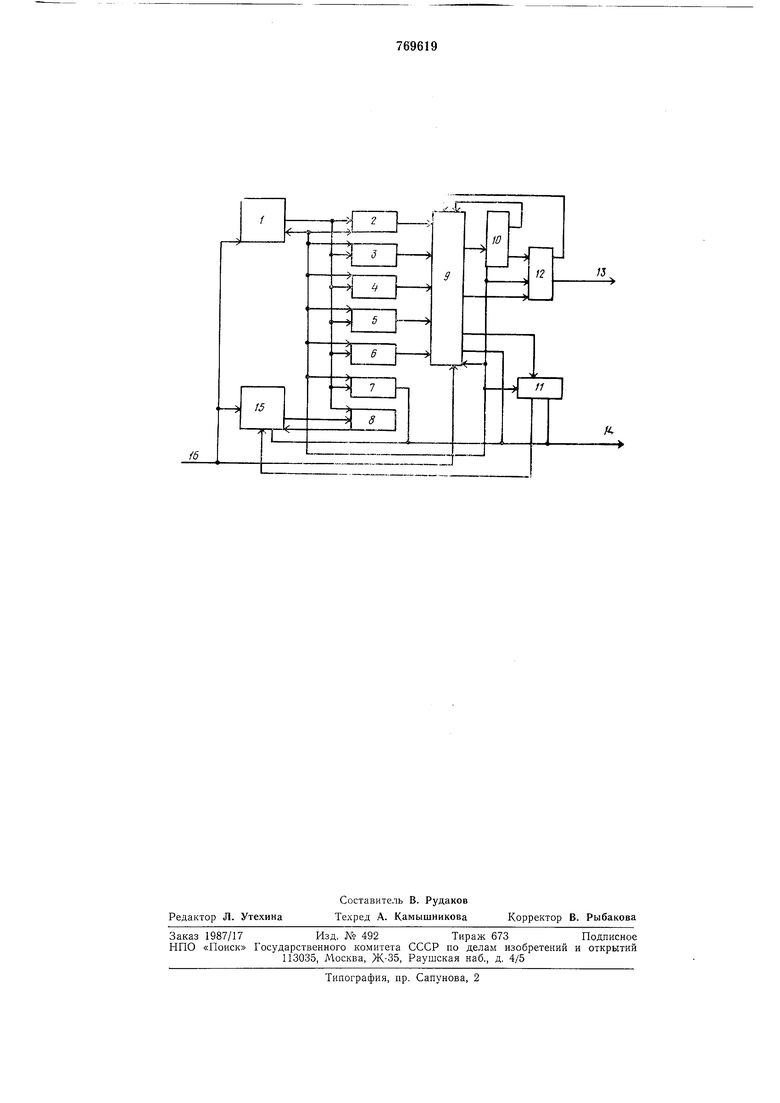

На чертеже изображена схема устройства для формирования адресных сигналов.

Устройство содержит накопитель 1, в качестве которого моЖет быть использовано сверхоперативное ЗУ, регистр адреса поля оперативной памяти 2, первый регистр адреса начальной границы массива 3, регистр длины массива 4, второй регистр адреса начальной границы массива 5, регистр адреса конечной границы массива 6, регистр длины поля оперативной памяти 7, регистр признака изменения содержимого 8, арифметический блок 9, буферный регистр 10, регистр фиксации результатов логических операций И, выходной регистр адреса 12, адресные выходные шины 13 устройства, управляющие выходные шины 14 устройства, блок управления 16 и входные шины 16 устройства.

Первые входы накопителя 1, блоков 9 и 15 подключены к шинам 16. Вторые входы накопителя 1 и блока 9, а также первые входы регистров 10 и 12 соединены с первым выходом блока 15. Первый и второй выходы блока 9 подключены соответственно ко вторым входам регистров 10 и 12. Выходы регистра 12 соединены соответственно с третьим входом блока 9 и шинами 13. Вы.коды регистра 10 подключены соответственно к третьему входу регистра 12 и четвертому входу блока 9. Второй выход блока 15 и третий выход блока 9 соединены с шинами 14.

Первые входы регистров 2-8 подключены к первому выходу блока 15, вторые входы, исключая регистр И, - к выходу накопителя 1. Выходы регистров 2-6 соединеиы еа входами блока 9 (с пятого по девятый). Выход регистра 7 подключен к шинам 14. Выход регистра 8 соединен со вторым входом блока 15, третий вход которого подключен к первому выходу регистра И,

вторые вход и выход которого соединены соответственно с четвертым выходом блока 9 и шинами 14.

Устройство работает следующим образом.

По Шинам 16 поступает номер внешнего адреса, адрес операнда на внешнем ЗУ и длина операнда. Блок управления 15 в первом такте по номеру внешнего адреса считывает из накопителя 1 информацию в регистры 2-8 и устанавливает в нуль регистр 11. Во втором такте на вход арифметического блока 9 подается содержимое регистра 4 и адрес операнда с шин 16, и устанавливается, что адрес операнда меньше адреса конечной границы массива, результат засылается в первый разряд регистра 11. В третьем такте подается на вход арифметического блока 9 адрес операнда с шин 16 и содержимое регистра 3, и устанавливается, что адрес операнда больше адреса начальной границы массива, результат засылается во второй разряд регистра 11. В четвертом такте на вход арифметического блока 9 подается содержимое регистра 6 и адрес операнда с шин 16, и устанавливается, что адрес операнда меньше адреса конечной границы массива во внешнеадресном поле, результат, засылается в третий разряд регистра 11. В пятом цикле подается на вход арнфметического блока 9 адрес операнда с шин 16 и содержимое регистра 5, и устанавливается, что адрес операнда больше адреса начальной границы массива внешнеадресного поля, результат операции засылается в четвертый разряд регистра И. В шестом цикле на вход арифметического блока 9 подается содержимое регистра 6, из него вычитается адрес операнда, который поступает с шин 16, результат засылается в регистр 10. В седьмом такте на вход арифметического блока 9 подается содержимое регистра 10, устанавливается, что оно больше или равно длине операнда, результат засылается в пятый разряд регистра И. В восьмом такте на вход арифметического блока 9 подается адрес операнда с шин 16, из него вычитается содержимое регистра 5, результат засылается в регистр 10. В девятом такте засылается в арифметический блок 9 содержимое регистра 10, к нему прибавляется содержимое регистра 2, результат помещается в регистр 12.

Если адрес операнда не находят во внешнем адресном поле, процессор (на чертеже не показан) считывает необходимую информацию во внешнеадресное поле и корректирует адреса начальной и конечной границ массива во внешнеадресном поле в накопителе 1.

Если процессор обнаружит, что разряд регистра 8 равен единице, то перед считыванием записывается информация из внешнеадресного поля на внешний носитель по адресу регистров 5 и 6. При выполнении онерацни при изменении содержимого внешнеадресного ноля устанавливается единичное значение разряда признака изменения содержимого но шинам 16 блоком управления 15 в накопителе 1. Изменение адреса в процессе выполнения операции производится в арифметическом блоке 9 прибавлением к адресу в регистре 12 величины, которая принимается по шинам 16, результат пересылается в регистр 10, и из него в регистр 12. При адресовании команд по адресам оперативной памяти формирование исполнительного адреса производится суммированием базового адреса, считанного из накопителя 1 в регистр 2, и индексного адреса, подаваемого по шинам 16. Результат номещается в регистр 12. При смене назначения внешнего адреса информация о новом назначении процессором засылается по шинам 16 и записывается под управлением блока 15 в накопитель 1. Изобретение позволяет существенно расширить область применения устройства за счет уменьшения числа команд, регламентируюшнх ввод-вывод информации и обеспечения возможности произвольного обрашения к массивам на внешних ЗУ. Формула изобретения Устройство для формирования адресных сигналов, содержаш,ее наконитель, буферный регистр, выходной регистр адреса, арифметический блок и блок унравления, причем первые входы накопителя, блока унравления и арифметического блока подключены к входным шинам устройства, вторые входы накопителя и арифметического блока, а также первые входы буферного регистра и выходного регистра адреса соединены с первым выходом блока управления, первый и второй выходы арифметического блока подключены соответственно ко вторым входам буферного регистра и выходного регистра адреса, выходы которого соединены cqответственно с третьим входом арифметического блока и адресными выходными шинами устройства, выходы буферного регистра подключены соответственно к третьему входу выходного регистра адреса и четвертому входу арифметического блока, второй выход блока управления и третий выход арифметического блока соединены с управляюшнми выходными шинами устройства, отличаюш,ееся тем, что, с целью расширения области применения устройства путем уменьшения числа команд, регламентпруюш,их ввод-вывод информации и обеспечения возможности произвольного обрашения к массивам на внешних запоминающих устройствах, оно содержит регистр адреса поля оперативной памяти, первый и второй регистры адреса начальной границы .массива, регистр длины массива, регистр адреса конечной границы массива, регистр длины ноля оперативной памяти, регистр признака изменения содержимого и регистр фиксации результатов логических операций, первые входы которых подключены к первому выходу блока унравления, вторые входы, исключая регистр фиксации результатов логических операций, - к выходу накопителя, выходы регистра адреса поля оперативной памяти, первого и второго регистров адреса начальной границы массива, регистра длины массива и регистра адреса конечной границы массива соединены со входами арифметического блока, с нятого по девятый, выход регнстра длины поля оперативной памяти подключен к управляюшнм выходным шинам устройства, выход регистра признака изменения содержимого соединен со вторым входом блока управления, третий вход которого подключен к первому выходу регистра фиксации результатов логических операций, вторые вход и выход которого соединены соответственно с четвертым выходом арифметического блока и управляюш,имивыходными шинами. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 338902, кл. G 06F 9/20, 1969. 2.Патент США №3818460, кл. 340-172.5, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Оперативное запоминающее устройство с защитной информации | 1976 |

|

SU590833A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

Авторы

Даты

1980-10-07—Публикация

1978-06-12—Подача