Изобретение относится к автоматике м вычислительной технике и может быть использовано в системах автоматики и телемеханики при аналоговой и цифровой обработке сигналов.

Известно устройство для воспроизведения функций, которое содержит блок задания параметров функций, буферные и рабочие регистры, схему обратной связи результата аппроксимации с блоком задания параметров функции, а также три цифроаналоговых преобразователя, блок памяти, управляемый генератор импульсов, реверсивный счетчик, триггеры, элементы И, ИЛИ.

Это устройство позволяет воспроизводить си-гналы по дискретным отсчетам и интервалам времени между ними. Основными недостатками устройства являются пониженная точность, невозможность воспроизведения сигналов с разрывами на границах участков аппроксимации, воспроизведение сигнала только лишь в аналоговом виде, невозможность воспроизведения значений функции в отдельных произвольных точках и в произвольные моменты времени, определяемые пользователем, т.е. пониженное удобство эксплуатации и суженный класс решаемых задач.

Наиболее близким к предлагаемому является устройство, содержащее первый и

второй сумматоры, блок задания параметров функций, первый и второй буферные регистры, элементИЛИ, второй и третий выходы блока задания параметров функций подключены к информационным входам соответственно первого и второго регистров ординат и регистра длительности участка аппроксимации, выход которого со.единен с входом управ1ляемого генератора импульсов, выход которого подключен к счетному входу реверсивного счетчика, цифровой выход которого соединен с адресным входом блока памяти значений аргумента, аналоговый выход устройства подключен к выходу цифроаналогового преобразователя, информационные входы цифрового блока умножения .подключены соответственно к выходам блока памяти значений аргумента и первого сумматора, а выход соединен с информационным входом первого буферного регистра, выход которого подключен к первому входу второго сумматора, второй вход которого соединен с выходом второго буферного регистра, а выход второго сумматора является цифровым выходом устройства и подключен к входу цифроаналогового преобразовateля, выход первого регистра ординат соединен с первым входом первого сумматора, второй вход-которого подключен к выходу преобразователя прямого кода в дополнительный, вход которого соединен с выходом регистра ординат и с информационным входом второго буферного регистра, вход записи которого объединен с входом записи первого буферного регистра и подключен к выходу второго элемента задержки, вход которого соединен с входом запуска цифрового блока умножения и с выходом первого элемента задержки, вход кОторого подключен к выходу элемента ИЛИ, входы которого соединены с выходом управляющего генератора импульсов и входом записи реверсивного счетчика, который также подключен к выходу третьего элемента.задержки, вход которого соединен с входами записи первого и второго регистров ординат и регистра длительности участка аппроксимации, с тактовым входом блока задания параметров функций и подключен к выходу признака обнуления реверсивного счетчика, информационный вход которого соединен с входом задания числа интервалов аппроксимирующей функции устройства.

Это устройство позволяет воспроизводить с достаточной точностью функции как в аналоговом, так и в цифровом виде, как без разрывов, так и с разрывами на границах участков аппроксимации. Однако оно обладает рядом недостатков.

В системах автоматики и телемеханики, использующих вычислительные машины, микропроцессорную технику, часто возникает необходимость при цифровой обработке сигналов восстанавливать цифровые коды сигнала только в отдельных точках, задаваемых их абсциссами. Такая задача может возникнуть, например, в устройстве отображения информации для ликвидации диспропорций изображения: если шаг дискретизации отображаемого двумерного поля по горизонтали и вертикали различен, а расстояние между строками.и точками в строках экрана одинаковы, то возникает искажение изображения - вытягивание его по вертикали или горизонтали, Такие диспропорции, когда отношение большего шага дискретизации двумерного поля к меньшему не равно целому числу, наиболее целесообразно исключать отображением не заданных (опорных) отсчетов, а рассчитанных в нужных точках по аппроксимации. При э.том абсцисса воспроизводимого значения может занимать различное относительное расположение на участке аппроксимации (например, ближе к левому или правому концу участка аппроксимации), а в результирующем массиве воспроизводимых значений не должно быть никаких кодов (например, кодов пропуска данных), кроме кодов воспроизводимь1х значений.

Известное устройство воспроизводит подряд все значения функции, не позволяя без изменений связей и введения новых элементов воспроизводить значения функции только в отдельных точках, задаваемых абсциссами, Это связано с тем, что интервалы времени между воспроизводимыми отсчетами и количество и относительное расположение на участке аппроксимации воспроизводимых отсчетов определяется соответственно частотой управляемого генератора импульсов, состоянием информационного входа счетчика и содержимым ячеек блока памяти .соответственно. Это не позволяет применять известное устройство для решения описанной задачи исключения диспропорций изображения.

Кроме того, если длительности участков аппроксимации различны, то- в силу того, что частота управляемого генератора импульсов зависит от длительности участка аппроксимации, известное устройство воспроизводит промежуточные значения сигнала с переменным шагом дискретизации по времени. Однако при цифровой обработке информации часто возникает необходимость воспроизведения промежуточных отсчетов сигнала с постоянным шагом дискретизации по времени. Известное устройство не позволяет при различных длительностях участков аппроксимации воспроизводить промежуточные значения сигнала с постоянным шагом дискретизации по времени.

Кроме того, в силу того, что известное устройство воспроизводит на каждом участке одно и то же число промежуточных отсчетов, его быстродействие как скорость дocти keния цели понижено, например, в следующем случае. Пусть на каком-либо из участков аппроксимации требуется воспроизвести только одну точку, абсцисса которой близка к абсциссе конца этого участка аппроксимации. В известном устройстве для этого требуется сначала воспроизвести все предыдущие промежуточные значения этого участка аппроксимации прежде чем устройство воспроизведет требуемый отсчет. Таким образом, имеют место избыточность вычислений и пониженное быстродействие.

Кроме того, известное устройство воспроизводит промежуточные значения сигнала только в автоматическом режиме, причем воспроизводятся все подряд значения, независимо оттого, нужны ли они пользователю, причем пользователь не имеет .возможности регулировать темп работы устройства - воспроизводить промежуточные отсчеты только по сигналу пользователя. Известное устройство, таким образом, не обеспечивает возможности работы с ним в диалогбвом режиме, что снижает удобство эксплуатации. Кроме того, известное устройство не позволяет воспроизводить на участке аппроксимации значения hoBTopHO или сначала воспроизвести отсчет с большим, а затем с меньшим значением абсциссы внутри участка аппроксимации. Это также снижает удобство его эксплуатации и сужает класс решаемых задач.

Цель изобретения - расширение класса решаемых задач за счет воспроизведения значений функции в отдельных произвольных точках, задаваемых своими абсциссами в произвольные моменты времени, повышение быстродействия и удобства эксплуатации.

Поставленная цель достигается тем, что в устройство для воспроизведения функций, содержащее блок задания параметров функций, первый и второй регистры ординат, регистр длительности участка аппроксимации, три элемента задержки, первый преобразователь прямого кода в дополнительный, два сумматора, цифровой блок умножения, цифроаналоговый преобразоваТ ель, блок памяти значений аргумента, два буферных регистра, элемент ИЛИ, причем первый, второй и третий выходы блока за5 Дания параметров функций подключены к информационным входам соответственно первого и второго регистров ординат и регистра длительности участка аппроксимации, аналоговый выход устройства ..

0 подключен к выходу цифроаналогового преобразователя, информационные входы цифрового блока умножения подключены соответственно к выходам блока памяти значений аргумента и первого сумматора, а

5 выход соединен с информационным входом первого буферного регистра, выход которого подключен к первому входу второго сумматора, второй вход которого соединен с выходом второго буферного регистра, а

0 выход второго сумматора является цифровым выходом устройства и подключен к входу цифроаналогового преобразователя, выход первого регистра ординат соединен с первым входом первого сумматора,

5 второй вход которого подключен к выходу первого преобразователя прямого кода в дополнительный, вход которого соединен с выходом второго регистра ординат и с информационным входом буферного регистра, вход записи которого обьединен с входом записи первого буферного регистра и подключен к выходу второго элемента задержки, вход которого соединен с входом запуска цифрового блока умножения и с выходом первого элемента задержки, вход записи регистра длительности участка аппроксимации объединен с входами записи первого и второго регистров ординат и подключен к тактовому входу блока- задания параметров функций, введены суммирующий счетчик, третий сумматор, первый и второй элементы НЕ, накапливающий сумматор, четвертый элемент задержки, четвертый сумматор, второй преобразователь прямого кода в дополнительный, блок памяти воспроизведенных значений, компаратор, RS-триггер, пятый элемент задержки, вход которого соединен с выходом Больше компаратора и с выходом установки В5-три1:гера, вход сброса которого соединен с выходом пятого элемента задержки, а прямой выход RS-триггера соединен с синхровходом накапливающего суммато|}а и с входом третьего элемента задержки, выход которого соединен с входом первого элемента НЕ, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с входом Пуск устройства, а выход элемента ИЛИ соединен с входом регистра длительности участка

аппроксимации, выход которого соединен с информационным входом накапливающего сумматора и с первым водом четвертого сумматора, второй вход которого подключен к выходу накапливающего сумматора, и суммирующего счетчика.

Введение совокупности элементов и связей обеспечивает расширение класса решаемых задач за счет воспроизведения значений функции в отдельных произвольных точках, задаваемых своими абсциссами в произвольные моменты времени, повышение быстродействия и удобства эксплуатации.

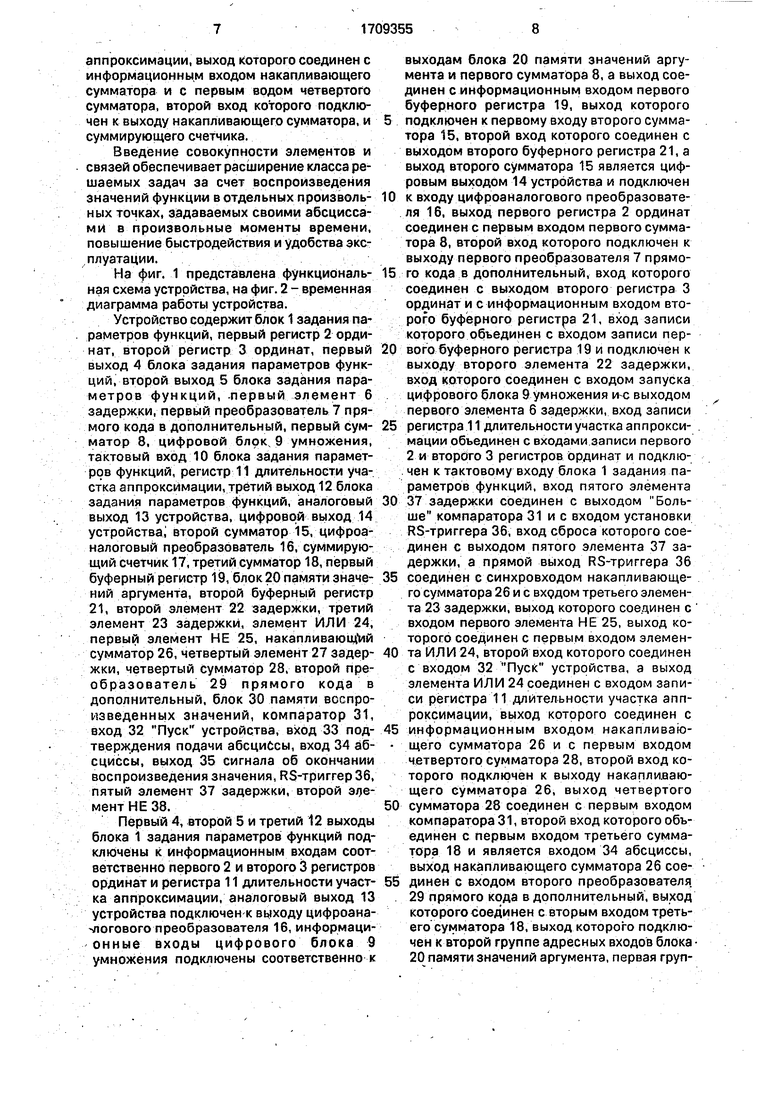

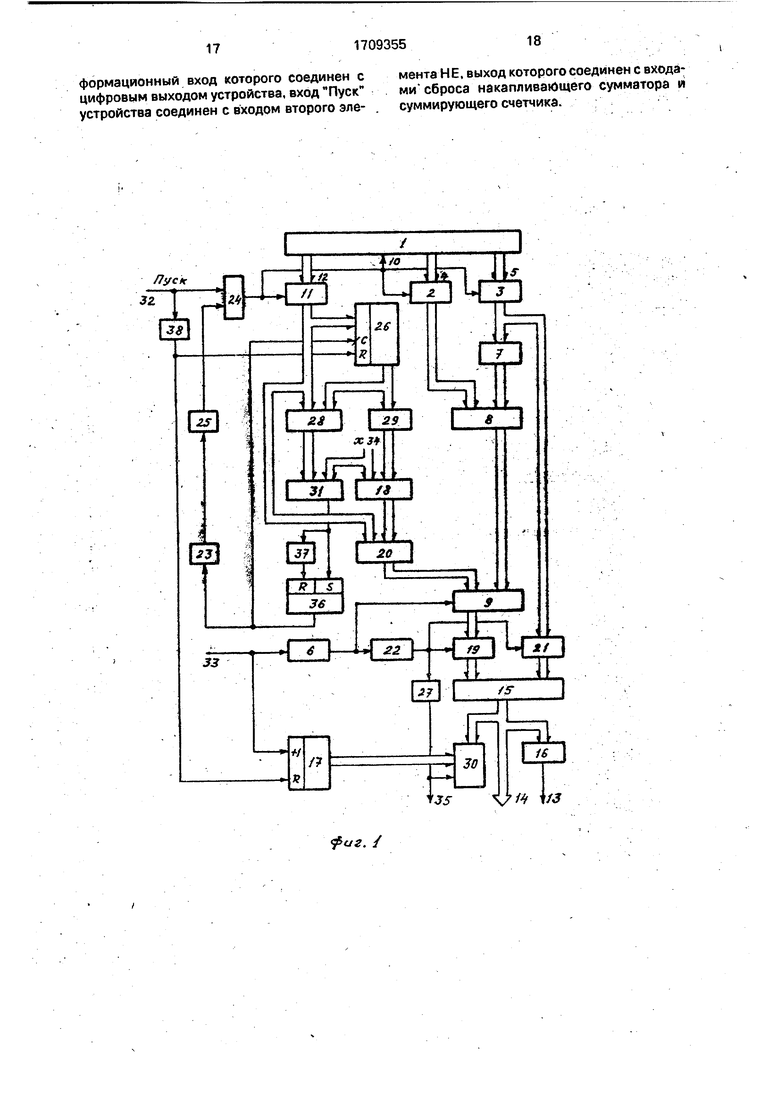

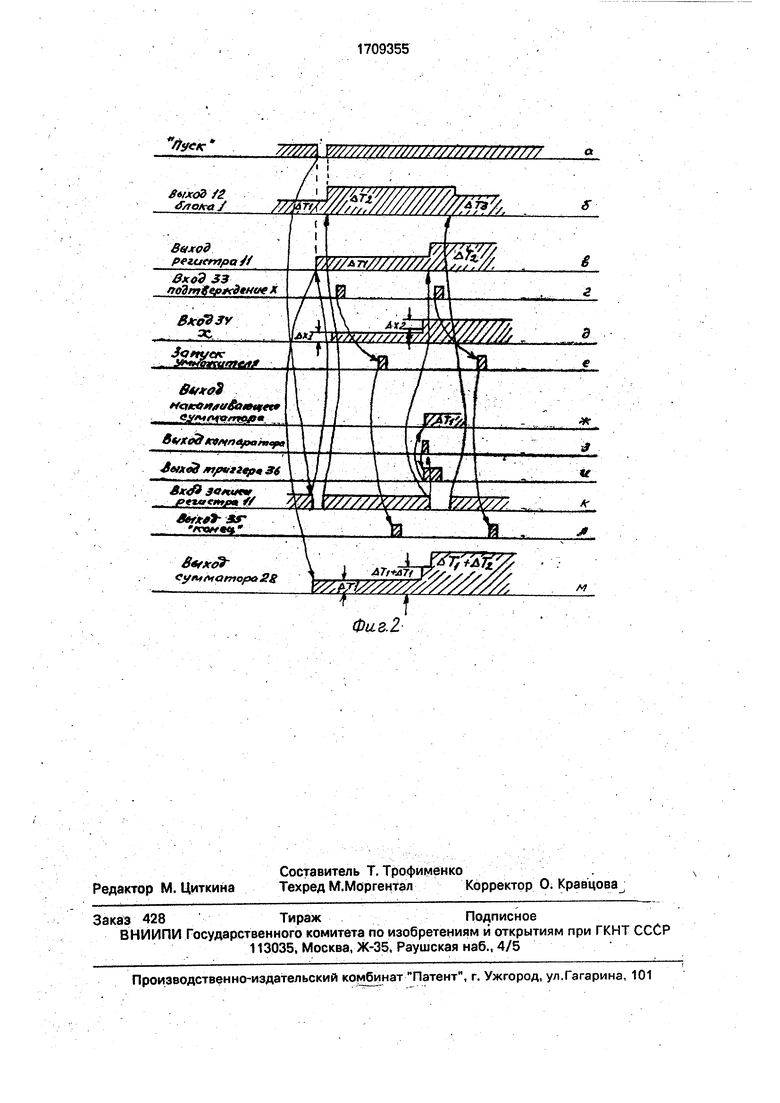

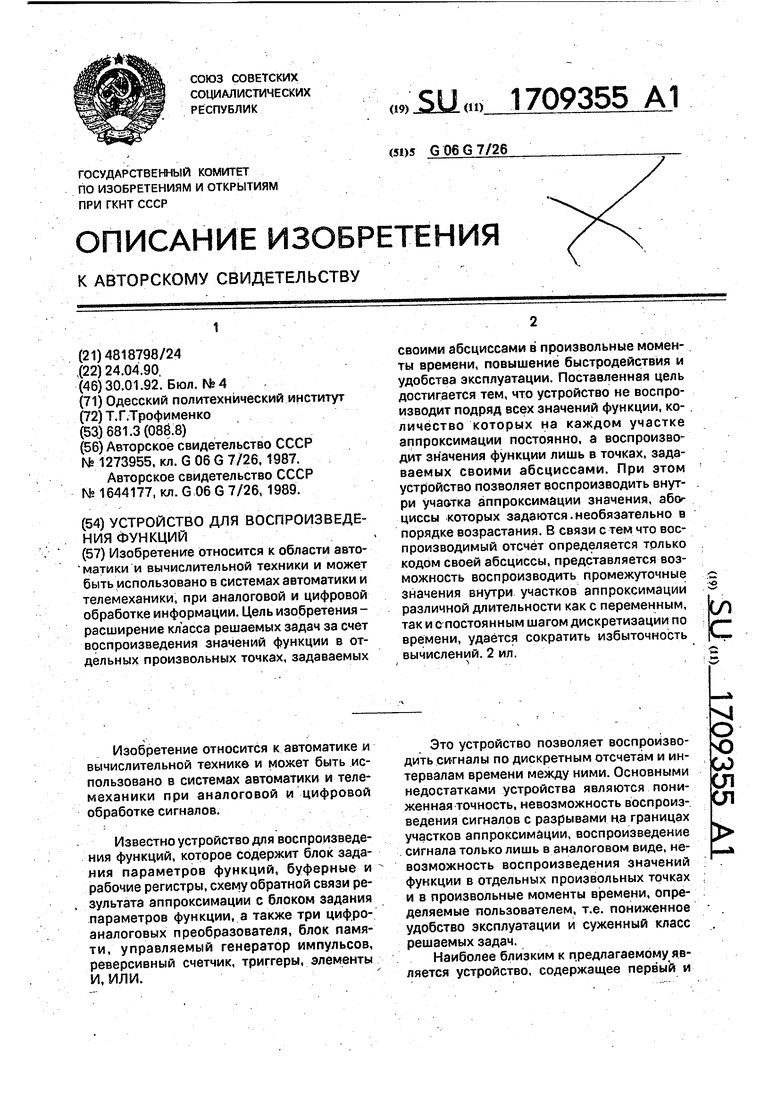

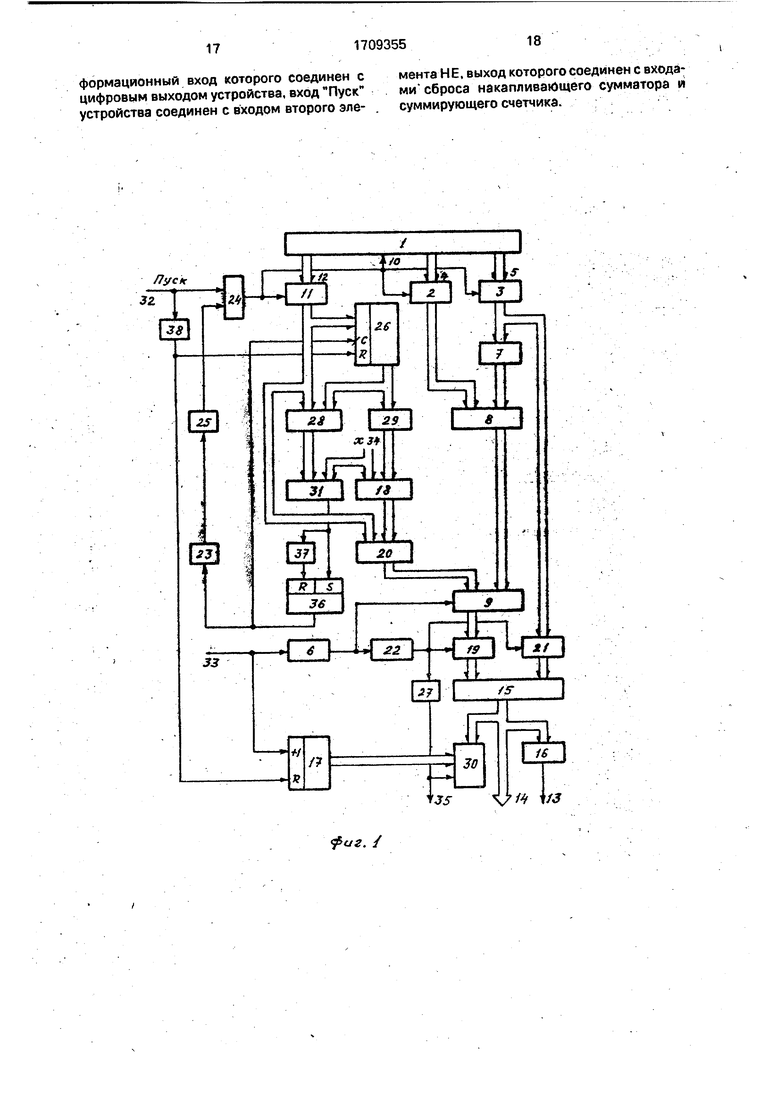

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит блок 1 задания параметров функций, первый регистр 2 ординат, второй регистр 3 ординат, первый выход 4 блока задания параметров функций, второй выход В блока задания параметров функций, -первый элемент 6 задержки, первый преобразователь 7 прямого кода в дополнительный, первый сумматор 8, цифровой блок 9 умножения, тактовый вход 10 блока задания параметров функций, регистр 11 длительности участка аппроксймации,трётий выход 12 блока задания параметров функций, аналоговый выход 13 устройства, цифровой выход 14 устройства второй сумматор 15, цифроаналоговый преобразователь 16, суммирующий счетчик 17, третий сумматор 18, первый буферный регистр 19, блок 20 памяти значений аргумента, второй буферный регистр 21, второй элемент 22 задержки, третий элемент 23 задержки, элемент ИЛИ 24, первый элемент НЕ 25, накапливающШ сумматор 26, четвертый элемент 27 задержки, четвертый сумматор 28, второй преобразователь 29 прямого кода в дополнительный, блок 30 памяти воспроизведеннь1х значений, компаратор 31, вход 32 Пуск устройства, вход 33 подтверждения подачи абсциссы, вход 34 абсциссы, выход 35 сигнала об окончании воспроизведения значения, RS-триггер 36, пятый элемент 37 задержки, второй э ементНЕ38.

Первый 4, второй 5 и третий 12 выходы блока 1 задания параметров функций подключены к информационным входам соответственно первого 2 и второго 13 регистров ординат и регистра 11 длительности участка аппроксимации, аналоговый выход 13 устройства подключен к выходу цифроанаvioroBoro преобразователя 16, информационные входы цифрового блока 9 умножения подключены соответственно к

выходам блока 20 памяти значений аргумента и первого сумматора 8, а выход соединен с информационным входом первого буферного регистра 19, выход которого

подключен к первому входу второго сумматора 15, второй вход которого соединен с выходом второго буферного регистра 21, а выход второго сумматора 15 является цифровым выходом 14 устройства и подключен

0 к входу цифроаналогового преобразователя 16, выход первого регистра 2 ординат соединен с первым входом первого сумматора 8, второй вход которого подключен к выходу первого преобразователя 7 прямого кода в дополнительный, вход которого соединен с выходом второго регистра 3 ординат и с информационным входом второго буферного регистра 21, вход записи которого объединен с входом записи первого буферного регистра 19 и подключен к выходу второго элемента 22 задержки, вход которого соединен с входом запуска цифрового блока 9 умножения и-с выходом первого элемента 6 задержки, вход записи

5 регистра 11 длительности участка аппрокси- . мации объединен с входами записи первого 2 и втордго 3 регистров ординат и подклю. чен к тактовому входу блока 1 задания параметров функций, вход пятого элемента

0 37 задержки соединен с выходом Больше компаратора 31 и с входом установки RS-триггера 36, вход сброса которого соединен с выходом пятого элемента 37 задержки, а прямой вь1ход RS-триггера 36

5 соединен с синхровходом накапливающего сумматора 26 и с вхрдом третьего элемента 23 задержки, выход которого соединен с входом первого элемента НЕ 25, выход которого соединен с первым входом элемента ИЛ И 24, второй вход которого соединен с входом 32 Пуск устройства, а выход элемента ИЛИ 24 соединен с входом записи регистра 11 длительности участка аппроксимации, выход которого соединен с

5 информационным входом накапливаю щего сумматора 26 и с первым входом четвертого сумматора 28, второй вход которого подключен к выходу накапливающего сумматора 26, выход четвертого

0 сумматора 28 соединен с первым входом компаратора 31, второй вход которого объединен с первым входом третьего сумматора 18 и является входом 34 абсциссы, выход накапливающего сумматора 26 соединен с входом второго преобразователя. . 29 прямого кода в дополнительный, выход которого соединен с вторым входом третьего сумматора 18, выход которого подключен к второй группе адресных входов блока 20 памяти значений аргумента, первая группа адресных входов которого подключена к выходу,регистра 11 длительности участка аппроксимации, вход первого элемента 6 задержки является входом 33 подтверждения подачи абсциссы, выход второго элемента 22 задержки соединен с входом четвёртого элемента 27 задержки, выход которого соединен с входом записи блока 30 памяти воспроизведенных значений и является выходом 35 сигнала об окончаний воспроизведения значения, вход 33 подтверждения подачи абсциссы соединен со счетным входом суммирующего счетчика 17, цифровой выход которого соединен с адресным входом блока 30 памяти, воспроизведенных значений, информационный вход которого соединен с цифровым выходом 14 устройства, вход 32 Пуск устройства соединен с входом второго элемента НЕ 38, выход которого соединен с входами сброса накапливающего сумматора 26 и суммирующего счетчика 17,

Аппроксимацию функции у(х) на i-м участке аппроксимации по соседним дискретным отсчетам AI и А2 и интервалу времени ДТ| между ними устройство реализует по следующей формуле:

/ДхЧ

И

y Ai-i-(A2-AI) F 1-1

гдеАх х- у AT о ,

AI и А2 - соответственно первый и второй дискретные отсчеты сигнала на 1-м участке аппроксимации;

АТ| - интервалы времени между соседними дискретными отсчетами AI и А2 сигнала;

F - аппроксимирующая функция,

./Ах,

N ..

Блок 20 памяти предназначен для табличного вычисления значений аппроксими(Ж IAT.J

На его выходах

рующей функции F

формируется код, значение которого не более единицы и не менее нуля и определяется видрм аппроксимирующей функции. Код

.{Ак N

определяется таблично блоком 20

памяти как соответствующий значению дроби Ах/АТ|, т.е. относительному положению абсциссы воспроизводимого значения на текущем 1-м участке аппроксимации. Значение АТ| подается на первую группу адресных входов блока 20 памяти, а значение Ах

подается на вторую группу адресных входов блока 20 памяти. На выходе блока 20 фор(М

IAT.Jмируется код F

При выходе абсциссы X за пределы текущего 1-го участка аппроксимации устройство обеспечивает автоматическую смену параметров Ai, Аа.

1-1 АТ|. Это происходит при х Т ATj+ Д Ti.

0

Накапливающий сумматор 26 предназначен для формирования и хранения суммы 1-1 Т Ьлок 30 памяти предназначен для

5 хранения воспроизведенных, значений функции.

Устройство для воспроизведения функций работает следующим образам.

Перед началом работы устройства на

0 выходах 12, 4 и 5 блока 1 задания параметров выставлены коды ATi (фиг. 26), А2 и AI соответственно (блок 1 задания параметров функций состоит из суммирующего счетчика, реагирующего на передний

5 фронт, счетного импульса, счетный вход счетчика является тактовым входом блока 1, цифровой выход счетчика соединен с адресными входами трех блоков памяти, предназначенных для хранения кодов АТГ,

0 Ai, А2 соответственно), на вход 34 подан кйд нуля. Сигнал уровня логического нуля Пуск поступает через второй элемент НЕ 38 на входы сброса накапливающего сумматора 26 и суммирующего счетчика 17 и

5 обнуляет их, одновременно сигнал Пуск поступает через элемент ИЛИ 24 на входы записи регистров 2, 3,.11 (фиг. 2к), разрешая параллельную запись в эти регистры . подготовленных блоком 1 кодов значений

0 А2 , Ai All соответственно (фиг. 2в), а также на тактовый вход блока 1, разрешая ему начать подготовку данных для следующего : участка аппроксимации (они сформируются на выходах блока 1 после окончания

5 действия импульса Пуск уровня логического нуля - фиг. 26). Таким образом, на выходах регистров 11, 2, 3 формируются необходимые параметры 1-го участкам аппроксимации - ATi,

0 В произвольный момент времени на вход 34 устройства поступает код абсциссы X (он может быть, например, набран пользователем с помощью тумблерного регистра или поступить от микропроцессорной

5 систем.ы, (см, фиг. 2д). Через произвольное время (это время может быть и фиксированным, если устройство работает в автомати, ческом режиме) на вход 33 устройства поступает сигнал (фиг. 2г) в виде импульса

уровня логической единицы, подтверждающий подачу абсциссы (в автоматическом Фежиме этот сигнал может быть подан, например, от микропроцессорной системы или это могут быть задержанные навремя формирования кода х на входе 34 инвертированный сигнал Пуск или сигнал об окончании воспроизведения значения). Этот сигнал с входа 33 устройства переводит счетчик 17 в следующее, первое, состояние, определяя тем самым адрес ячейки блока 30 памяти, в которую будет записано воспроизведенное значение функции. В это время на выходе четвертого сумматора 28 оказывается с:формированным код ATI (фиг. 2м) как сумма кода ATi, поданного с выхода регистра 11, и кода нуля (сумма длительностей предыдущих участков аппроксимации, накапливаемая накапливающим сумматором 26, на первом участке аппроксимации равна нулю) с выхода накапливак щего сумматора 26. Таким образом, на первый вход компаратора 31 поступает код ATi, а на второй вход компаратора 31 гюступает код х, и пока значение X не превышает значения ATi, выход Больше компаратора остается в нулевом состоянии. Одновременно коде выхода накапливающего сумматора 26 (для первого участка аппроксимации это код куля) поступает на вход преобразователя 29 прямого кода в дополнительный, на выходе которого формируется дополнительный код содержимого накапливающего сумматора, который поступает на ёторой вход третьего сумматора 18, на выходе которого формируется код Ах (для первого участка аппроксимации код А х х). Код Ах поступает на вторую группу адресных входов блока 20 памяти, на первую группу адресных входов которого поступает код ATi. На выходе 20 памяти формируется записанный в ячейке с адресом, определяемым кодами ATi и Ах, код значения аппроксимирующей функции F пГТг

поступает на первый информационный вход цифрового блока 9 умножения. Одновременно на второй информационный вход блока умножения поступает код разности (), сформированный на выходе первого сумматора 8, на первый вход которого поступает код А2 с выхода регистра 2/а на второй вход сумматора 8 поступаетдополнительный код числа AI , сформированный на выходе преобразователя 7i на вход которого подан код At с выхода регистра 3. Время задержки те, определяемое элементом задержки 6, достаочно для того, чтобы к моменту запуска цифрового блока 9 умножения,на его инфорационных входах успели сформироваться

коды р(-;г-тг-| и (Aa-Ai) соответственно Д ||

последний меняется только при выполне1-1

НИИ условия X у ATj-t- АТр. Результат умч1/Ах

ножения (А2-А1 )р|-д поступает

на

нформационный вход первого буферного регистра 19 и записывается в этот регистр по сигналу с выхода второго элемента 22

адержки, задержанному на время 22, небходимое для выполнения операции умножения. По этому же сигналу с выхода элемента 22 задержки производится запись во второй буферный регистр 21 кода

AI с выхода регистра 3. Коды с выходов буферных регистров 19 и 21 поступают соответственно на первый и второй вхрды второго сумматора 15. Таким образом, на цифровом выходе 14 устройства

формируется код воспроизведенного значения в точке с абсциссой х, принадлежащей 1-му (в рассматриваемом случае 1-му) интервалу дискретизации: у ( Ai)F 3 на аналоговом выходе 13 li/

соответствующий ему уровень аналогового сигнала.

Сигнал с выхода элемента 27 задержки, время Г27 которой выбирают достаточным для того, чтобы на выходе сумматора 15 сформировался код.воспроизводимого значения, поступает на вход записи блока 30 памяти, разрешая запись в его ячейку по адресу, сформированному счетчиком

17, кода воспроизведенного значения. Одновременно сигнал с выхода элемента 27 задержки является сигналом об окончании воспроизведения значения, который .поступает на выход 35 устройства (фиг, 2л).

После этого в произвольный момент времени на вход 34 устройства может быть подан код нового значения абсциссы х. Если это новое значение не превышает суммы 1-1

У ATj+ ATi (для первого участка аппроксимации эта сумма равна ATi), то устройство работает аналогично описанному. Если же новое значение х превысит сумму длительностей предыдущих и текущего

участка аппроксимации (именно такая ситуацияИ отражена на фиг. 2), то устройство будет работать слё дующим образом.

На выходе Больше компаратора 31 появляется сигнал уровня логической единицы (фиг. 2з), который поступает на вход устаноаки RS-триггера 36, устанавливая его в единичное состояние (фиг. 2и). Сигнал с прямого выхода триггера 36 поступает на синхровхрд накапливающего сумматора 26, увеличивая его содержимое на величину АТ|, фиг. 2ж (код значения AT) подан на информационный вход накапливающего сумматора 26 с выхода регистра 11). Затем сигнал с прямого выхода триггера 36, задержанный элементом задержки 23 на время Г23, достаточное для изменения состояния накапливающего сумматора 26, и инвертированный элементом НЕ 25, поступает через элемент ИЛИ 24 на входы записи регистров 11, 2 и 3, разрешая параллельную запись в них новых значений ATi, А2, AI соответственно. Через время Тз7 задержки, определяемое элементом 37 задержки, достаточное для того, чтобы сигнал с прямого триггера 36 изменил содержимое накапливающего сумматора 26 и, инвертированный с задержкой Г2з, изменил содержимое регистра 11, а также что . .- 1-1 бы новые коды х и Т АТ| успели

сформироваться на входах компаратора, сигнал с выхода элемента 37 задержки сбрасывает триггер 36 в нулевое состояние (фиг. 2и), далее устройство воспроизводит новое значение функции так же, как описано выше. При этом время задержки элемента 6 Гб удовлетворяет следующему неравенству: Tfe 7з7 Ti3.

Необходимость введения в устройство триггера 36 и элемента 37 задержки вызвана следующим. Когда х превышает сумму длительностей предыдущих участков аппроксимации (она хранится в накапливающем сумматоре 26) и текущего участка (содержимое регистра 11), т.е; когда х превысит значение на выходе сумматора 28 (фиг. 2м), то сначала изменяется содержимое накапливающего сумматора 26 - оно увеличивается на величину текущего значения длительности участка аппроксимации, и лишь после этого через время, определяемое элементом 23 задержки, происходит запись в регистр 11 нового значения ATi+-i. Поэтому в момент времени, когда содержимое накапливающего сумматора уже увеличилось на величину текущего АТь а содержимое регистра 11 еще не изме1;|илось, значение на выходе сумматора 28 может составить Т ATj+ ATi (фиг. 2м), и если

I при этом АТн-1 АТ| и х Т АТ}+ ATi (но

1 при этом выполняется х У ATj+АТ -ц),

то на выходе Больше компаратора может

возникнуть ложный импульс. Триггер 36 и элемент задержки 37 и предназначены для того, чтобы не допустить попадания этого ложного импуАъса на синхровход накапливающего сум атора 26.

Таким o ipiiaaoM, благодаря введению новых элементов м связей устройство не воспроизводит подряд всех значений функции, количество которых на каждом участке аппроксимации постоянно, а воспроизводит значения функции лищь в точках, задаваемых своими абсциссами. При этом устройство позволяет воспроизводить внутри участка аппроксимации значения, абсциссы которых задаются необязательно в

порядке возрастания (поскольку параметры участка аппроксимации ATi, Ai.Aa изме1-1няются только при условии х у ATj+ATi).

В связи с тем, что воспроизводимый отсчет

определяется только кодом своей абсциссы, предоставляется возможность воспроизводить промежуточные значения внутри участков аппроксимации различной длительности как с переменным, так и с постоянным шагом дискретизации по времени, сократить избыточность вычислений. Кроме того, предлагаемое устройство обеспечивает выполнение воспроизведения значения функции как в автоматическом

режиме, так и в произвольный момент времени -по сигналу пользователя, что обеспечивает повышение удобства эксплуатации устройства и расширение класса решаемых задач. Это позволяет применять предложенное устройство, например, для специального масштабирования, исключающего диспропорции в устройствах отображения. Кроме того, отсутствие необходимости воспроизведения всех промежуточных значений

внутри участка аппроксимации повышает быстродействие устройства (скорость достижения поставленной цели). Например, на каком-то из участков аппроксимации требуется воспроизвести только одну

точку, абсцисса которой близка к абсциссе конца этого участка аппроксимации. В устройстве-прототипе для этого требуется сначала воспроизвести все предыдущие промежуточные значения этого участка ап-

проксимации, прежде чем устройство приступит к воспроизведению требуемого отсчета-. В предлагаемом же устройстве воспроизведение требуемого отсчета начинается без этой задержки - как только на соответствующий вход устройства поступит

абсцисса требуемого отсчета и поступление ее будет подтверждено соотвествующим сигналом.

Таким образом, введение новых эле ментов и связей обеспечивает достижение поставленной цели- расширение класса решаемых задач за счет воспроизведения значений функции в отдельных произвольных точках, задаваемых своими абсциссами в произвольные моменты времени, повышение быстродействия и удобства эксплуатации,

Ф о р.м улаизобретения;

Устройство для воспроизведения функций, содержащее блок задания параметров функций, первый и второй регистры ординат, регистр длительности участка аппроксимации, три элемента задержки, первый преобразователь прямого кода в дополнительный, два сумматора, цифровой блок умножения, цифроаналоговый преобразователь, блок памяти значений аргумента, два буферных регистра, элемент ИЛИ, причем первый, второй и третий выходы блока задания параметров функций подключены к информационным входам соответственно первого и второго регистров, ординат и регистра длительности участка аппроксимации, аналоговый выход устройства - к выходу цифроаналогового преобразователя, информационные входы цифрового блока умножения - соответственно к выходам блока памяти значений аргумента и первого сумматора, и выход соединен с информационным входом первого буферного регистра, выход которого подключен к первому входу второго сумматора, второй вход которого соединен с выходом второго буферного регистра, а выход второго сумматора является цифровым входом устройства и подключен к входу цифроаналогового преобразователя, выход первого регистра ординат Соединен с первым входом первого сумматора, втоpoi i вход которого подключен к йыходу первого преобразователя прямого кода в дополнительный, вход которого соединен с выходом второго регистра ординат и с информационным входом второго буферного регистра вход записи которого объединен с входом записи первого буферного регист ра и подкЛчЮчен к выходу второго элемента задержки, вход которого соединен с входом запуска цифрового блока умножения и с выходом первого элемента задержки, вход записи регистра длительности участка аппроксимации объединен с входами записи первого и второго регистров ординат и подключен к тактовому входу

блока задания параметров функций, отличающееся тем, что, с целью расширения класса решаемых задач за счет воспроизведения значений функции в отдельных

произвольных точках, задаваемых своими абсциссами в произвольные моменты времени, повышение быстродействия и удобства эксплуатации, в него введены суммирующий счетчик, третий сумматор, первый и второй

0 элементы НЕ, накапливающий сумматор, четвертый элемент задержки, четвертый сумматор, второй преобразователь прямого кода в дополнительный, блок памяти воспрот изведенных значений, компаратор, RS-триг5 гер, пятый элемент задержки, вход которого соедин€1н с выходом Больше компаратора и с входом установки RS-триггера, вход сброса соединен с выходом пятого элемента задержки, а прямой выход RS-триггера

0 соединен с синхровходом накапливающего сумматорами с входом третьего элемента задержки, выход которого соединен с входом первого элемента НЕ, выход которого соединен с первым входом элемента ИЛИ,

5 второй вход которого соединен с входом Пуск устройства, а выход элемента ИЛИ соединен с входом записи регистра длительности участка аппроксимации, выход которого соединен с информационным входом накапливающего сумматора и с первым входом четвертого сумматора, второй вход которого подключен к выходу накапливающегосумматора, выход четвертого сумматора соединен с первым входом компаратора, второй вход которого объединен с первым входом третьего сумматора и является входом абсциссы, выход накапливающего сумматора соединен с входом второго преобразователя прямого кода в

0 дополнительный, выход которого соединен с вторым уходом третьего сумматора, выход которого соединен с вторым входом третьего сумматора, выход которого подключен к второй группе адресных входов

5 блока памяти значений аргумента, первая группа адресных входов которого подключена к выходу регистра длительности участка аппроксимации, вход первого элемента задержки является входом подтверждения

0 подачи абсциссы,выход второго элемента задержки соединен с входом четвертого элемента задержки, выход которого соединен с входом записи блока памяти воспроизведенных значений и является выходом

5 сигнала об окончании воспроизведения, значений, вход подтверждения подачи .абсциссы соединен со счетНым входом суммирующего счетчика. Цифровой выход которого соединен с адресным входом бло- КЗ памяти воспроизведенных значений, информационный вход которого соединен с цифровым выходом устройства, вход Пуск устройства соединен с входом второго эле- .

мента НЕ. выход которого соединен с входами сброса накапливающего сумматора и суммирующего счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1990 |

|

SU1732360A2 |

| Устройство для воспроизведения функций | 1989 |

|

SU1644177A1 |

| Функциональный преобразователь | 1984 |

|

SU1176344A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU993271A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

Изобретениге относится к области авто- 'матики и вычислительной техники и можетбыть использовано в системах автоматики и телемеханики, при аналоговой и цифровой обработке информации. Цель изобретения - расширение класса решаемых задач за счет воспроизведения значений функции в отдельных произвольных точках, задаваемыхсвоими абсциссами в произвольные моменты времени, повышение быстродействия и удобства зксплуатации. Поставленная цель достигается тем, что устройство не воспроизводит подряд всех значений функции, количество которых на каждом участке аппроксимации постоянно, а воспроизводит зн'ачения функции лишь в точках, задаваемых своими абсциссами. При этом устройство позволяет воспроизводить внутри учаотка аппроксимации значения, або^ циссы которых задаются.необязательно в порядке возрастания. В связи с тем что воспроизводимый отсчёт определяется трлько кодом своей абсциссы, представляется возможность воспроизводить промежуточные значения внутри участков аппроксимации различной длительности как с переменным, так и ^постоянным шагом дискретизации по времени, удаётся сократить избыточность вычислений.2 ил.с;Ё

95с/г, /

W //////////y/////y ///// ///7/

I I

mm xw/////M /.

.

1---

f

A

г

-.

с

ж

и

т

Фи,г.2

| Устройство для воспроизведения функций | 1985 |

|

SU1273955A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-04-24—Подача