(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРНЕВЫХ

ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО

УПРАВЛЕНИЯ

Поставленная цель достигается тем, что устройство для вычисления корневых годографов систем автоматического управления, содержащее генератор импульсов, распределитель синхросигналов, триггеры, счетчики, элементы И, элементы ИЛИ, блок памяти, схему сравнения, первый вход которой является информационным входом устройства, первый регистр, выход которого соединен с первыми входами элементов И первой группы, второй регистр, выход которого соединен с первыми входами элементов И второй группы, третий регистр, содержит арифметический блок, информационный выход которого соединен с информационными входами первого, второго и третьего регистров, выход знакового разряда арифметического блока соединен с первым входом элемента неравнозначности, выход которого соединен с входами знаковых разрядов каждого из регистров, первый информационный вход арифметического блока соединен с выходами элементов ИЛИ первой группы, второй информационный вход - с выходами элементов ИЛИ второй группы, вход деления арифметического блока подключен к выходу первого элемента ИЛИ и к первому входу второго элемента ИЛИ, вход вычитания арифметического блока соединен с выходом третьего элемента ИЛИ, вход умножения арифметического блока соединен с первыми входами четвертого и пятого элементов ИЛИ и с соответствующим выходом распределителя синхросигналов, вход сложения арифметического блока соединен с вторым входом четвертого элемента ИЛИ, с первым входом шестого элемента ИЛИ и с соответствующим выходом распределителя синхросигналов, выход состояния арифметического блока соединен с первым входом первого элемента И, выход которого соединен с входом распределителя синхросигналов, первый управляющий выход блока памяти соединен с первым входом второго элемента И, выход которого соединен с управляющим входом блока памяти, нулевым входом первого триггера, входом первого счетчика, управляющими входами схемы сравнения и третьего регистра, второй управляющий выход блока памяти соединен с единичным входом первого триггера, вход блока памяти подключен к выходу седьмого элемента ИЛИ и к первым входам элементов И третьей группы, вторые входы которых соединены с информационным выходом блока памяти, выходы элементов И третьей группы соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И четвертой группы, первые входы которых и второй вход схемы сравнения соединены с выходом третьего регистра, третьи входы элементов ИЛИ второй группы соединены с выходами элементов И второй группы, вторые входы которых соединены с выходом восьмого элемента

ИЛИ, выходы элементов И первой группы соединены с первыми входами элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов пятой группы, третьи входы - подключены к выходам элементов И щестой группы, первые входы которых соединены с информационным выходом первого счетчика и с первым информационным выходом устройства, четвертые выходы элементов ИЛИ первой группы соединены с выходами элементов И седьмой

группы, первые входы которых подключены к информационному выходу второго счетчика и к второму информационному выходу устройства, вторые входы элементов И первой группы соединены с выходом второго

, элемента ИЛИ, выход четвертого элемента ИЛИ соединен с вторыми входами элементов И четвертой группы и с вторым ходом второго элемента ИЛИ, управляющий выход первого счетчика соединен с входом второго счетчика, управляющий выход которого соединен с нулевым входом второго триггера, единичный вход которого является управляющим входом устройства, выход второго триггера соединен с вторым входом первого элемента И, третий вход которого подключен к выходу генератора импульсов, выход первого триггера соединен с первым входом третьего элемента И, выход которого соединен с вторым входом элемента неравнозначности, вход первого регистра соединен с выходом щестого элемента ИЛИ, вход второго

0 регистра соединен с выходом пятого элемента ИЛИ, выход схемы сравнения является управляющим выходом устройства, первые входы элементов И пятой группы являются входами устройства, выходы распределителя синхросигналов соединены соответственно с

5 первым входом седьмого элемента ИЛИ, вторыми входами элементов И шестой трупы, первым входом третьего элемента ИЛИ, вторым входом щестого элемента ИЛИ, вторым входом седьмого элемента ИЛИ, вторыми входами элементов И седьмой группы, вторым входом третьего элемента ИЛИ, вторым входом пятого элемента ИЛИ, с первым входом восьмого элемента ИЛИ, первым входом первого элемента ИЛИ, третьим входом щестого элемента ИЛИ, с вторым

5 входом третьего элемента И, вторым входом восьмого элемента ИЛИ, третьим входом третьего элемента ИЛИ, вторыми входами элементов И пятой группы, с третьим входом пятого элемента ИЛИ, третьим входом восьмого элемента ИЛИ, вторым входом первого элемента ИЛИ, с входом третьего регистра и с вторым входом второго элемента И.

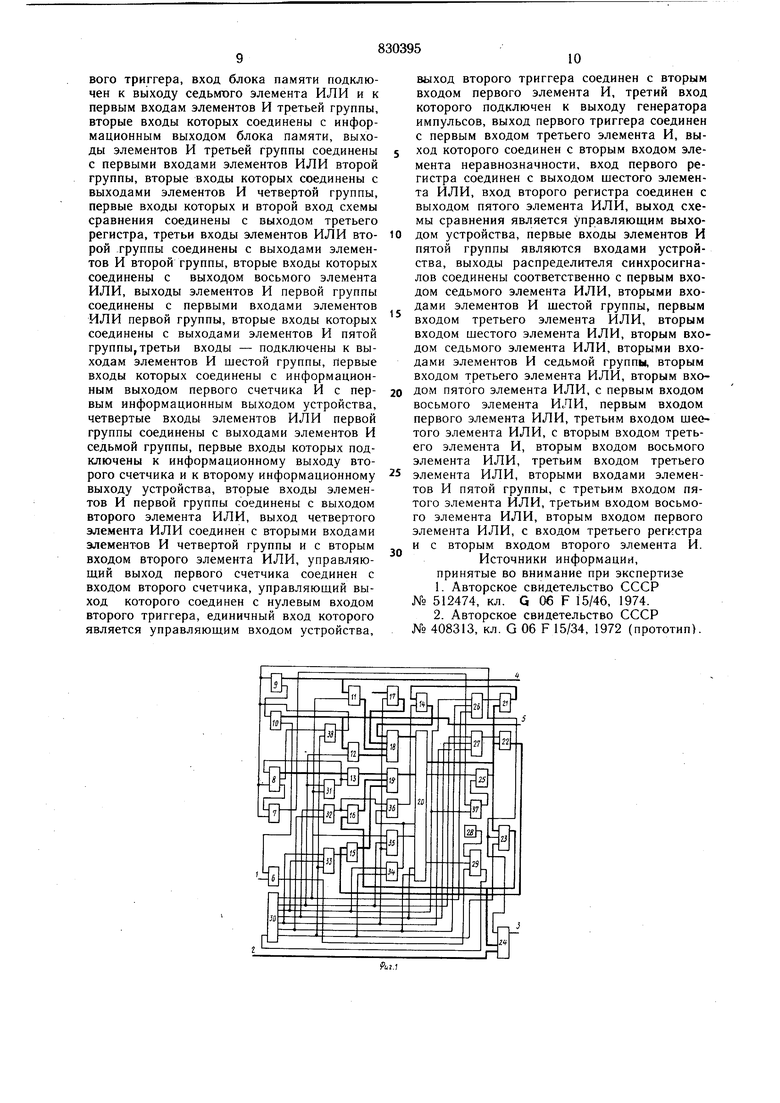

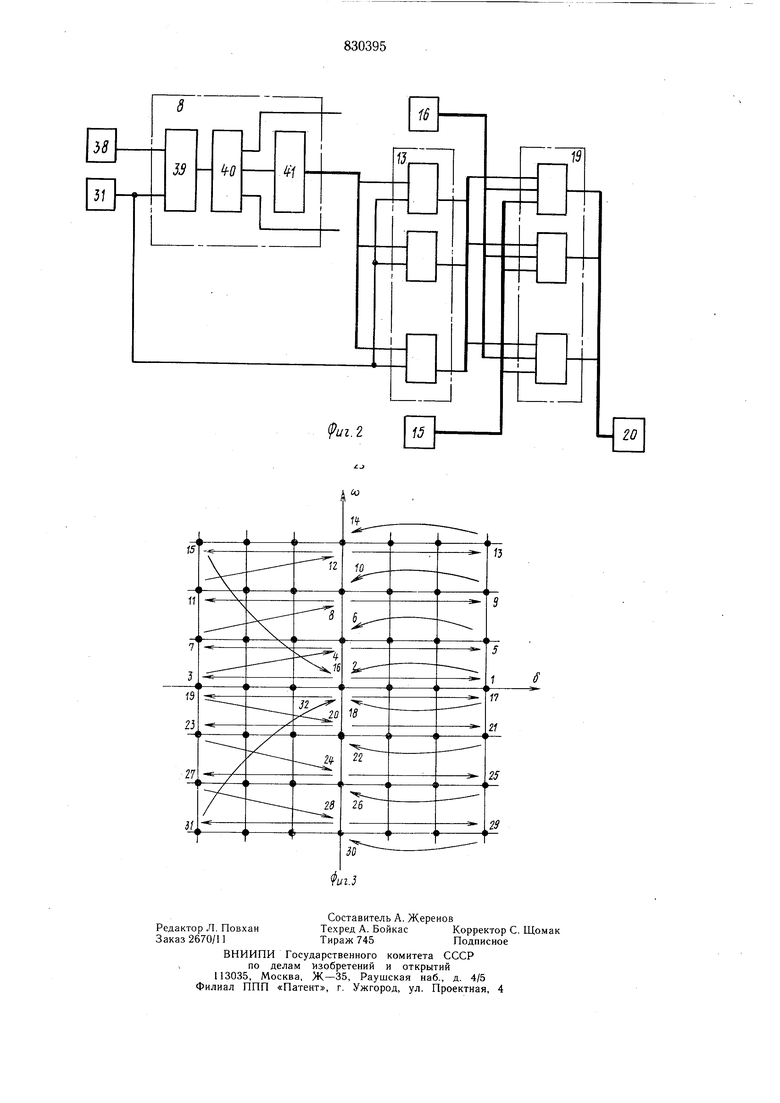

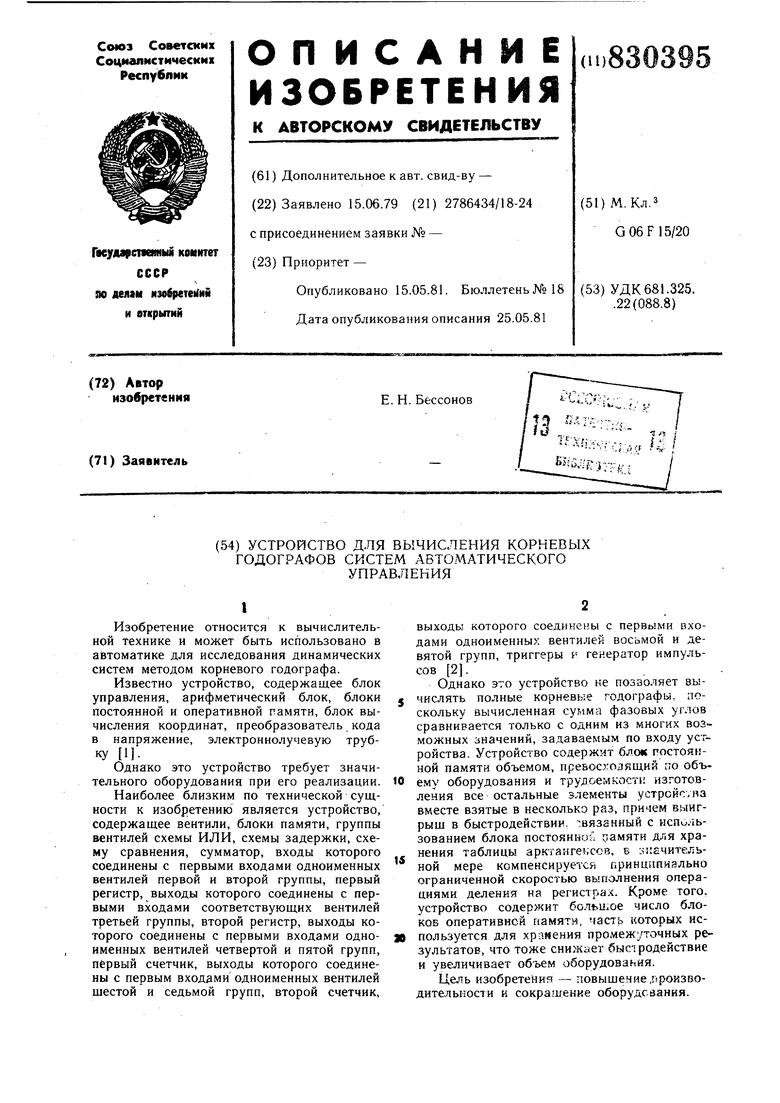

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - функциональные схемы блока памяти, группы элементов И, группы элементов ИЛИ и соответствующие внутрен;ние связи; на фиг. 3 - порядок исследования точек симметричной рабочей области плоскости собственных частот. Устройство содержит управляющий вход 1, информационные входы 2, управляющий выход 3, информационные выходы 4 и 5 триггеры 6 7, блок 8 памяти, счетчики 9 и 10, группы элементов И 11 -17, группы элементов ИЛИ 18 и 19, арифметический блок 20, регистры 21-23, схему 24 сравнения элемент 25 неравнозначности, элемент ИЛИ 26 и 27, генератор 28 импульсов, элемент И 29, распределитель 30 синхроимпульсов, элемент ИЛИ 31-36, элемент 37 и 38, счетчик 39 адреса, дещифратор 40, запоминающий узел 41. Устройство работает на основе следующего соотнощения: у+ Ыд 2 arctgf -- HLrarctgf;-f Orlо - Opj М -абсцисса и ордината иссле-дуемой точки плоскости; -абсциссы и ординаты полюсов передаточной функции разомкнутой цепи; О2м,сд)г.м -абсциссы и ординаты нулей передаточной функции разамкнутой цепи. f - число нулей; -фазовый угол коэффициента усиления разомкнутой цепи; N -0,,±1, ± 2, ± 2,... Вместо вычисления суммы арктангенсов достаточно произвести вычисления по рекуррентной формуле ш И 4fi i л « 9 п П+1- ir.5i.r 1-..---, П l-«Pt,4t n + m раз, приняв fi .- для полюсов. «fi V 0 0. Устройство работает следующим образом. Перед началом работы в блок памяти вводят последовательно cWp , Spt, tOp, , Sp, , Spa ,Ti. 4 ,i.i . Szi , .Jrm, xtT устанавливают в нуль триггеры, регистр 23, распределитель 30 синхроимпульсов, счетчик адреса блока памяти и счетчики. На вход 2 подается код тангенса фазового угла коэффициента усиления. Запуск устройства производят подачей сигнала на вход 1. При этом триггер 6 переходит в единичное состояние и разрещает прохождение импульсов генератора через элемент И 29 на вход распределителя 30. В первом такте работы распределителя 30 сигнал с его первого выхода иницирует занесение в арифметический блок 20 кода состояния счетчика 9, на котором находится значение AV, через группы элементов И 11 и элементов ИЛИ 18 и содержимое первой ячейки блока памяти через элементы И 13 и элементы ИЛИ 19. Одновременно через элемент ИЛИ 35 иницируется операция вычитания и арифметическом блоке 20 и через элемент ИЛИ 26 - занесение в регистр 2 результата операции в арифметическом блоке, который к концу первого такта принимает значение )р. Цепи синхронизации указанных действий условно не показаны. Аналогичным образом в следующих щести тактах производятся следующие действия. Занесение в арифметический блок содержимого счетчика 10, где находится код абсциссы исследумой точки плоскости и содержимого второй ячейки блока памяти, где находится код абсциссы первого полюса, инициирование операции вычитания в арифметическом блоке 20 и занесение результата операции в регистр 22 происходит во втором такте. После каждого обращения к блоку памяти происходит приращение на единицу содержимого счетчика адреса блока памяти. В. третьем такте в арифметический блок заносятся расстояния от исследуемой точки плоскости до первого полюса из регистров 21 и 22, инициируется операция деления, и Б регистр 21 заносится результат операции, представляющий собой аргумент первого арктангенса. В четвертом такте в арифметический блок 20 заносится полученный аргумент f из регистра 21 и результат, полученный по рекуррентной формуле в предыдущих семи тактах и хранящийся на регистре 23, вычисляется их произведение и заносится в регистр 22. В пятом такте в арифметический блок заносятся через группу элементов И 17 код числа «единица и вычисленное в предыдущем такте произведение из регистра 22, вычисляется их разность и заносится в тот же регистр. В щестом такте в арифметический блок заносятся слагаемь1е знаменатели рекуррентной формулы из регистров 21 и 23, производится сложение, и результат записывается в регистр 21. В последнем седьмом такте содержимое регистров 21 и 22 передается в арифметический блок, где производится деление и вычисляется новое значение по рекуррентной формуле, Которое заносится в регистр 23. При всех вычислениях в арифметическом блоке 20 в зависимости от его типа и возможностей по быстродействию на время выполнения операций, таких, например, как деление или умножение, возможно прекращение поступления импульсов на вход распределения через элементы 29 из-за исчезновения разрещения на выходе состояния арифметического блока до окончания исполнения операции в блоке. В течение следующих семи тактов повторяются все описанные действия, но уже с координатами следующего полюса. Когда все полюсы исчерпаны, сигнал с выхода дешифратора адреса блока памяти воздействуя на единичный вход триггера 7, переводит его в состояние «1 и с этого момента в третьем такте через элемент И 37 на один из входов схемы неравнозначности 25 поступает единичный логический уровень, и запись аргумента очередного арктангенса 6 регистр 21 производится с обратным знаком. Тем самым реализуется замена операции вычитания арктангенсов сложением.

При выполнении действия с последним из нулей передаточной функции во втором такте на выходе дешифратора появляется единичный логический уровень, благодаря чему в седьмом такте через элемент И 38 производится сброс счетчика адреса блока памяти, сброс триггера 7, изменение состояния счетчиков, сравнение величины igy на входе 2 с содержимыми регистра 23 и сброс названного регистра. В случае полного или частичного совпадения (схема сравнения не обязательно должна быть полноразрядной) сравниваемых величин на выходе схемы сравнения и устройства появляется сигнал, свидетельствующий о том, что на выходах 4 и 5 устройства код точки корневого годографа. Цепи синхронизации этих действий также условно не показаны. Оба счетчика представляют собой один счетчик, поскольку связь с управляющего выхода счетчика 9 на вход счетчика 10 можно трактовать как внутреннюю. При этом по сравнению с разрядностью регистров и арифметического блока в счетчиках могут отсутствовать младшие и старшие разряды. Отсутствие младших разрядов соответствует приращениям координат исследуемых точек большим, чем дискретность операндов, отсутствие старших разрядов соответствует границам рабочей области плоскости собственных частот. Старшие разряды любого из счетчиков или обоих могут пониматься по необходимости как знаковые. В этом случае рабочая область симметрична относительно осей координат. Каждый раз, когда происходит изменение состояния счетчика 10, счет чик 9 обнуляется. Таким образом, при перемещении по плоскости собственных частот в симметричной рабочей области точки исследуются в порядке, указанном на фиг. 3. В .момент обнуления ооомх счетчиков при их одновременном переполнении сигнал с выхода счетчика 0 сбрасывает триггер 6 и работа устройства прекращается, поскольку исследована вся рабочая область. Число исследуемых точек, каждая из которых проверяется на принадлежность корневому годографу, равно емкости счетчика, образован ного обоими счетчиками.

За счет полного использования регистров отсутствует необходимость запоминания промежуточных результатов вычислений в блоке памяти и сокращается его объем по сравнению с суммарным объемом блоков памяти известного устройства. За счет использования рекуррентной формулы, не содержащей функций арктангенса исключен блок постоянной памяти для хранения таблицы арктангенсов и превосходящий по объему оборудования и трудоемкости изготовления все остальные элементы устройства вместе взятые в несколько раз. Поскольку никакие действия вычислительного процесса не совмещены, все блоки памяти для хранения исходных данных объединены в один, так как это, уменьшая общий объем оборудования, не отражается на быстродействии устройства. Отсутствие в формуле вычислений произвольной целой величины позволяет вычислять полные, а не фрагментарные корневые годографы и полностью автоматизировать работу устройства.

Формула изобретения Устройство для вычисления корневых годографов систем автоматического управлен ия, содержащее генератор импульсов, распределитель синхросигналов, триггеры, счетчики, элементы И, элементы ИЛИ, блок памяти, схему сравнения, первый вход которой является информационным входом устройства, первый регистр, выход которого

соединен с первыми входами элементов И первой группы, второй регистр, выход которого соединен с первыми входами элементов И второй группы, третий регистр, отличающееся тем, что, с целью повышения производительности и сокращения оборудования, оно содержит арифметический блок, информационный выход которого соединен с информационными входами первого, второго и третьего регистров, выход знакового разряда арифметического блока соединен с первым входом элементг неравнозначности, выход которого с входами знаковых разрядов .ого из регистров, первый информационный вход арифметического блока соединен с выходами элементов ИЛИ первой группы, второй информационный

вход - с выходами элементов ИЛИ второй группы, вход деления арифметического блока подключен к выходу первого элемента ИЛИ к первому входу второго элемента ИЛИ, вход вычитания арифметического

Q блока, соединен с выходом третьего элемента ИЛИ, вход умножения арифметического блока соединен с первыми входами четвертого и пятого элементов ИЛИ и с соответствующим вь1ходом распределителя синхросигналов, вход сложения арифметического

5 блока соединен с вторым входом четвертого элемента ИЛИ, с первым входом шестого элемента ИЛИ и с соответствующим выходом распределителя синхросигналов, выход состояния арифметического блока соединен с первым входом первого элемента И, выход которого соединен с входом распределителя синхросигналов, первый управляющий выход блока памяти соединен с первым входом второго элемента И, выход которого соединен с управляющим входом бло5 ка памяти, нулевым входом первого триггера, входом первого счетчика, управляющими входами схемы сравнения и третьего регистра, второй управляющий выход блока памяти соединен с единичным входом первого триггера, вход блока памяти подключен к выходу седьмого элемента ИЛИ и к первым входам элементов И третьей группы, вторые входы которых соединены с информационным выходом блока памяти, выходы элементов И третьей группы соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И четвертой группы, первые входы которых и второй вход схемы сравнения соединены с выходом третьего регистра, третьи входы элементов ИЛИ второй труппы соединены с выходами элементов И второй группы, вторые входы которых соединены с выходом восьмого элемента ИЛИ, выходы элементов И первой группы соединены с первыми входами элементов ИЛИ первой группы, вторые входы которых соединены с выходами элементов И пятой группы, третьи входы - подключены к выходам элементов И шестой группы, Первые входы которых соединены с информационным выходом первого счетчика И с первым информационным выходом устройства, четвертые входы элементов ИЛИ первой группы соединены с выходами элементов И седьмой группы, первые входы которых подключены к информационному выходу второго счетчика и к второму информационному выходу устройства, вторые входы элементов И первой группы соединены с выходом второго элемента ИЛИ, выход четвертого элемента ИЛИ соединен с вторыми входами элементов И четвертой группы и с вторым входом второго элемента ИЛИ, управляющий выход первого счетчика соединен с входом второго счетчика, управляющий выход которого соединен с нулевым входом второго триггера, единичный вход которого является управляющим входом устройства.

выход второго триггера соединен с вторым входом первого элемента И, третий вход которого подключен к выходу генератора импульсов, выход первого триггера соединен с первым входом третьего элемента И, выход которого соединен с вторым входом элемента неравнозначности, вход первого регистра соединен с выходом шестого элемента ИЛИ, вход второго регистра соединен с выходом пятого элемента ИЛИ, выход схемы сравнения является управляющим выходом устройства, первые входы элементов И пятой группы являются входами устройства, выходы распределителя синхросигналов соединены соответственно с первым входом седьмого элемента ИЛИ, вторыми входами элементов И шестой группы, первым

входом третьего элемента ИЛИ, вторым входом щестого элемента ИЛИ, вторым входом седьмого элемента ИЛИ, вторыми входами элементов И седьмой группы, вторым входом третьего элемента ИЛИ, вторым входом пятого элемента ИЛИ, с первым входом восьмого элемента ИЛИ, первым входом первого элемента ИЛИ, третьим входом щеотого элемента ИЛИ, с вторым входом третьего элемента И, вторым входом восьмого элемента ИЛИ, третьим входом третьего

5 элемента ИЛИ, вторыми входами элементов И пятой группы, с третьим входом пятого элемента ИЛИ, третьим входом восьмого элемента ИЛИ, вторым входом первого элемента ИЛИ, с входом третьего регистра и с вторым входом второго элемента И.

Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР № 512474, кл. G Об F 15/46, 1974.

2. Авторское свидетельство СССР № 408313, кл. G Об F 15/34, 1972 (прототип).

Д

/

4У

16

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

| УСТРОЙСТВО для ВЫЧИСЛЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УНРАВЛЕНИЯ1Изобретение относится к автоматике и телемеханике и предназначено для исследования динамических свойств систем автоматического управления.Известны устройства для построения корневых годографов систем автоматического управления, содержащие вентили, группы вентилей, блоки памяти, схемы ИЛИ, схемы задержки, схему сравнения, сумматор, выходы которого соединены с первыми входами одноименных вентилей первой и второй групп, первый регистр, выходы которого соединены с первыми входами соответствующих вентилей третьей группы, второй регистр, выходы которого соединены с первыми входами одноименных вентилей четвертой и пятой групп, первый счетчик, выходы которого соединены с первыми входами одноименных вентилей ще- стой и седьмой групп, второй счетчик, выходы которого соединены с первыми входами одноименных вентилей восьмой и девятой групп, триггеры и генератор импульсов.Однако известные устройства имеют недостаточное быстродействие, невысокую точность работы и ограниченные функциональные возможности. | 1973 |

|

SU408313A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для записи информации в оперативную память | 1982 |

|

SU1049966A1 |

| Устройство для обработки радиосигналов | 1980 |

|

SU955083A1 |

(.2

4

15

3

Авторы

Даты

1981-05-15—Публикация

1979-06-15—Подача