1

Изобретение относится к вычислительной технике, в частности к интегральным постоянным запоминающим устройствам (ПЗУ).

Известны адресные формирователи, выполненные по схеме основного элемента транзисторно-транзнсторной логики 1. Паиболее близким к изобретению техническим решением является адресный формирователь, содерл :ащий три транзистора, диод, два резистора, входную и выходную шины, шину питания и шину нулевого потенциала, причем база первого транзистора соединена с входной шиной, коллектор соединен с базой третьего транзистора и через первый резистор - с шиной нитания, эмиттер соединен с базой второго транзистора и через второй резистор - с шиной нулевого потенциала, эмиттер третьего транзистора соединен с анодом первого диода, катод которого соединен с выходной шиной и коллектором второго транзистора, эмиттер которого соединен с шиной нулевого потенциала 2. Однако известный формирователь имеет низкое выходное сопротивление в режиме записи информации.

Целью изобретения является повышение надежности и уменьшение потребляемой мошности в режиме записи информации. В описываемом формирователе это достигается тем, что он содержит четвертый и пятый транзисторы, второй и третий диоды, третий, четвертый и

пятый резисторы, причем эмиттер пятого транзистора соединен с коллектором третьего транзистора, коллектор соединен с шиной питаиия, а база - через третий резистор с шиной питания и коллектором четвертого транзистора, эмиттер которого непосредственно, а база через пятый резистор подключены к шипе нулевого потенциала и аноду второго диода, катод которого соединен с выходной шиной, анод третьего диода через четвертый резистор подключен к базе четвертого транзистора, а катод- к шине питания.

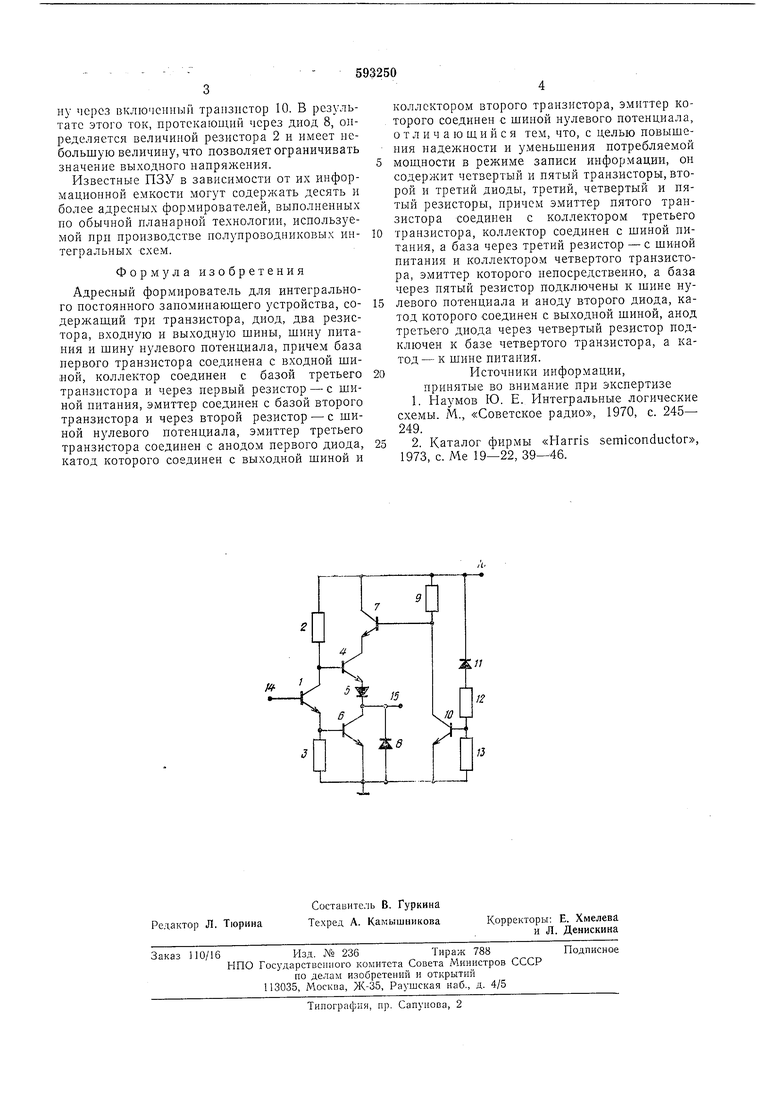

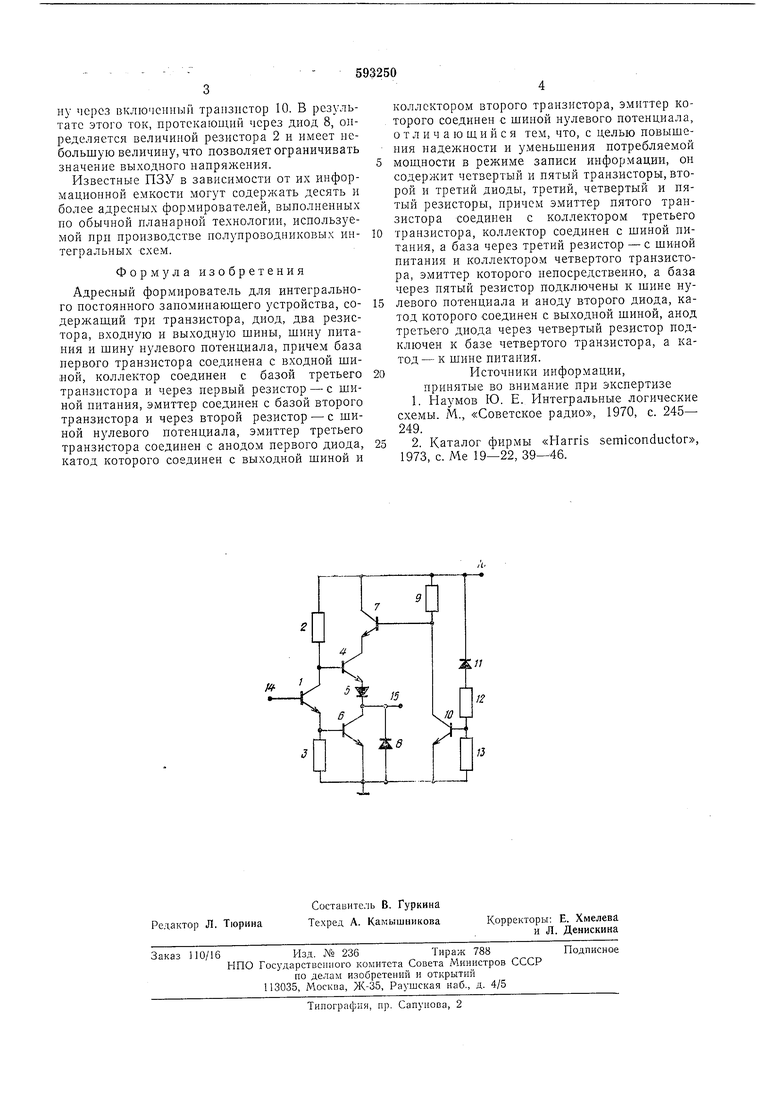

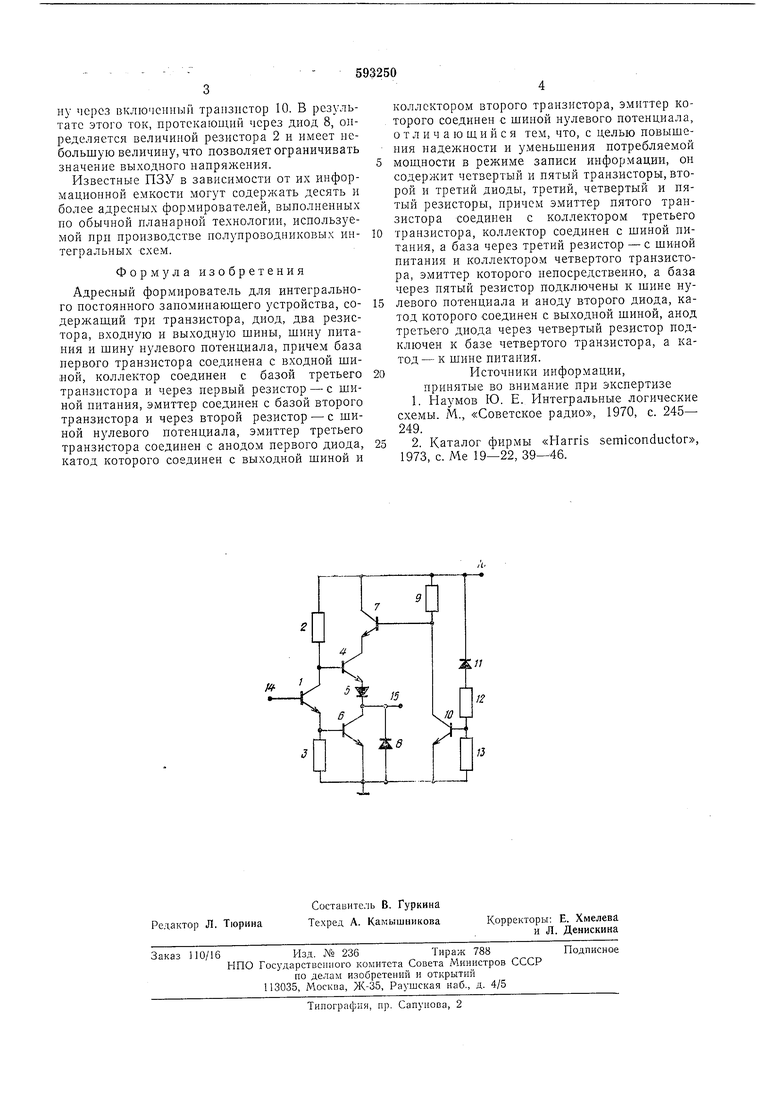

На чертеже представлена электрическая схема описываемого формирователя.

Он содержит первый транзистор 1, первый резистор 2, второй резистор 3, третий транзистор 4, первый диод 5, второй транзистор 6, пятый транзистор 7, второй диод 8, третий резистор, 9, четвертый транзистор 10, третий диод 11, четвертый резистор 12, пятый резистор 13, входную шину 14, выходную шину 15 и шину питания 16.

При работе адресного формирователя в режиме заниси информации при повышении напряжения источника питания до величииы, необходимой для записи информации, диод 11 пробивается, ток через резистор 12 протекает в базу транзистора 10 и включает его, транзистор 7 выключается, так как ток резистора 9 не поступает в его базу, а течет в общую шнну через включенный транзистор 10. В результате этого ток, протекающий через диод 8, онределяетея величиной резистора 2 и имеет небольшую величину, что позволяет ограничивать значение выходного напряжения.

Известные ПЗУ в зависимости от их информационной емкости могут содержать десять и более адресных формирователей, выполненных по обычной Планерной технологии, используемой при производстве полупроводниковых интегральных схем.

Формула изобретения

Адресный формирователь для интегрального постоянного запомииающего устройства, содержащий три транзистора, диод, два резистора, входную и выходную щины, шину питания и щину нулевого потенциала, причем база первого транзистора соединена с входной шиной, коллектор соединен с базой третьего транзистора и через первый резистор - с шиной питания, эмиттер соединен с базой второго транзистора и через второй резистор - с шиной нулевого потенциала, эмиттер третьего транзистора соединен с анодом первого диода, катод которого соединен с выходной шиной и

коллектором второго транзистора, эмиттер которого соединен с шиной нулевого потенциала, отличающийся тем, что, с целью повышения надежности и уменьшения потребляемой мощности в режиме записи информации, он содержит четвертый и пятый транзисторы, второй и третий диоды, третий, четвертый и пятый резисторы, причем эмиттер пятого трапзистора соединеи с коллектором третьего транзистора, коллектор соединен с шиной питания, а база через третий резистор - с шиной питания и коллектором четвертого транзистора, эмиттер которого непосредственно, а база через пятый резистор подключены к шине нулевого потенциала и аноду второго диода, катод которого соединен с выходной шиной, анод третьего диода через четвертый резистор подключен к базе четвертого транзистора, а катод - к шине питания.

Источники информации, принятые во внимание при экспертизе

1.Наумов Ю. Е. Интегральные логические схемы. М., «Советское радио, 1970, с. 245- 249.

2.Каталог фирмы «Harris semiconductor, 1973, с. Me 19-22, 39-46.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор запоминаюшего устройства | 1979 |

|

SU871330A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Формирователь уровня считывания | 1984 |

|

SU1244718A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Интегральный элемент памяти | 1977 |

|

SU858102A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Устройство для выборки информации из накопителя | 1983 |

|

SU1141451A1 |

| Формирователь импульсов | 1979 |

|

SU809353A1 |

/J

Авторы

Даты

1978-02-15—Публикация

1975-12-26—Подача