1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в блоках опорной частоты или задающих генераторах, различных системах обработки преобразования и передачи информации, к которым предъявляются повышенные требования стабильности и надежности работы.

Известен резервированный делитель частоты, содержащий резервные счетчики, мажоритарные элементы и дешифраторы состояний.

Однако такие устройства характеризуются невысокими помехоустойчивостью и быстродействием.

В предлагаемом делителе частоты в каждый канал введен элемент «И-НЕ, выход которого подключен к установочному входу первого разряда резервного счетчика, а входы соединены с выходом дешифратора состояний, с инверсным выходом мажоритарного элемента и с инверсным выходом источника входных сигналов.

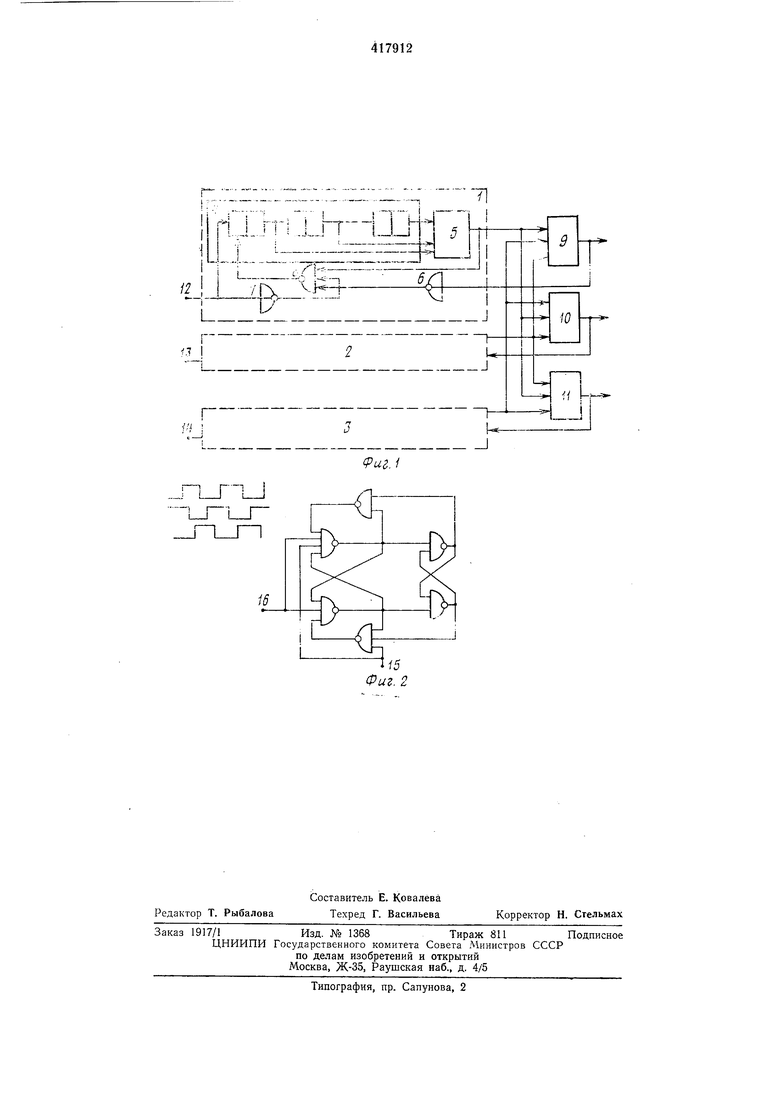

На фиг. 1 показана блок-схема делителя частоты; на фиг. 2 приведен пример выполнения первого разряда счетчика.

Резервированный делитель частоты содержит резервные каналы (например, три) 1, 2 и 3, каждый из которых состоит из счетчика 4 импульсов, дешифратора 5, инвертирующих каскадов 6, 7 и логического элемента «И-

НЕ 8, мажоритарные элементы 9, 10 и 11, входные шины 12. 13 н 14, установочный вход 15 и счетный в.од 16 первого разряда. Делитель работает следующим образом.

Сигнал по шинам 12, 13, 14 поступает на входы счетчиков импульсов и через инвертирующий каскад на первый вход логической схемы «И-НЕ каждого канала. При установке всех разрядов счетчика 4, например, в

«1, на выходе дешифратора появляется сигнал, который поступает на входы мажоритарных элементов 9, 10, 11 и на второй вход логического элемента «И-НЕ своего канала. При совпадении двух сигналов на входах мажоритарных элементов на их выходах появляются сигналы, которые через инвертирующие каскады закрывают по третьему входу элементы «И-НЕ. Таким образом, при синхронной работе всех каналов на выходах логических элементов «И-НЕ всегда действует единичный потенциал, который не влияет на работу счетчиков импульсов.

В случае возникновения сбоя, например, в канале 1 (аналогично могут быть рассмотрены сбои в каналах 2 или 3), на выходе дещифратора 5 канала 1 появляется сигнал, опережающий сигналы на выходах дещифраторов других каналов, который нрикладывается к второму входу логического элемента

«И-НЕ. При этом на выходе мажоритарного элемента 9 действует нулевой потенциал, который инвертируется каскадом бив виде единичного потенциала действует на третий вход логического элемента «И-НЕ. По окончании действия входного импульса но шине 12 на выходе инвертирующего каскада 7 появляется единичный нотенциал. С приходом этого потенциала иа первый вход логического элемента «И-НЕ на его выходе возникает нулевой потенциал.

Поскольку выход логического элемента «И-НЕ соединен с установочным входом 15 первого разряда счетчика импульсов, счетные импульсы, поступающие по щиие 12 на счетный вход 16 первого разряда, не меняют его состояния. В этом состоянии счетчик импульсов находится до тех пор пока на выходе элемента 9 не появится сигнал, который через инвертирующий каскад б закрывает логическую схему «И-НЕ по третьему входу. В этот момент все разряды счетчиков импульсов каналов 1, 2, 3 находятся в состояниях, определяемых дещифраторами 5.

Установившийся единичный потенциал на выходе логического элемента «И-НЕ не препятствует поступлению имнульсов с шины 12 в счетчик импульсов 4. Таким образом, при поступлении счетных импульсов по шинам 12, 13, 14 обеспечивается сипхронно-синфазный режим работы всех каналов резервированного

делителя частоты. Выход из строя одного из каналов не приводит к искажению выходных сигналов. Благодаря этому обеспечивается высокая надежность делителя частоты. Кроме того, предлагаемый делитель обладает повышенным быстродействием, так как в процессе нормальной работы на установочные входы разрядов счетчиков импульсов не поступают синхронизирующие сигналы, и

быстродействие делителя частоты определяется быстродействием этих счетчиков импульсов. Отсутствие связей в цепях установки разрядов счетчиков импульсов повыщает помехоустойчивость и упрощает резервированный делитель частоты.

Предмет изобретения

Резервированный делитель частоты, содержащий резервные счетчики, мажоритарные элементы и дешифраторы состояний, отличающийся тем, что, с целью упрощения, повышения помехоустойчивости и увеличения быстродействия, в каждый канал введен элемент «И-НЕ, выход которого подключен к установочному входу первого разряда резервного счетчика, а входы соединены с выходом дешифратора состояний, с инверсным выходом мажоритарного элемента и с инверсным выходом источника входных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетное резервированное устройство | 1986 |

|

SU1354413A1 |

| Распределитель импульсов | 1979 |

|

SU809134A1 |

| Резервированный делитель частоты | 1983 |

|

SU1163473A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Резервированный делитель частоты | 1977 |

|

SU645282A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Резервированное многоканальное устройство | 1981 |

|

SU1058098A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Устройство для регулирования и защиты энергоагрегата | 1986 |

|

SU1442691A1 |

Даты

1974-02-28—Публикация

1972-05-04—Подача