1

Предлагаемое изобретение относится к области вычислительной техники и может быть применено в устройствах управления цифровых вычислительных машин.

Известны устройства микропрограммного управления, содержащие запоминаюиию устройства, регистры, ден1ифратор, элементы задержки, генератор тактовых импульсов.

Целью изобретения является унрощение устройства и повышение его быстродействия,

Устройство отличается от известных тем, что в пем имеется только один дешифратор для двух запомипаюш,их устройств, в одном из которых запоминается последовательность адресов микрокоманд, составляющих микропрограмму, а в другом - операционные части микрокоманд.

Выход одного разряда первого ЗУ подкл10чается к первы.м входам элементов «И изменения адреса, ко вторым входам которых подключаются выходы разрядов кода операций регистра команд.

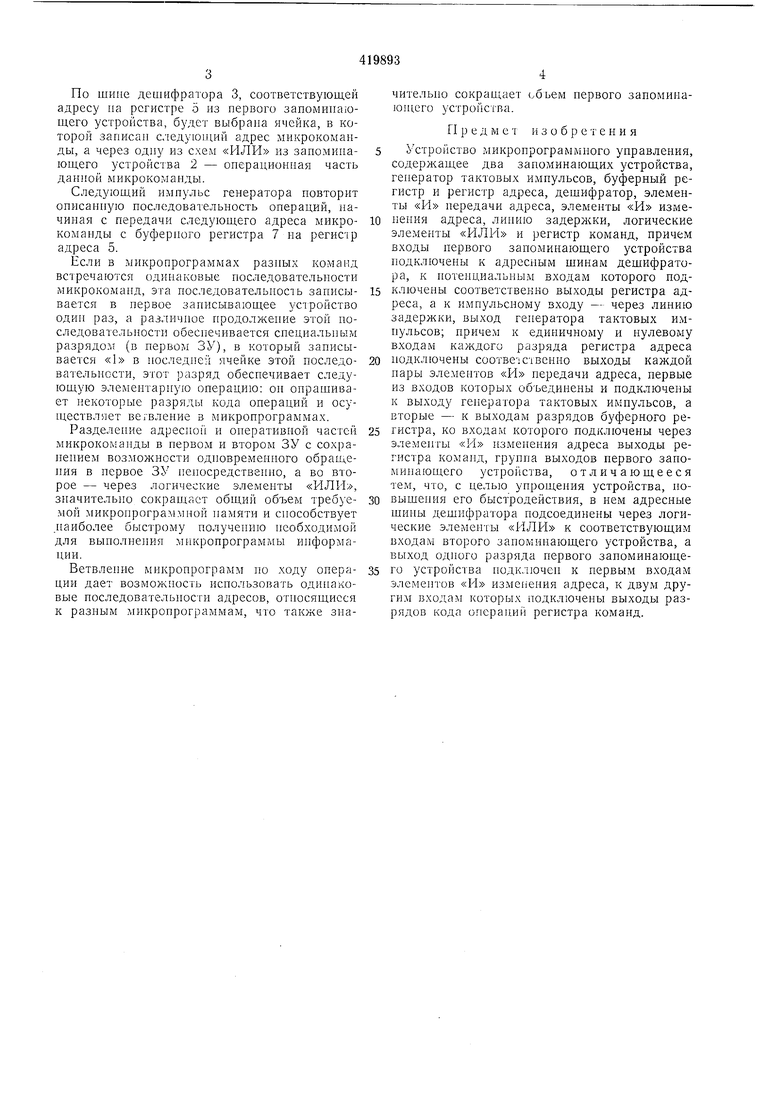

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит заноминающее устройство 1, в котором запоминается последовательность следующих один за другим адресс.ш микрокоманд; запоминающее устройство 2, в котором запоминаются операционные части микрокоманд; дешифратор 3, расщифровыва2

ющий следующий адрес микрокоманды; группу логических элементов «ИЛИ 4, на входах которых собирается a;ipeciibie шнны дешифратора 3, относящиеся к различным ячейкам первого запоминающего устройства, выходы которых выбирают одну ячейку во втором запоминающем устройстве 2; регистр адреса 5, группу элементов «II 6, через которые передается адрес с регистра 7, для запоминания следующего адреса мнкрокоманды на региегр адреса 5; элемент задержки 8, генератор имнульсов 9, который унравляет передачей следующего адреса мнкрокоманды из регистра 7 в регистр адреса 5, а через элемент задержки 8 осуществляет пуск дешифратора 3 и установку в «О регистра задержки 7; группу элементов «II вентилей 10, которые при помощи сиециальиой элементарной операции, задаваемой разрядом в пepвo.i запоминающем устройстве, онращи.вают разряды кода операции и изменяют следующий адрес микрокоман.:1,ы на регистре 7; регистр команд П.

Предлагаемое ycTpoiiCTBo работает следующим образом.

Код операции из регистра комаид передается на буферный регистр 7. Генератор импульсов передает этот a,apec через группу элементов «И на регистр адреса 5. а через элеме;гг задержки 8 осуществляет пуск дещифратора 3 и установку в «О буферного регистра 7.

3

По шине дешифратора 3, соответствуюш,ей адресу па регистре 5 из первого запомипаюш,его устройства, будет выбрана ячейка, в которой записан следующий адрес микрокоманды, а через одну из схем «ИЛИ из заномипающего устройства 2 - онерационная часть данной микрокоманды.

Следуюший имнульс генератора повторит описанную последовательность операций, начиная с передачи следуюш,его адреса микрокоманды с буферного регистра 7 на регистр адреса 5.

Если в микропрограммах разных команд встречаются одинаковые носледовательпости микрокоманд, эта последовательность записывается в нервое запнсываюш.ее устройство один раз, а различное продолжение этой носледовательпости обеспечивается специальным разрядом (в первом ЗУ), в который записывается «1 в последней ячейке этой последовательности, этот разряд обеспечивает следуюшую элемеитариую операцию: он опрашивает некоторые разряды кода операций и осунгествляет ветвление в микропрограммах.

Разделепие адрееной и онеративпой частей микрокоманды в первом и втором ЗУ с сохраиепием возможности одиовременного обращения в первое ЗУ непосредственно, а во второе - через логические элементы «ИЛИ, значительно сокращает общий объем требуемой микропрограммной памяти и способствует .паиболее быстрому получению необходимой для вынолпения микропрограммы информации.

Ветвление микропрограмм но ходу операции дает возможность использовать одипаковые последовательностей адресов, относящиеся к разным микропрограммам, что также значительно сокращает ьоъем нервого запоминаюн1его устройства.

Г1 р е д м е т и з о б р е т е н и я

Устройство микропрограммного управления, содержащее два запоминающих устройства, геператор тактовых импульсов, буферный регистр и регистр адреса, дешифратор, элементы «И передачи адреса, элементы «И изменения адреса, линию задержки, логические элементы «РШИ и регистр команд, причем входы первого запоминающего устройства подключены к адресным шинам дешифратора, к потенциальным входам которого подключены соответственно выходы регистра адреса, а к импульсному входу - через линию задержки, выход генератора тактовых имнульсов; причем к едипичному и пулевому входам каждого разряда регистра адреса

подключены соответственно выходы каждой нары элементов «И передачи адреса, первые из входов которых объединены и подключены к выходу генератора тактовых имнульсов, а вторые - к выходам разрядов буферного регистра, ко входам которого подключены через элеменгы «И изменения адреса выходы регистра команд, группа выходов первого запомипающего устройства, отличающееся тем, что, с целью упрощения устройства, повыщепия его быстродействия, в нем адресные щины дешифратора подсоединеиы через логические элементы «ИЛР1 к соответствующим входам второго заномннающего устройства, а выход одного разряда первого запоминающего устройства подключен к первым входам элементов «И изме11ения адреса, к двум другим Bxo;iaM которых подключены выходы разрядов кода операций регистра команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| УСТРОЙСТВО для МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1968 |

|

SU217066A1 |

| Микропрограммное устройство для управления обменом управляющей информацией в распределенной системе | 1986 |

|

SU1325477A1 |

| Адаптивное микропрограммное устройство управления | 1980 |

|

SU934471A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Устройство микропрограммного управления | 1981 |

|

SU1003086A1 |

| Адаптивное устройство микропрограммного управления | 1984 |

|

SU1290317A1 |

| Устройство микропрограммного управления | 1980 |

|

SU922742A1 |

| Устройство микропрограммного управления | 1972 |

|

SU482744A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Даты

1974-03-15—Публикация

1972-01-11—Подача