Изобретение относится к вычислительной технике и может быть использовано при построении управляющих и вычислительных систем высокой производительности.

Целью изобретения является расширение области применения устройства за счет реализации транзитной передачи микрокоманд управления.

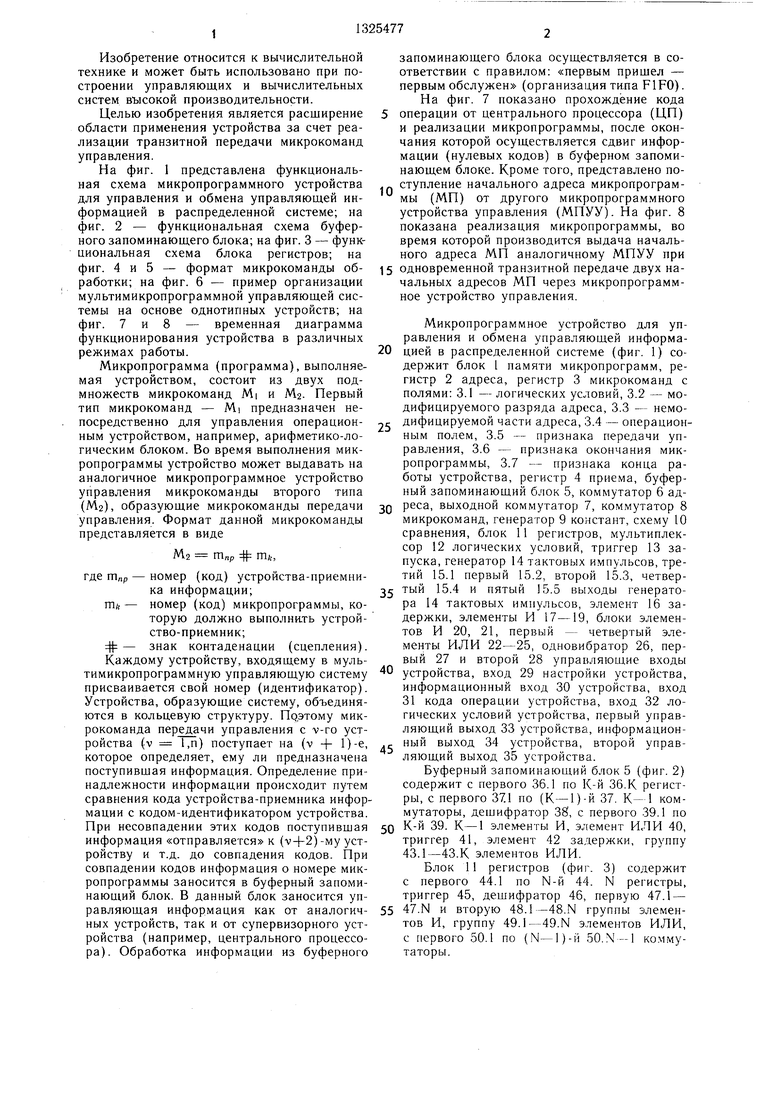

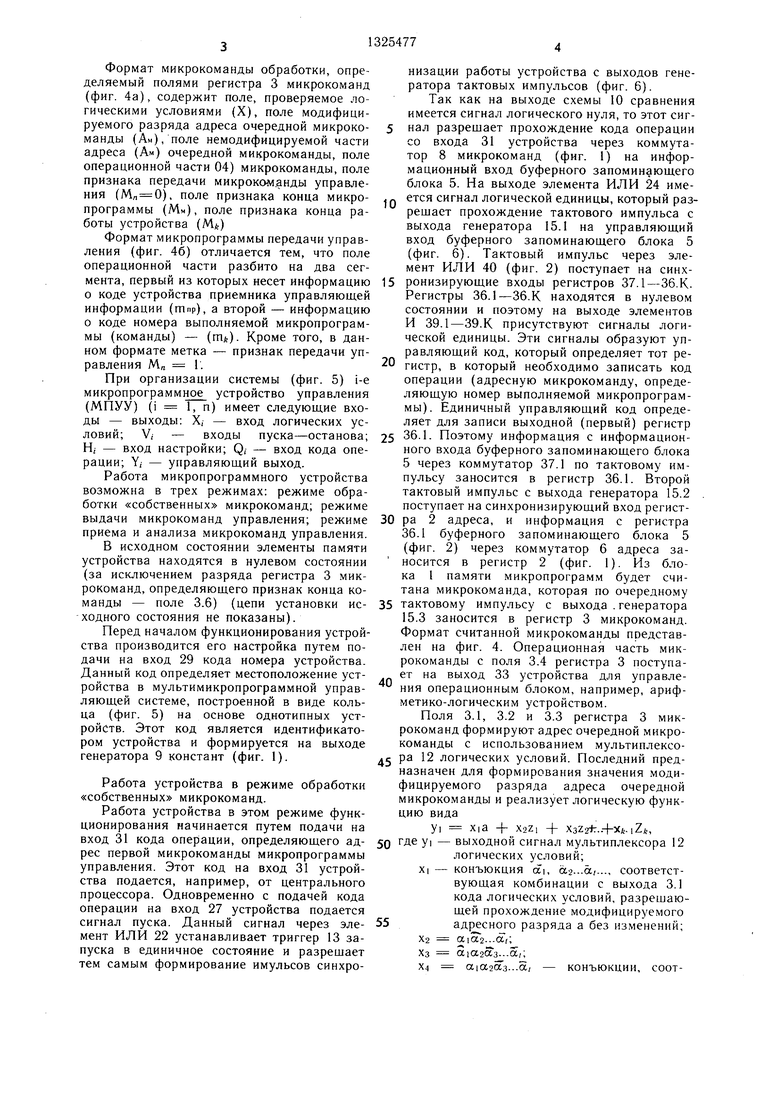

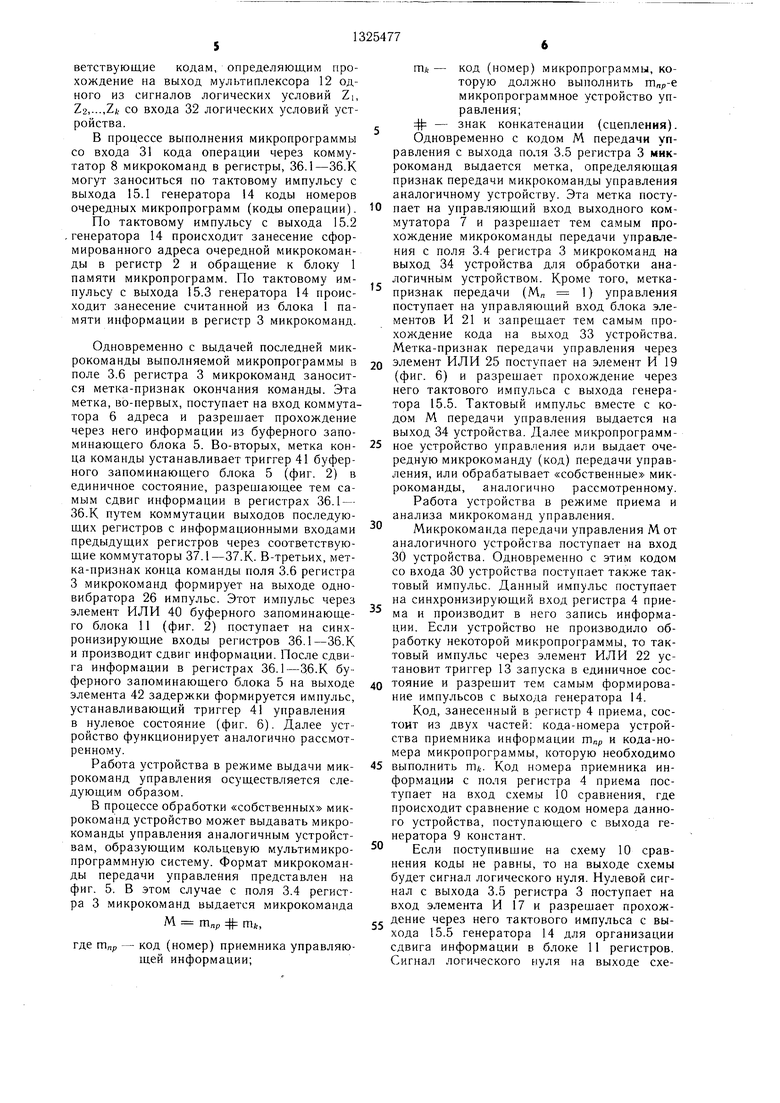

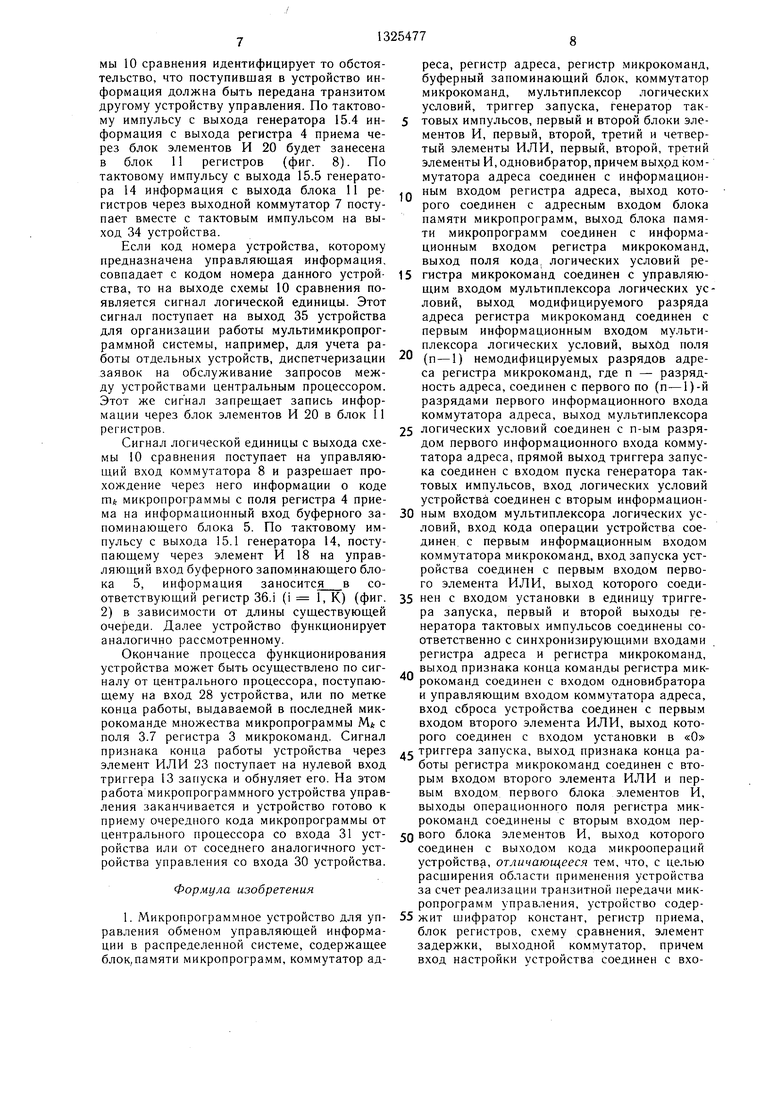

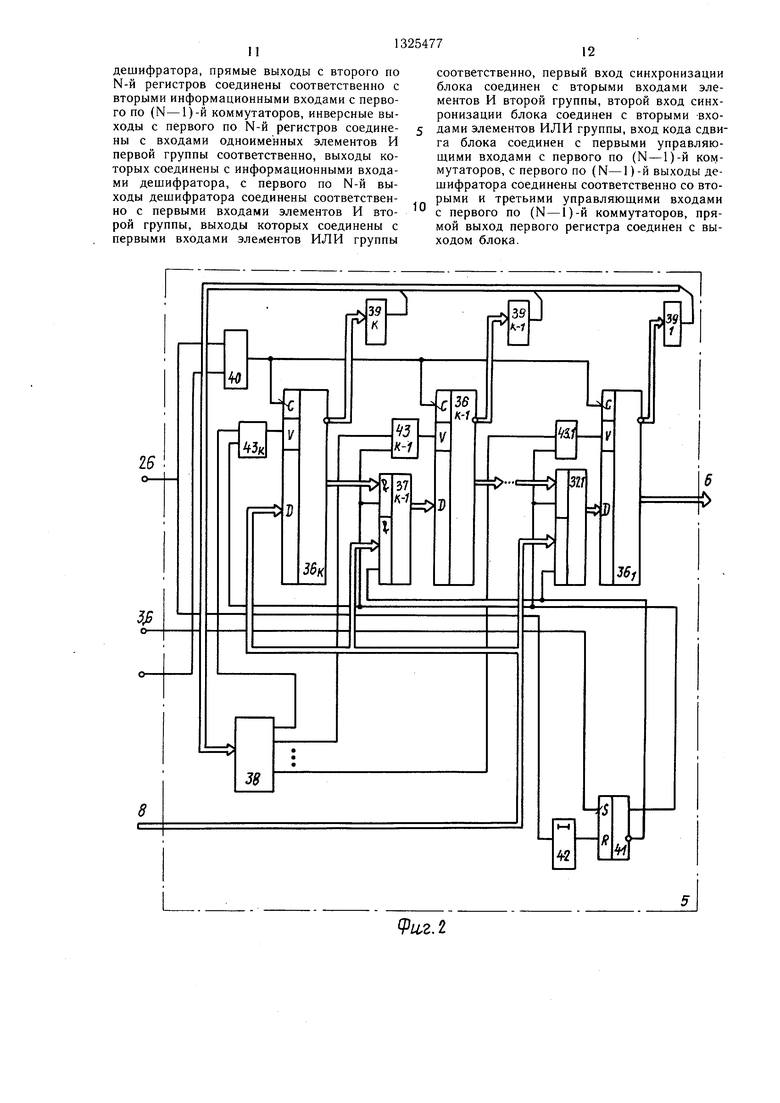

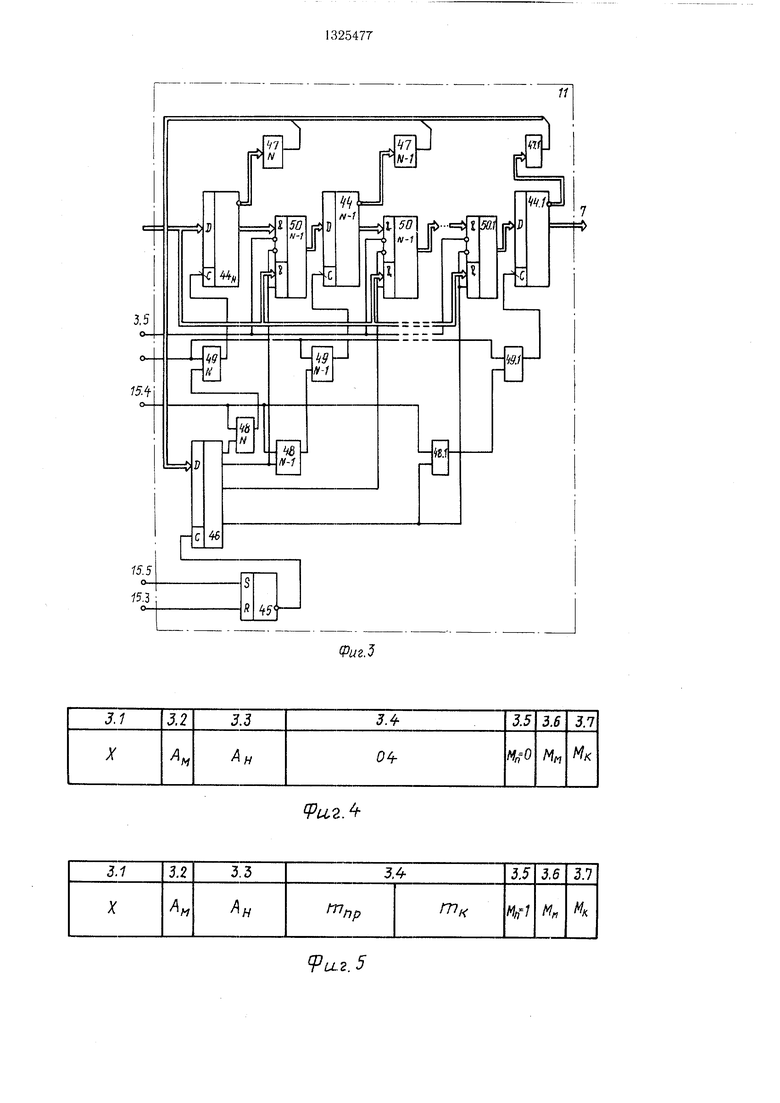

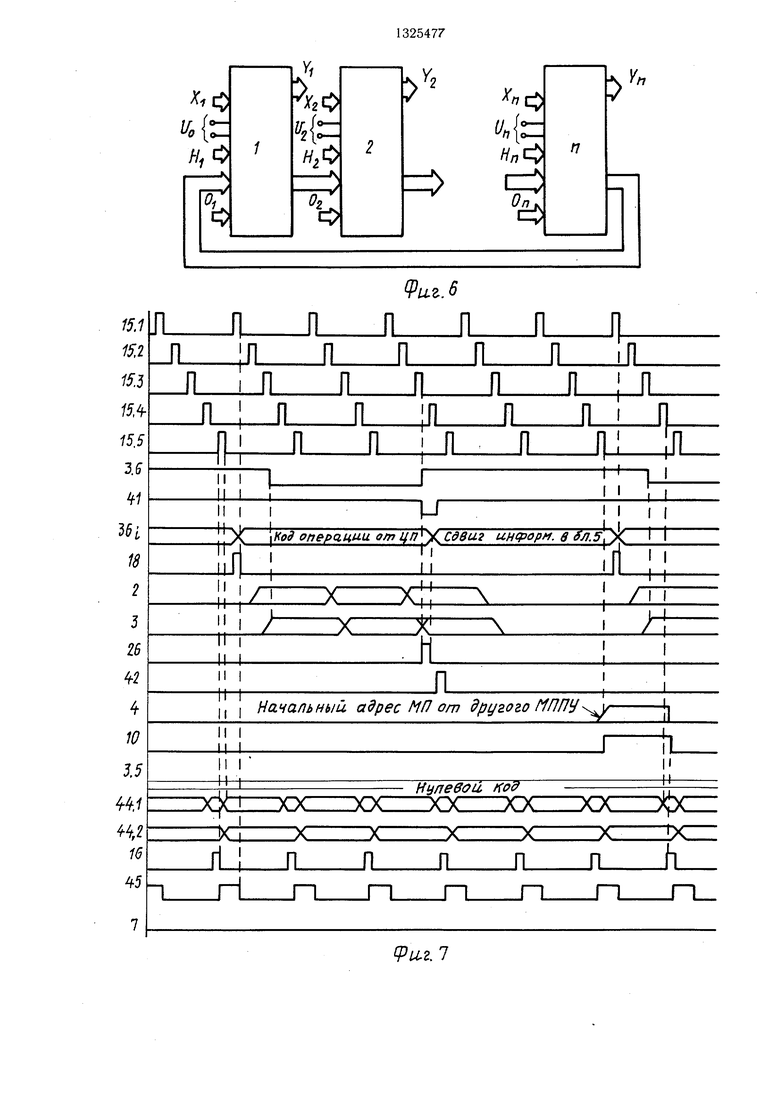

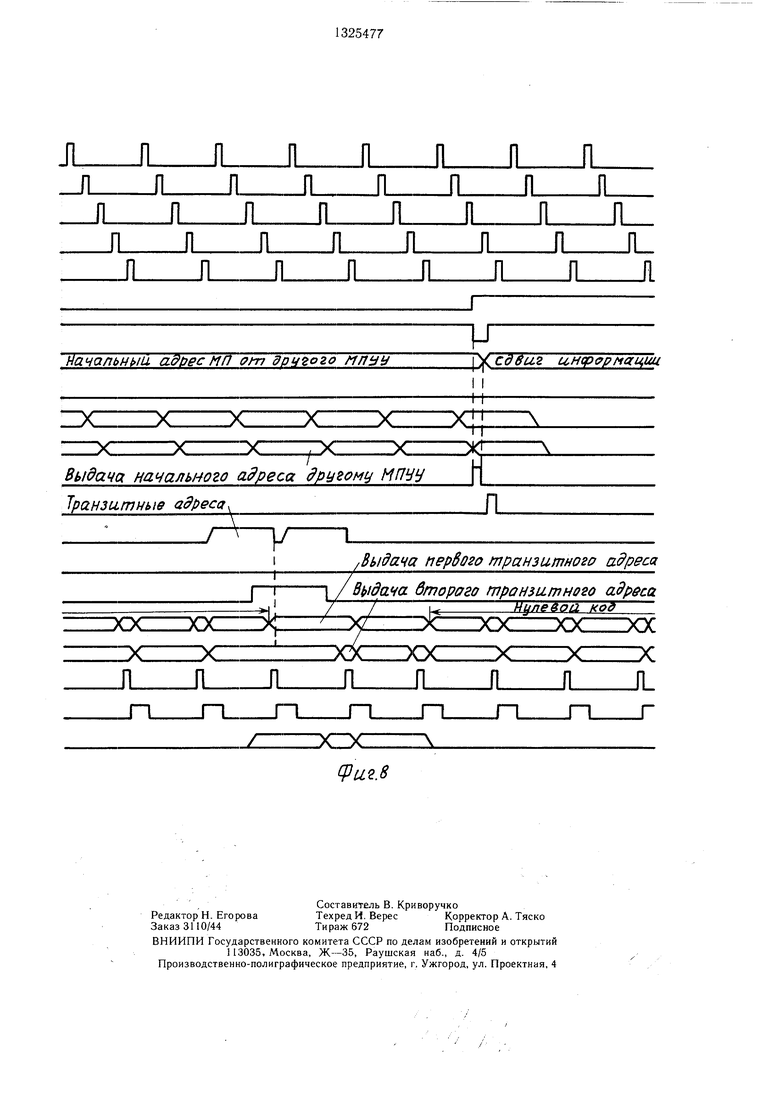

На фиг. 1 представлена функциональная схема микропрограммного устройства для управления и обмена управляющей информацией в распределенной системе; на фиг. 2 - функциональная схема буферного запоминающего блока; на фиг. 3 - функциональная схема блока регистров; на фиг. 4 и 5 - формат микрокоманды обработки; на фиг. 6 - пример организации мультимикропрограммной управляющей системы на основе однотипных устройств; на фиг. 7 и 8 - временная диаграмма функционирования устройства в различных режимах работы.

Микропрограмма (программа), выполняемая устройством, состоит из двух подмножеств микрокоманд Mi и М2. Первый тип микрокоманд - Mi предназначен непосредственно для управления операционным устройством, например, арифметико-логическим блоком. Во время выполнения микропрограммы устройство может выдавать на аналогичное микропрограммное устройство управления микрокоманды второго типа (М2), образующие микрокоманды передачи управления. Формат данной микрокоманды представляется в виде

М2 т„р ф mt,

где т„р - номер (код) устройства-приемника информации;

ш/г - номер (код) микропрограммы, которую должно выполнять устройство-приемник;

ф- знак контаденации (сцепления).

Каждому устройству, входящему в муль- тимикропрограммную управляющую систему присваивается свой номер (идентификатор). Устройства, образующие систему, объединяются в кольцевую структуру. Прэтому микрокоманда передачи управления с v-ro устройства (v 1,п) поступает на (v 1)-е, которое определяет, ему ли предназначена поступивщая информация. Определение принадлежности информации происходит путем сравнения кода устройства-приемника информации с кодом-идентификатором устройства. При несовпадении этих кодов поступившая информация «отправляется к (v+2) -му устройству и т.д. до совпадения кодов. При совпадении кодов информация о номере микропрограммы заносится в буферный запоминающий блок. В данный блок заносится управляющая информация как от аналогичных устройств, так и от супервизорного устройства (например, центрального процессора). Обработка информации из буферного

запоминающего блока осуществляется в соответствии с правилом: «первым прищел - первым обслужен (организация типа FIFO). На фиг. 7 показано прохождение кода

операции от центрального процессора (ЦП) и реализации микропрограммы, после окончания которой осуществляется сдвиг информации (нулевых кодов) в буферном запоминающем блоке. Кроме того, представлено поступление начального адреса микропрограммы (МП) от другого микропрограммного устройства управления (МПУУ). На фиг. 8 показана реализация микропрограммы, во время которой производится выдача начального адреса МП аналогичному МПУУ при

5 одновременной транзитной передаче двух начальных адресов МП через микропрограммное устройство управления.

Микропрограммное устройство для управления и обмена управляющей информа0 цией в распределенной системе (фиг. 1) содержит блок 1 памяти микропрограмм, регистр 2 адреса, регистр 3 микрокоманд с полями: 3.1 - логических условий, 3.2 - модифицируемого разряда адреса, 3.3 - немо5 дифицируемой части адреса, 3.4 - операционным полем, 3.5 - признака передачи управления, 3.6 - признака окончания микропрограммы, 3.7 - признака конца работы устройства, регистр 4 приема, буферный запоминающий блок 5, коммутатор 6 адQ реса, выходной коммутатор 7, коммутатор 8 микрокоманд, генератор 9 констант, схему 10 сравнения, блок 11 регистров, мультиплексор 12 логических условий, триггер 13 запуска, генератор 14 тактовых импульсов, третий 15.1 первый 15.2, второй 15.3, четвер5 тый 15.4 и пятый 5.5 выходы генератора 14 тактовых импульсов, элемент 16 задержки, элементы И 17-19, блоки элементов И 20, 21, первый - четвертый элементы ИЛИ 22-25, одновибратор 26, первый 27 и второй 28 управляющие входы

0 устройства, вход 29 настройки устройства, информационный вход 30 устройства, вход 31 кода операции устройства, вход 32 логических условий устройства, первый управляющий выход 33 устройства, информацион ный выход 34 устройства, второй управляющий выход 35 устройства.

Буферный запоминающий блок 5 (фиг. 2) содержит с первого 36.1 по К-й 36.К регистры, с первого 37 по (К-1)-й 37. К-1 коммутаторы, дешифратор 38, с первого 39.1 по

0 К-й 39. К-1 элементы И, элемент ИЛИ 40, триггер 41, элемент 42 задержки, группу 43.1-43.К элементов ИЛИ.

Блок 11 регистров (фиг. 3) содержит с первого 44.1 по N-й 44. N регистры, триггер 45, дешифратор 46, первую 47.1 -

5 47.N и вторую 48.1-48.N группы элементов И, группу 49.1-49.N элементов ИЛИ, с первого 50.1 по (N-1)-й 50.N-1 коммутаторы.

Формат микрокоманды обработки, определяемый полями регистра 3 микрокоманд (фиг. 4а), содержит поле, проверяемое логическими условиями (X), поле модифицируемого разряда адреса очередной микрокоманды (Ам), поле немодифицируемой части адреса (Ам) очередной микрокоманды, поле операционной части 04) микрокоманды, поле признака передачи микрокоманды управления (), поле признака конца микропрограммы (Мм), поле признака конца работы устройства (М)

Формат микропрограммы передачи управления (фиг. 46) отличается тем, что поле операционной части разбито на два сегмента, первый из которых несет информацию о коде устройства приемника управляющей информации (mnp), а второй - информацию о коде номера выполняемой микропрограммы (команды) - (т/г). Кроме того, в данном формате метка - признак передачи управления М„ 1.

При организации системы (фиг. 5) i-e микропрограммное устройство управления (МПУУ) (i 1, п) имеет следующие входы - выходы: X, - вход логических условий; V, - входы пуска-останова; Н, - вход настройки; Q, - вход кода операции; Y, - управляющий выход.

Работа микропрограммного устройства возможна в трех режимах: режиме обработки «собственных микрокоманд; режиме выдачи микрокоманд управления; режиме приема и анализа микрокоманд управления.

В исходном состоянии элементы памяти устройства находятся в нулевом состоянии (за исключением разряда регистра 3 микрокоманд, определяющего признак конца команды - поле 3.6) (цепи установки исходного состояния не показаны).

Перед началом функционирования устройства производится его настройка путем подачи на вход 29 кода номера устройства. Данный код определяет местоположение устройства в мультимикропрограммной управляющей системе, построенной в виде кольца (фиг. 5) на основе однотипных устройств. Этот код является идентификатором устройства и формируется на выходе генератора 9 констант (фиг. 1).

Работа устройства в режиме обработки «собственных микрокоманд.

Работа устройства в этом режиме функционирования начинается путем подачи на вход 31 кода операции, определяющего адрес первой микрокоманды микропрограммы управления. Этот код на вход 31 устройства подается, например, от центрального процессора. Одновременно с подачей кода операции на вход 27 устройства подается сигнал пуска. Данный сигнал через элемент ИЛИ 22 устанавливает триггер 13 запуска в единичное состояние и разрешает тем самым формирование имульсов синхронизации работы устройства с выходов генератора тактовых импульсов (фиг. 6).

Так как на выходе схемы 10 сравнения имеется сигнал логического нуля, то этот сигнал разрешает прохождение кода операции со входа 31 устройства через коммутатор 8 микрокоманд (фиг. 1) на информационный вход буферного запоминающего блока 5. На выходе элемента ИЛИ 24 име ется сигнал логической единицы, который разрешает прохождение тактового импульса с выхода генератора 15.1 на управляющий вход буферного запоминающего блока 5 (фиг. 6). Тактовый импульс через элемент ИЛИ 40 (фиг. 2) поступает на синх5 ронизирующие входы регистров 37.1-36. К. Регистры 36.1-36.К находятся в нулевом состоянии и поэтому на выходе элементов И 39.1-39.К присутствуют сигналы логической единицы. Эти сигналы образуют управляющий код, который определяет тот ре0 гистр, в который необходимо записать код операции (адресную микрокоманду, определяющую номер выполняемой микропрограммы). Единичный управляющий код определяет для записи выходной (первый) регистр

5 36.1. Поэтому информация с информационного входа буферного запоминающего блока 5 через коммутатор 37.1 по тактовому импульсу заносится в регистр 36.1. Второй тактовый импульс с выхода генератора 15.2 поступает на синхронизирующий вход регист0 ра 2 адреса, и информация с регистра 36.1 буферного запоминающего блока 5 (фиг. 2) через коммутатор 6 адреса за- носится в регистр 2 (фиг. 1). Из блока 1 памяти микропрограмм будет считана микрокоманда, которая по очередному

5 тактовому импульсу с выхода . генератора 15.3 заносится в регистр 3 микрокоманд. Формат считанной микрокоманды представлен на фиг. 4. Операционная часть микрокоманды с поля 3.4 регистра 3 поступает на выход 33 устройства для управле ния операционным блоком, например, арифметико-логическим устройством.

Поля 3.1, 3.2 и 3.3 регистра 3 микрокоманд формируют адрес очередной микрокоманды с использованием мультиплексое ра 12 логических условий. Последний предназначен для формирования значения модифицируемого разряда адреса очередной микрокоманды и реализует логическую функцию вида

У xia + X2Zi + X3Z2ir..-fXA. iZb

0 где у I - выходной сигнал мультиплексора 12

логических условий;

Х| - конъюкция d, аг.-.а..., соответствующая комбинации с выхода 3.1 кода логических условий, разрешающей прохождение модифицируемого

5адресного разряда а без изменений;

Х2 aiaz...a(; Хз Siazaa.-ab Х4 a aia:3...ai - конъюкции, соответствующие кодам, определяющим прохождение на выход мультинлексора 12 одного из сигналов логических условий Zi, 7.2,..., ik со входа 32 логических условий устройства,с

в процессе вынолнения микропрограммы со входа 31 кода операции через коммутатор 8 микрокоманд в регистры, 36.1-36.К могут заноситься но тактовому импульсу с выхода 15.1 генератора 14 коды номеров очередных микропрограмм (коды операции). Ю

По тактовому импульсу с выхода 15.2 .генератора 14 происходит занесение сформированного адреса очередной микрокоманды в регистр 2 и обращение к блоку 1 памяти микропрограмм. По тактовому импульсу с выхода 15.3 генератора 14 происходит занесение считанной из блока 1 памяти информации в регистр 3 микрокоманд.

Одновременно с выдачей последней микгпй - код (номер) микропрограммы, которую должно выполнить Шпр-е микропрограммное устройство управления;

Ф - знак конкатенации (сцепления).

Одновременно с кодом М передачи управления с выхода поля 3.5 регистра 3 микрокоманд выдается метка, определяющая признак передачи микрокоманды управления аналогичному устройству. Эта метка поступает на управляющий вход выходного коммутатора 7 и разрешает тем самым прохождение микрокоманды передачи управления с поля 3.4 регистра 3 микрокоманд на выход 34 устройства для обработки аналогичным устройством. Кроме того, метка- признак передачи (М„ 1) управления поступает на управляющий вход блока элементов И 21 и запрещает тем самым прохождение кода на выход 33 устройства. Метка-признак передачи управления через

рокоманды выполняемой микропрограммы в 20 элемент ИЛИ 25 поступает на элемент И 19 поле 3.6 регистра 3 микрокоманд заносит-(фиг. 6) и разрешает прохождение через

ся метка-признак окончания команды. Эта метка, во-первых, поступает на вход коммутатора 6 адреса и разрешает прохождение через него информации из буферного запоминающего блока 5. Во-вторых, метка конца команды устанавливает триггер 41 буферного запоминающего блока 5 (фиг. 2) в единичное состояние, разрешающее тем самым сдвиг информации в регистрах 36.1 - 36.К путем коммутации выходов последующих регистров с информационными входами предыдущих регистров через соответствующие коммутаторы 37.1-37.К. В-третьих, метка-признак конца команды поля 3.6 регистра 3 микрокоманд формирует на выходе одно- вибратора 26 импульс. Этот импульс через элемент ИЛИ 40 буферного запоминающего блока 11 (фиг. 2) поступает на синхронизирующие входы регистров 36.1-36.К и производит сдвиг информации. После сдвига информации в регистрах 36.1-36.К бунего тактового импульса с выхода генератора 15.5. Тактовый импульс вместе с кодом М передачи управления выдается на выход 34 устройства. Далее микропрограмм- 25 ное устройство управления или выдает очередную микрокоманду (код) передачи управления, или обрабатывает «собственные микрокоманды, аналогично рассмотренному.

Работа устройства в режиме приема и анализа микрокоманд управления.

Микрокоманда передачи управления М от аналогичного устройства поступает на вход 30 устройства. Одновременно с этим кодом со входа 30 устройства поступает также тактовый импульс. Данный импульс поступает на синхронизирующий вход регистра 4 прие30

35

ма и производит в него запись информации. Если устройство не производило обработку некоторой микропрограммы, то тактовый импульс через элемент ИЛИ 22 установит триггер 13 запуска в единичное сосферного запоминающего блока 5 на выходе 40 тояние и разрешит тем самым формироваэлемента 42 задержки формируется импульс, устанавливающий триггер 41 управления в нулевое состояние (фиг. 6). Далее устройство функционирует аналогично рассмотренному.

Работа устройства в режиме выдачи микрокоманд управления осуществляется следующим образом.

В процессе обработки «собственных микрокоманд устройство может выдавать микрокоманды управления аналогичным устройствам, образующим кольцевую мультимикро- программную систему. Формат микрокоманды передачи управления представлен на фиг. 5. В этом случае с поля 3.4 регистра 3 микрокоманд выдается микрокоманда

М т„р ф т,

где гппр - код (номер) приемника управляющей информации;

ние импульсов с выхода генератора 14.

Код, занесенный в регистр 4 приема, состоит из двух частей: кода-номера устройства приемника информации и кода-номера микропрограммы, которую необходимо 45 выполнить mk- Код номера приемника информации с поля регистра 4 приема поступает на вход схемы 10 сравнения, где происходит сравнение с кодом номера данного устройства, поступающего с выхода генератора 9 констант.

Если поступившие на схему 10 сравнения коды не равны, то на выходе схемы будет сигнал логического нуля. Нулевой сигнал с выхода 3.5 регистра 3 поступает на вход элемента И 17 и разрешает прохождение через него тактового импульса с выхода 15.5 генератора 14 для организации сдвига информации в блоке 11 регистров. Сигнал логического нуля на выходе схе50

гпй - код (номер) микропрограммы, которую должно выполнить Шпр-е микропрограммное устройство управления;

Ф - знак конкатенации (сцепления).

Одновременно с кодом М передачи управления с выхода поля 3.5 регистра 3 микрокоманд выдается метка, определяющая признак передачи микрокоманды управления аналогичному устройству. Эта метка поступает на управляющий вход выходного коммутатора 7 и разрешает тем самым прохождение микрокоманды передачи управления с поля 3.4 регистра 3 микрокоманд на выход 34 устройства для обработки аналогичным устройством. Кроме того, метка- признак передачи (М„ 1) управления поступает на управляющий вход блока элементов И 21 и запрещает тем самым прохождение кода на выход 33 устройства. Метка-признак передачи управления через

0 элемент ИЛИ 25 поступает на элемент И 19 (фиг. 6) и разрешает прохождение через

него тактового импульса с выхода генератора 15.5. Тактовый импульс вместе с кодом М передачи управления выдается на выход 34 устройства. Далее микропрограмм- 5 ное устройство управления или выдает очередную микрокоманду (код) передачи управления, или обрабатывает «собственные микрокоманды, аналогично рассмотренному.

Работа устройства в режиме приема и анализа микрокоманд управления.

Микрокоманда передачи управления М от аналогичного устройства поступает на вход 30 устройства. Одновременно с этим кодом со входа 30 устройства поступает также тактовый импульс. Данный импульс поступает на синхронизирующий вход регистра 4 прие0

5

ма и производит в него запись информации. Если устройство не производило обработку некоторой микропрограммы, то тактовый импульс через элемент ИЛИ 22 установит триггер 13 запуска в единичное сос0 тояние и разрешит тем самым формирование импульсов с выхода генератора 14.

Код, занесенный в регистр 4 приема, состоит из двух частей: кода-номера устройства приемника информации и кода-номера микропрограммы, которую необходимо 5 выполнить mk- Код номера приемника информации с поля регистра 4 приема поступает на вход схемы 10 сравнения, где происходит сравнение с кодом номера данного устройства, поступающего с выхода генератора 9 констант.

Если поступившие на схему 10 сравнения коды не равны, то на выходе схемы будет сигнал логического нуля. Нулевой сигнал с выхода 3.5 регистра 3 поступает на вход элемента И 17 и разрешает прохождение через него тактового импульса с выхода 15.5 генератора 14 для организации сдвига информации в блоке 11 регистров. Сигнал логического нуля на выходе схе0

мы 10 сравнения идентифицирует то обстоятельство, что постунившая в устройство информация должна быть передана транзитом другому устройству управления. По тактовому импульсу с выхода генератора 15.4 информация с выхода регистра 4 приема через блок элементов И 20 будет занесена в блок 11 регистров (фиг. 8). По тактовому импульсу с выхода 15.5 генератора 14 информация с выхода блока 11 регистров через выходной коммутатор 7 поступает вместе с тактовым импульсом на выход 34 устройства.

Если код номера устройства, которому предназначена управляющая информация, совпадает с кодом номера данного устройства, то на выходе схемы 10 сравнения появляется сигнал логической единицы. Этот сигнал поступает на выход 35 устройства для организации работы мультимикропрог- раммной системы, например, для учета работы отдельных устройств, диспетчеризации заявок на обслуживание запросов между устройствами центральным процессором. Этот же сигнал запрещает запись информации через блок элементов И 20 в блок 11 регистров.

Сигнал логической единицы с выхода схемы 10 сравнения поступает на управляющий вход коммутатора 8 и разрещает прохождение через него информации о коде т/г микропрограммы с поля регистра 4 приема на информационный вход буферного запоминающего блока 5. По тактовому импульсу с выхода 15.1 генератора 14, поступающему через элемент И 18 на управляющий вход буферного запоминающего блока 5, информация заноситсяв соответствующий регистр 36.i (i 1, К) (фиг. 2) в зависимости от длины существующей очереди. Далее устройство функционирует аналогично рассмотренному.

Окончание процесса функционирования устройства может быть осуществлено по сигналу от центрального процессора, поступающему на вход 28 устройства, или по метке конца работы, выдаваемой в последней микрокоманде множества микропрограммы М с поля 3.7 регистра 3 микрокоманд. Сигнал признака конца работы устройства через элемент ИЛИ 23 поступает на нулевой вход триггера 13 запуска и обнуляет его. На этом работа микропрограммного устройства управления заканчивается и устройство готово к приему очередного кода микропрограммы от центрального процессора со входа 31 устройства или от соседнего аналогичного устройства управления со входа 30 устройства.

Формула изобретения

1. Микропрограммное устройство для управления обменом управляющей информации в распределенной системе, содержащее блок.памяти микропрограмм, коммутатор адреса, регистр адреса, регистр .микрокоманд, буферный запоминающий блок, коммутатор микрокоманд, мультиплексор логических условий, триггер запуска, генератор тактовых импульсов, первый и второй блоки элементов И, первый, второй, третий и четвертый элементы ИЛИ, первый, второй, третий элементы И, одновибратор, причем выход коммутатора адреса соединен с информационQ ным входом регистра адреса, выход которого соединен с адресным входом блока памяти микропрограмм, выход блока памяти микропрограмм соединен с информационным входом регистра микрокоманд, выход поля кода, логических условий ре5 гистра микрокоманд соединен с управляющим входом мультиплексора логических условий, выход модифицируемого разряда адреса регистра микрокоманд соединен с первым информационным входом мультиплексора логических условий, выхйд поля

0 (п-1) немодифицируемых разрядов адреса регистра микрокоманд, где п - разрядность адреса, соединен с первого по (п-1)-й разрядами первого информационного входа коммутатора адреса, выход мультиплексора

5 логических условий соединен с п-ым разрядом первого информационного входа коммутатора адреса, прямой выход триггера запуска соединен с входом пуска генератора тактовых импульсов, вход логических условий устройства соединен с вторым информацион0 ным входом мультиплексора логических условий, вход кода операции устройства соединен с первым информационным входом коммутатора микрокоманд, вход запуска устройства соединен с первым входом первого элемента ИЛИ, выход которого соеди5 нен с входом установки в единицу триггера запуска, первый и второй выходы генератора тактовых импульсов соединены соответственно с синхронизирующими входами регистра адреса и регистра микрокоманд, выход признака конца команды регистра микрокоманд соединен с входом одновибратора и управляющим входом коммутатора адреса, вход сброса устройства соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в «О

5 триггера запуска, выход признака конца работы регистра микрокоманд соединен с вторым входом второго элемента ИЛИ и первым входом первого блока элементов И, выходы операционного поля регистра микрокоманд соединены с вторым входом пер0 вого блока элементов И, выход которого соединен с выходом кода микроопераций устройства, отличающееся тем, что, с целью расщирения области применения устройства за счет реализации транзитной передачи микропрограмм управления, устройство содер5 жит шифратор констант, регистр приема, блок регистров, схему сравнения, элемент задержки, выходной коммутатор, причем вход настройки устройства соединен с вхо0

дом шифратора констант, выход которого соединен с первым входом схемы сравнения, выход схемы сравнения соединен с первым входом второго блока элементов И, управляющим входом коммутатора микрокоманд и выходом признака управления распределенной системой устройства, вход кода управления распределенной системой устройства соединен с информационным входом регистра приема, выход кода номера внешнего устройства регистра приема соединен С вторым входом схемы сравнения, выход кода операции регистра приема соединен е: вторым входом второго блока элементов И И вторым информационным входом коммутатора микрокоманд, выход второго блока элементов И соединен с информационным входом блока регистров, третий выход генератора тактовых импульсов соединен с первым входом первого элемента И и входом разрешения сдвига блока регистров, выход первого элемента И соединен с входом синхронизации буферного запоминающего блока, выход которого соединен с вторым информационным входом коммутатора адреса, четвертый выход генератора тактовых импульсов соединен с входом элемента задержки и с первым входом синхронизации блока регистров, выход коммутатора микрокоманд соединен с информационным входом буферного запоминающего блока и входом третьего элемента ИЛИ, пятый выход генератора тактовых импульсов соединен с первыми входами второго и третьего элементов И и входом запрета сдвига блока регистров, выход второго элемента И соединен с вторым входом синхронизации блока регистров, выход операционного поля регистра микрокоманд соединен с первым информационным входом выходного коммутатора, выход которого соединен с выходом кода управления распределенной системой устройства, выход признака передачи управления регистра микрокоманд соединен с управляющим входом выходного коммутатора, инверсным входом первого блока элементов И, первым входом четвертого элемента ИЛИ, инверсным входом второго элемента И и входом кода сдвига блока регистров, выход которого соединен с вторым входом четвертого элемента ИЛИ, и вторым информационным входом выходного коммутатора, выход третьего элемента И подключен к выходу кода управления распределенной системой устройства, выход признака конца команды регистра микрокоманд соединен с входом разрешения записи буферного запоминающего блока, выход одновибратора соединен с входом управления сдвигом буферного запоминающего блока, вход синхронизации устройства соединен с вторым входом первого элемента ИЛИ и с синхронизирующим входом регистра приема, вход установки в «О которого соединен с выходом элемента задержки, выход третьего элемента ИЛИ соединен с вторым входом первого элемента И.

2.Устройство по п. I, отличающееся тем, .что буферный запоминающий блок содержит с первого по К-й регстры, где К - глубина очереди на обслуживание запросов устройством, с первого по (К-1)-й коммутаторы, дешифратор, с первого по К-й элементы И, элемент ИЛИ, триггер, элемент

,. задержки, группу элементов ИЛИ, причем информационный вход блока соединен с информационным входом К-го регистра и первыми информационными входами с первого по (К-1)-й коммутаторов, выходы которых соединены соответственно с информа5 ционными входами с первого по (К-1)-й регистров, вход синхронизации буферного запоминающего блока соединен с первым входом элемента ИЛИ, выход которого соединен с синхронизирующими входами с первого по К-й регистров, вход управления

0 сдвигом блока соединен с вторым входом элемента ИЛИ и входом элемента задержки, выход которого соединен с входом установки в «О триггера, вход разрешения записи блока соединен с входом установ5 ки в «1 триггера, инверсный выход которого соединен с первыми управляющими входами с первого по (К-1)-й коммутаторов, прямой выход триггера соединен с вторыми управляющими входами с первого по (К-1)-й коммутаторов и первыми входа0 ми элементов ИЛИ группы, выходы которых соединены соответственно с входами разрешения записи с первого по К-й регистров, инверсные выходы с первого по (К-1) регистров соединены с входами с первого по К-й элементов И соответственно, выходы ко5 торых соединены соответственно с первого.luj К-й входами дешифратора, с первого по К-й выходы дешифратора соединены соответственно с вторыми входами группы элементов ИЛИ, прямые выходы с второго по К-й регистров соединены соответственно с

0 вторыми информационными входами с первого по (К-1)-й коммутаторов, прямой выход первого регистра соединен с выходом блока.

3.Устройство по п. 1, отличающееся тем, , что блок регистров содержит с первого по

N-й регистры, где N - длина очереди хранения транзитных запросов устройства, триггеры, дешифратор, первую и вторую группы элементов И, группу элементов ИЛИ, с первого по (N - 1)-й коммутаторы, причем инQ формационный вход блока подключен к информационному входу N-ro регистра и к первым информационным входам с первого по N-й коммутаторов, выходы которых соединены с информационными входами с первого по N-й регистров соответственно, вхо5 ды разрещения и запрета сдвига блока соединены соответственно с входом установки в «О и «1 триггера, инверсный выход которого соединен со стробирующим вхолом

дешифратора, прямые выходы с второго по N-й регистров соединены соответственно с вторыми информационными входами с первого по (N-1)-й коммутаторов, инверсные выходы с первого по N-й регистров соединены с входами одноименных элементов И первой группы соответственно, выходы которых соединены с информационными входами дешифратора, с первого по N-й выходы дешифратора соединены соответственно с первыми входами элементов И второй группы, выходы которых соединены с первыми входами элементов ИЛИ группы

0

соответственно, первый вход синхронизации блока соединен с вторыми входами элементов И второй группы, второй вход синхронизации блока соединен с вторыми -входами элементов ИЛИ группы, вход кода сдвига блока соединен с первыми управляющими входами с первого по (N-1)-й коммутаторов, с первого по (N-1)-й выходы дешифратора соединены соответственно со вторыми и третьими управляющими входами с первого по (N-1)-й коммутаторов, прямой выход первого регистра соединен с выходом блока.

.2

fPu2. 49u.2. 5

fPilZ.

Л

П(I

HuHonbHifiLi a&ijec МП упг другого

IX

X

/I

Выдача начального адреса другому

Транзитные adijecct.

7

V

а

л(1

Y cdSuz uHcpypfiynuu

yti

л

,Выдача пербого транзитного адреса

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Многоканальное устройство для обмена управляющей информацией в вычислительной системе | 1988 |

|

SU1566362A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256025A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих и вычислительных систем высокой производительности, в частности при организации процедур управления в систолических структурах. Цель изобретения - расширение области применения устройства за счет реализации транзитной передачи микрокоманд управления. Микропрограммное устройство для управления обменом управляющей информации в распределенной системе содержит блок Iпамяти микропрограмм, регистры адреса 2, микрокоманд 3 и приема 4, буферный запоминающий блок 5, коммутаторы адреса 6, выходной 7 и микрокоманд 8, генератор 9 констант, схему сравнения 10, блок 11 регистров, мультиплексор 12 логических условий, триггер 13 запуска, генератор 14 тактовых импульсов, третий 15.1, первый 15.2, второй 15,3, четвертый 15.4 и пятый 15.5 выходы генератора 14 тактовых импульсов, элемент 16 задержки, элементы И 17, 18 и 19, блоки 20 и 21 элементов И, первый 22, второй 23, третий 24, четвертый 25 элементы ИЛИ, одновибратор 26. Новыми в устройстве являются шифратор 9 констант, регистр 4 приема, схема 10 сравнения, блок IIрегистров, элемент 16 задержки и выходной коммутатор 7, что позволяет достигнуть цели изобретения. 2 з.п. ф-лы, 8 ил. (Л со to ел

| УСТРОЙСТВО для МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 0 |

|

SU217066A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропрограммного управления при к-значном кодировании | 1972 |

|

SU474806A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-23—Публикация

1986-02-05—Подача