(5) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство микропрограммного управления | 1981 |

|

SU985788A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматических системах с программным управлением в цифровых вычислительных машинах.

Известно микропрограммное устройство управления, содержащее счетчик, два дешифратора адреса, блок памяти микропрограмм, блок памяти микроопераций, регистр микрокоманд, счетчик тактов и дешифратор микроопераций Il(.

Однако указанное устройство достаточно сложно при технической реализации..

Наиболее близким по технической сущности и достигаемому результату к из.обретению является устройство микропрограммного управления, содержащее два запоминающих устройства, дешифратор, логические элементы ИЛИ, регистр адреса, элементы И передачи адреса, буферный регистр, элемент задержки, генератор тактовых импуль,

СОВ, элементы И изменения адреса и регистр команд 12).

Недостатком известного устройства является невысокая надежность и его сложность.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в устройство микропрограммного управления, содержащее два блоtoка памяти, блок элементов ИЛИ, дешифратор, регистр адреса, две группы элементов И, буферный регистр, генератор импульсов, элемент задержки и регистр команд причем группа выходов

15дешифратора соединена с группой входов первого блока памяти и с. группой входов блока элемента ИЛИ, группа выходов которого соединена с группой входов второго блока памяти, группа

М выходов которого является группой информационных выходов устройства, вход дешифратора соединен с выходом регистра адреса, группа информационных входов которого соединена с группой выходов элементов И первой группы, первые входы которых соединены соответственно с выходами группы- выходов буферного регистра, тактовый вход которого соединен с управляющим входом дешифратора и через элемент задержки с выходом генератора импульсов, первая группа информационных входов буферного регистра соединена с группой выходов элементов И второй группы, первые и вторые входы которых соединены соответственно с первым управляющим выходом первого блок памяти и с выходами поля кодов операций регистра команд, вторая группа информационных входов буферного регистра является группой входов начального адреса устройства, третья группа информационных входов буферного регистра соединена с группой выходов первого блока памяти, введены элемен ИЛИ, элемент НЕ и два элемента И, причем группа информационных выходов и первый и второй управляющие выходы первого блока памяти соединены соотаетствеино с входами элемента ИЛИ, . выход которого соединен с первым вхо дом первого элемента И и через элемент НЕ с первым входом второго элемента. И, вторые входы первого и второго элементов И соединены с выходом генератора импу7;1ьсов, выход первого элемента И соединен с вторыми входами элементов И первой группы, выход второго элемента И соединен с управляющим входом регистра адреса.

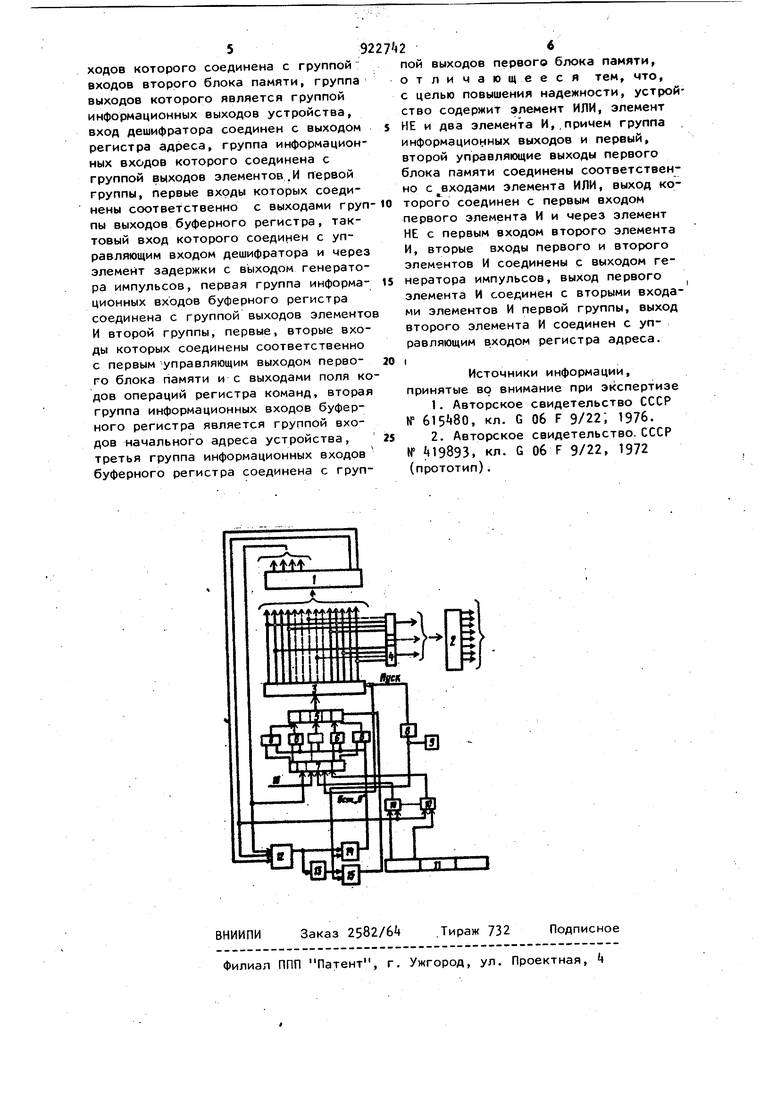

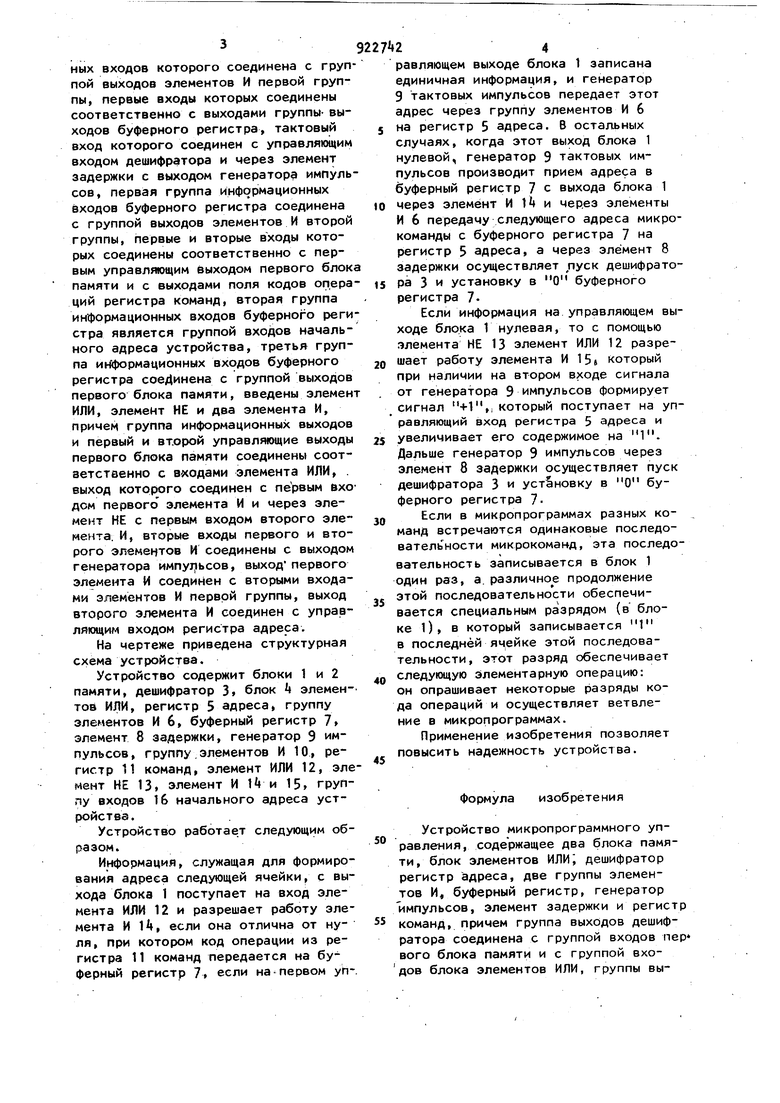

На чертеже приведена структурная схема устройства.

Устройство содержит блоки 1 и 2 памяти, дешифратор 3, блок k элементой ИЛИ, регистр 5 адреса, группу элементов И 6, буферный регистр 7, элемент 8 задержки, генератор 9 импульсов, группу .элементов И 10, регистр 11 команд, элемент ИЛИ 12, элемент НЕ 13, элемент И И и 15, группу входов 16 начального адреса устройства.

Устройство работае.т следующим образом.

Информация, служащая для формирования адреса следующей ячейки, с выхода блока 1 поступает на вход элемента ИЛИ 12 и разрешает работу элемента И 14, если она отлична от нуля, при котором код операции из регистра 11 команд передается на буферный регистр 7, если на первом уп-.

равляющем выходе блока 1 записана единичная информация, и генератор 9 тактовых импульсов передает этот адрес через группу элементов И 6 5 на регистр 5 адреса. В остальных случаях, когда этот выход блока 1 нулевой, генератор 9 тактовых импульсов производит прием адреса в буферный регистр 7 с выхода блока 1 0 через элемент И 1 и через элементы И 6 передачу следующего адреса микрокоманды с буферного регистра 7 на регистр 5 адреса, а через элемент 8 задержки осуществляет пуск дешифратое ра 3 и установку в О буферного регистра 7.

Если информация на управляющем выходе блока 1 нулевая, то с помощью элемента НЕ 13 элемент ИЛИ 12 разрешает работу элемента И 15 который при наличии на втором входе сигнала от генератора 9 импульсов формирует сигнал +1,i который поступает на управляющий вход регистра 5 адреса и 5 увеличивает его содержимое на 1. Дальше генератор 9 импульсов через элемент 8 задержки осуществляет пуск дешифратора 3 и уст&новку в О буферного регистра 7Если в микропрограммах разных команд встречаются одинаковые последовательности микрокоманд, эта последовательность записывается в блок 1 один раз, а. различное продолжение этой последовательности обеспечивается специальным разрядом (в блоке 1), в который записывается 1 в последней ячейке этой последовательности, этот разряд обеспечивает следующую элементарную операцию: он опрашивает некоторые разряды кода операций и осуществляет ветвление в микропрограммах.

Применение изобретения позволяет повысить надежность устройства.

Формула изобретения

Устройство микропрограммного управления, содержащее два блока памяти, блок элементов ИЛИ) дешифратор регистр адреса, две группы элементов И, буферный регистр, генератор 11мпульсов, элемент задержки и регистр команд, причем группа выходов дешифратора соединена с группой входов пер вого блока памяти и с группой входов блока элементов ИЛИ, группы вы

Авторы

Даты

1982-04-23—Публикация

1980-06-09—Подача