(54) АДАПТИВНОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство микропрограммного управления | 1984 |

|

SU1290317A1 |

| Устройство микропрограммного управления | 1981 |

|

SU960815A1 |

| Микропрограммное устройство управления | 1978 |

|

SU763898A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство микропрограммного управления | 1980 |

|

SU960814A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Микропрограммное устройство управления | 1980 |

|

SU959080A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве управляющего устройства ЭВМ, применяемых для управления сложными системами.

Известно микропрограммное устройство управления, содержащее два запоминающих блока, регистры, логические элементы И и НЕ, элементы задержки, счет чики, дешифраторы и генератор тактовых импульсов tl.

Недостатком этого устройства является низкое йгстродействие.

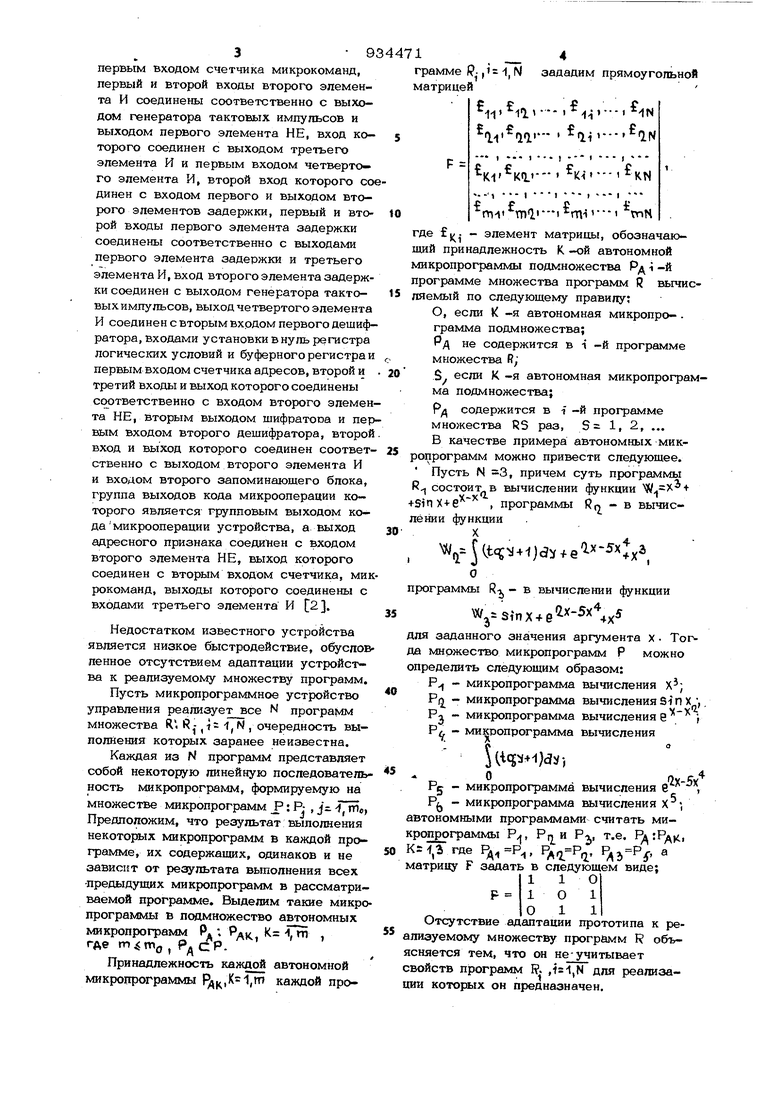

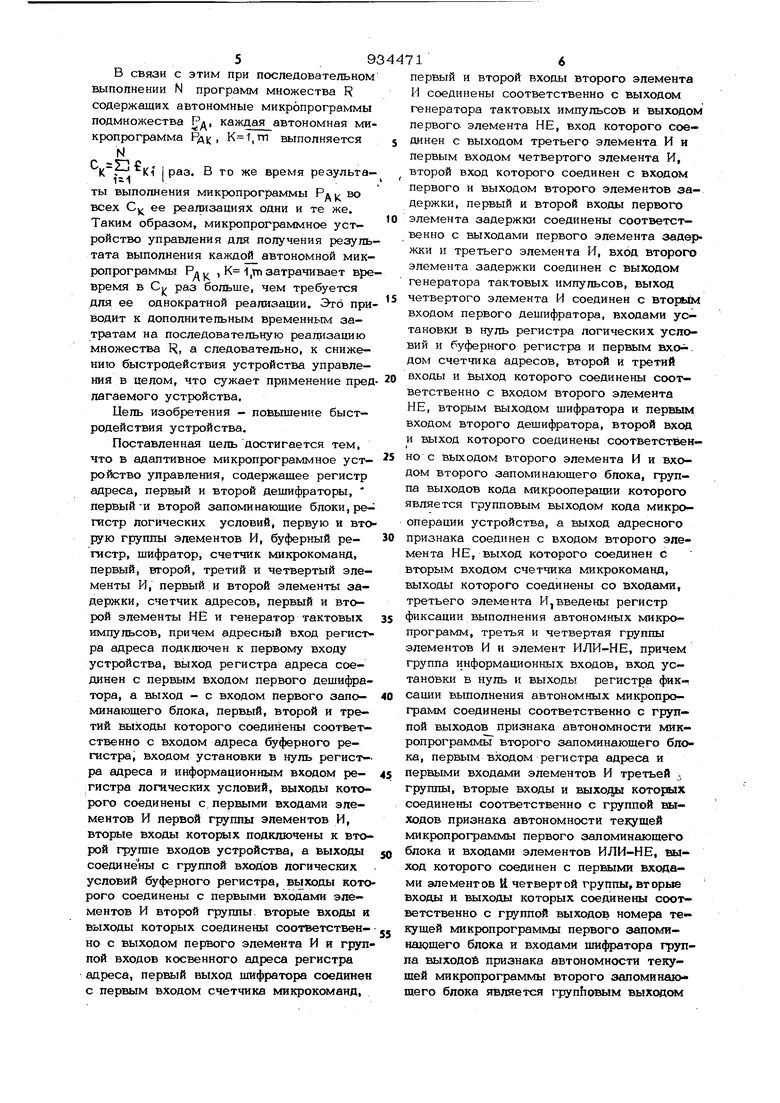

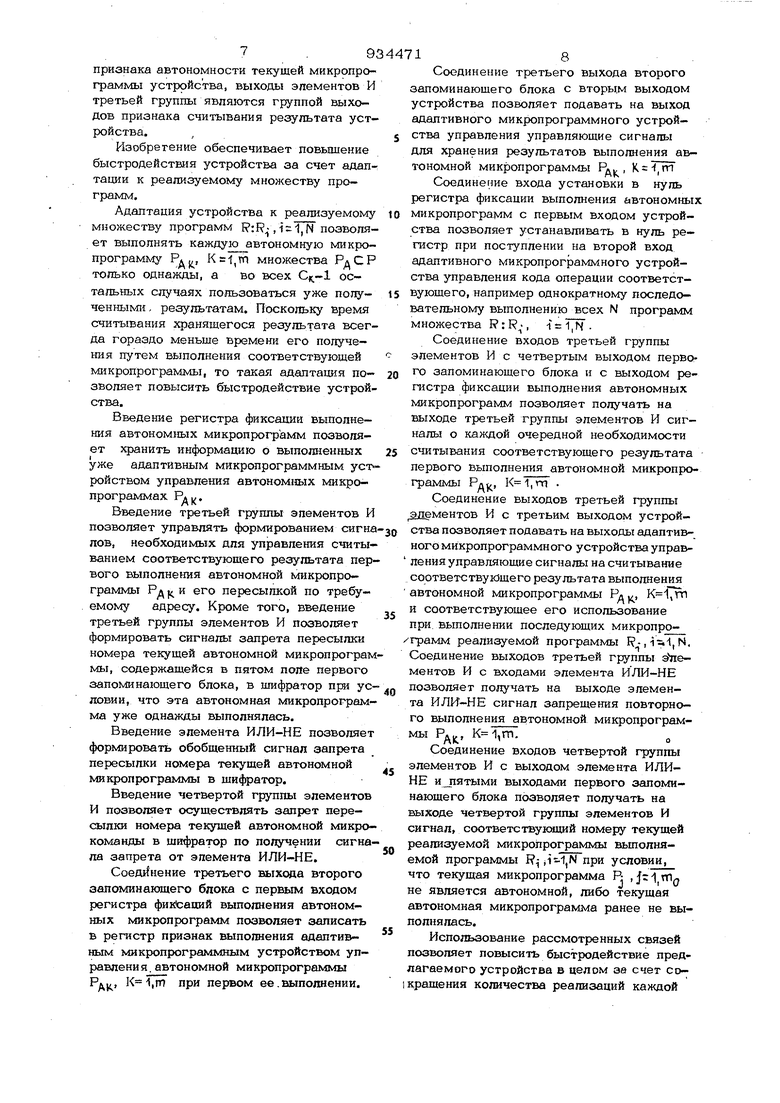

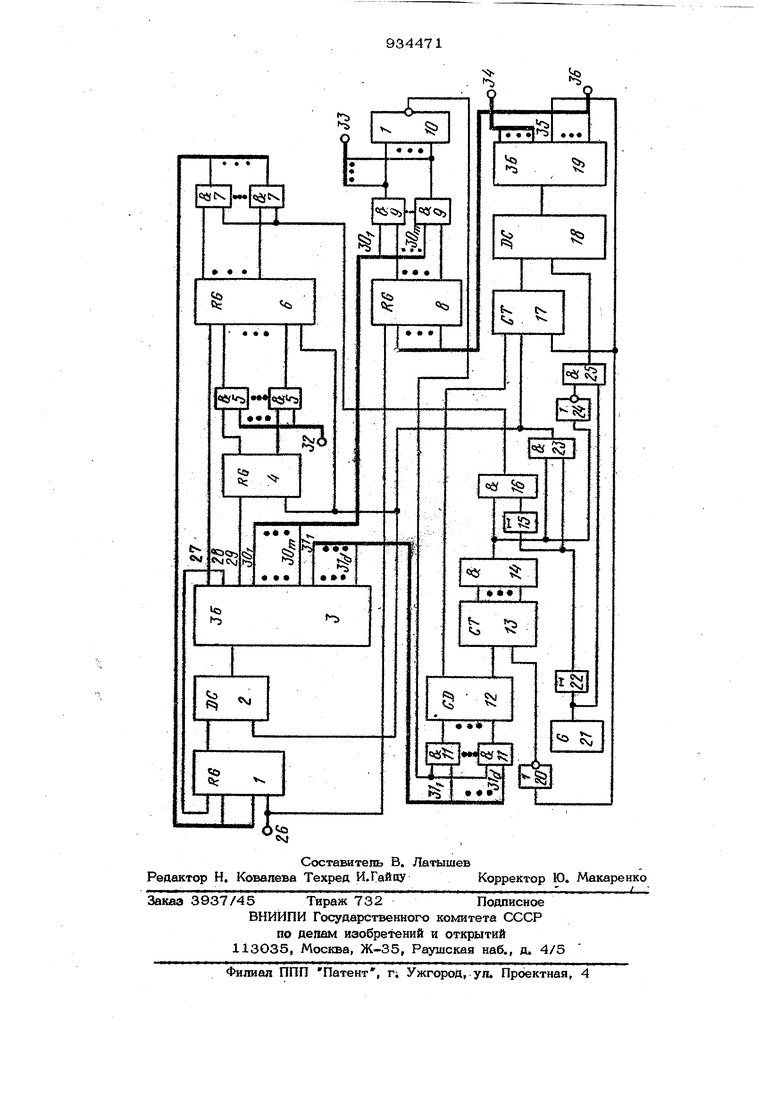

Наиболее близким к предлагаемому является микропрограммное устройство управления. Это устройство содержит регистр адреса, первый и второй дешифраторы, первый и второй запоминающие блоки, регистр логических условий, первую и вторую группы элементов И, бу юрный регистр, щифратор, счетчик микрокоманд, первый, второй, третий и четвертый эпеменоы И, первый и второй элементы задержки, счетчик адресов, первый и второй элементы НЕ и генератор тактовых импульсов, причем адресный вход pejгистра адреса является первым входом устройства, выход регистра адреса соединен с первым входом первого дешифратора, а выхсю - с входом первого запоминающего блока, первый, второй и трю- тий выходы которого соединены соответственно с входом адреса буферного регистра, входом установки в нуль регистра адреса и информацисжным входом регистра логических условий, выходы которого соединены с первыми входами элементов И первой группы, вторые входы которых подключены к второй группе входов устройства, а выходы соединены с группой входов логических условий буферного регистра, выходы которого соеди. нены с. первыми входами элементов И второй группы, вторые входы и выходы котордх соединены соответственно с выходом элементе И и группой входов косвенного адреса регистра адре« са, первый выход 1Ш14 атора соединен с первым входом счетчика микрокоманд, первый и второй входы второго элемента И соединены соответственно с выходом генератора тактовых импульсов и выходом первого элемента НЕ, вход ко- торого соединен с выходом третьего элемента И и первым входом четвертого элемента И, второй вход которого со динен с входом первого и выходом второго элементов задержки, первый и второй входы первого элемента задержки соединены соответственно с выходами первого элемента задержки и третьего элемента И, вход второго элемента задержки соединен с выходом генератора тактовых импульсов, выход четвертого элемента И соединен с вторым входом первого дешифратора, входами установки в нуль регистра логических условий и буферного регистра и первым входом счетчика адресов, второй и третий входы и выход которого соединены соответственно с входом второго элемен та НЕ, вторым выходом шифратооа и пер вым входом второго дешифратора, второй вход и выход которого соединен соответ ственно с выходом второго элемента И и входом второго запоминающего блока, группа выходов кода микрооперации которого является групповым выходом кода микрооперации устройства, а выход адресного признака соединен с входом второго элемента НЕ, выход которого соединен с вторым входом счетчика, мик рокоманд, выходы которого соединены с входами третьего элемента И 2. Недостатком известного устройства является низкое быстродействие, обуслов ленное отсутствием адаптации устройства к реализуемому множеству программ. Пусть микропрограммное устройство управления реализует все N программ множества R- j, t 1, N , очередность выполнения которых заранее неизвестна. Каждая из N программ представляет собой некоторую линейную последователь ность микропрограмм, формируемую на множестве микропрограмм Р: Р; , j -1, гПс, Предположим, что результат выполнения некоторых микропрограмм в каждой программе, их содержащих, одинаков и не зависит от реа1ультата вьшолнения всех предыдущих микропрограмм в рассматриваемой программе. Выделим такие микро программы в подмножество автономных микропрограмм Р ; Рдк., 1 -i/rn , где , РдСР. Принадлежность каждой автономной микропрограммы ,,т каждой программе 1. iiz-I N зададим прямоугольной матрицей где 1. - элемент матрицы, обозначающий принадлежность К -ой автономной микропрограммы подмножества Рд i -и программе множества программ R вычисляемый по следующему правилу; О, если К -я автономная микропро- . грамма подмножества; Рд не содержится в i -и программе множества R; S если К -я автономная микропрограмма подмножества; Рд содержится в i -и программе множества RS раз, S 1, 2, ... В качестве примера автономных микропрограмм можно привести следующее. Пусть N 3, причем суть программы R-) состоит в вычислении функции +Sin X-t-e , программы RQ - в вычислении функции X , ei) программы Rij - в вычислении функции Wj si-nx + для заданного значения аргумента х. Тог да мнржество микропрограмм Р можно определить следующим образом: Р - микропрограмма вычисления х; PIJ - микропрограмма вычисления Si П X,, Рл - микропрограмма вычисления , РЛ - микропрограмма вычисления , о7х-5х Pj - микропрограмма вычисления 6 , Рл - микропрограмма вычисления X , автономными программами считать микропрограммы Р, Pj,, т.е. КМ,3 где Рд,Р,, , , а матрицу F задать в следующем виде; 1 10 101 01 1 Отсутствие адаптации прототипа к реализуемому множеству программ R объясняется тем, что он не-учитывает свойств программ R. ,bl,N для реализации которых он предназначен. 5.93 В связи с этим при последовательном выполнении N программ множества R содержащих автономные микропрограммы подмножества Рд, каждая автономная микропрограмма Рд,;, ,т выполняется N Г 5 С I раз. В то же время реаультаты выполнения микропрограммы Рд. во всех С) ее реализациях одни и те же. Таким образом, микропрограммное устройство управления для получения результата выполнения каждой автономной микропрограммы PUV , К 1,тт1 затрачивает вре- время в С., раз больше, чем требуется для ее однократной реализации. Это приводит к дополнительным временньп затратам на последовательную реализацию множества R, а следовательно, к снижению быстродействия устройства управлеНИИ в целом, что сужает применение предлагаемого устройства. Цель изобретения - повьпление быстродействия устройства. Поставленная цель достигается тем, что в адаптивное микропрограммное устpoifcTBO управления, содержащее регистр адреса, первый и второй дешифраторы, первыйИ второй запо шнающие блоки, регмстр логических условий, первую и вто рую группы элементов И, буферный регистр, шифратор, счетчик микрокоманд, первый, второй, третий и четвертый элементы И, первый и второй элементы задержки, счетчик адресов, первый и второй элементы НЕ и генератор тактовых импульсов, причем адресный вход регистра адреса подключен к первому входу устройства, выход регистра адреса соединен с первым входом первого дешифратора, а выход - с входом первого запоминаюшего блока, первый, второй и третий выходы которого соединены соответственно с входом адреса буферного регистра, входом установки в нуль регист- ра адреса и информационным входом регистра логических условий, выходы которого соединены с первыми входами элементов И первой группы элементов И, вторые входы которых подключены к второй группе входов устройства, а выходы соединёны с группой логических условий буферного регистра, выходы кото рого соединены с первыми входами з/ю- ментов И второй группы, вторые входы и выходы которых соединены соответственно с выходом первого элемента И и группой входов косвенного адреса регистра адреса, первый шифратора соединен с первым входом счетчика микрокоманд, 16 первый и второй входы второго элемента И соединены соответственно с выходом генератора тактовых импульсов и выходом первого элемента НЕ, вход которого соединен с выходом третьего элемента И и первым входом четвертого элемента И, второй вход которого соединен с входом первого и выходом второго элементов задержки, первый и второй входы первого элемента задержки соединены соответственно с выходами первого элемента задержки н третьего элемента И, вход второго элемента задержки соединен с выходом генератора тактовых импульсов, выход четвертого элемента И соединен с вторь Дешифратора, входами усгановш в нуль регистра логических успо буферного регистра и первым вхо. счетчика адресов, второй и третий входы и выход которого соединены соответственно с входом второго элемента вторым выходом шифратора и первым входом второго дешифратора, второй вход ,« которого соединены соответствен ° выходом второго элемента И и второго запоминающего блока, группа выходов кода NfflKpoonepamin которого является групповым выходом кода микрооперации устройства, а выход адресного признака соединен с входом второго эпемента НЕ, выход которого соединен С вторым входом счетчика микрокоманд, выходы которого соединены со входами, третьего элемента И,введены регистр фиксации выполнения автономных микропрограмм, третья и четвертая группы элементов И и элемент ИЛИ-НЕ, причем группа информационных входов, вход уетановки в нуль и выходы регистра фик- сации выполнения автономных микропрограмм соединены соответственно с группой выходов признака автономности микропрограммы второго запоминающего блока, первым входом регистра адреса и первыми входами элементов И третьей группы, вторые входы и выхофл которых соединены соответственно с группой выходов признака автономности текущей микропрограммы первого запоминающего блока и входами элементов ИЛИ-НЕ, выход которого соединен с первыми входами элементов U четвертой группы, вторые входы и выходы которых соединены соответственно с группой выходов номера текущей микропрограммы первого запоминавдщего блока и входами шифратора группа выходоб признака автономности текущей микропрограммы второго запоминающего блока является групЬовым выходом признака автономности текущей микропрограммы устройства, выходы элементов И третьей группы являются группой выходов признака считывания результата устройства., Изобретение обеспечивает повышение быстродействия устройства за счет адаптации к реализуемому множеству программ. Адаптация устройства к реализуемому множеству программ RrRi. позволяет выполнять каждую автономную микропpoгpaм iy Рд,, ,т множества РдСР только однажды, а во всех остальных случаях пользоваться уже полученными, результатам. Поскольку время считывания хранящегося результата всегда гораздо меньше времени его получения путем выполнения соответствующей микропрограммы, то такая адаптация позволяет повысить быстродействие устройства. Введение регистра фиксации выполнения автономных микропрограмм позволяет хранить информацию о выполненных уже адаптивным микропрограммным уст ройством управления автономных микропрограммах Рд(. Введение третьей группы элементов И позволяет управлять формиройанием сигна лов, необходимых для управления считыванием соответствующего результата пер вого выполнения автономной микропрограммы Рд«. и его пересылкой по требуемому адресу. Кроме того, введение третьей группы элементов И позволяет формировать сигналы запрета пересылки номера текущей автономной микропрограм мы, содержащейся в пятом поле первого запоминающего блока, в шифратор прт ус ловии, что эта автономная микропрограм ма уже однажды выполнялась. Введение элемента ИЛИ-НЕ позволяет формировать обобщенный сигнал запрета пересылки номера текущей автономной микропрограммы в щифратор. Введение четвертой группы элементов И позволяет осуществлять запрет пересылки номера текущей автономной микро команды в шифратор по получении сигна ла запрета от элемента ИЛИ-НЕ. Соединение третьего выхода второго запоминающего блока с первым входом регистра фикЬаоий выполнения автономных микропрограмм позволяет записать в регистр признак выполнения адаптивным микропрограммным устройством управления. автономной микропрограммы Рд, К ViT при первом ее. выполнении. Соединение третьего выхода второго апоминающего блока с вторы.м выходом устройства позволяет подавать на выход адаптивного микропрограммного устройства управления управляющие сигналы для хранения результатов выполнения автономной микропрограммы P«., , К Vrf Соединение входа установки в нуль регистра фиксации выполнения автономных микропрограмм с первым входом устройства позволяет устанавливать в нуль регастр при поступлении на второй вход адаптивного микропрограммного устройства управления кода операции соответствующего, например однократному последовательному выполнению всех N программ множества R: R , i 1|N . Соединение входов третьей группы элементов И с четвертым выходом первого запоминающего блока и с выходом рюгистра фиксации выполнения автономных микропрограмм позволяет получать на выходе третьей группы элементов И сигналы о каждой очередной необходимости считывания соответствующего результата первого выполнения автономной микропрограммы РЛ, К 1,гп . Соединение выходов третьей группы элементов И с третьим выходом устройства позволяет подавать на выходы адаптивного микропрограммного устройства управления управляющие сигналы на считывание соответствующего результата выполнения автономной микропрограммы Рдц, ,т и соответствующее его использование при выполнении последующих микропрограмм реализуемой программы ,N. Соединение выходов третьей группы эпементов И с входами элемента ИЛИ-НЕ позволяет получать на выходе элемента ИЛИ-НЕ сигнал запрещения повторного выполнения автономной микропрограммы Рд, ,т.о Соединение входов четвертой группы элементов И с выходом элемента ИЛИНЕ и J ятыми выходами первого запоминающего блока позволяет получать на выходе четвертой группы элементов И сигнал, соответствующий номеру текущей реализуемой микропрограммы вьшолняемой программы I -ii-1,N при условии, что текущая микропрограмма Р- , не является автономной, либо текущая автономная микропрограмма ранее не выполнялась. Использование рассмотренных связей позволяет повысить быстродействие предлагаемого устройства в целом за счет ct кращения количества реализаций каждой автономной микропрограммы Рд,/, ,m на (С,) раз. Повышение быстрюдействия устройств можно пояснить следующим образом. В ячейках второго запоминающего блока последовательно записаны микрокоманды b..,V:1|Cl состоящие из трех полей разрядностью П(3,т соответственно. В первом поле Ъ разрядностью Пр-бсхГлй считываемом по первому выходу второго запоминающего блока, задаются сигналы микроопераций. Во втором поле fcw (Содержащем один разряд и считываемом по второму выходу второго запоминающего блока, задается признак того, что данная микрокоманда byiV-1, SL является заключательной в какой-либо микропрограмме RJ , третьем пoлeЪ,,Q содержащем m разрядов и считываемом по третьему выходу второго запоминающего блока, задается признак того, что данная микрокоманда Ъу V 1 fi является конечной (заключительной) только в автономной микропрограмме Рр, ,01.При этом в каждом К-м разряде третьего поля Ъ ,(5 ,т записаны О либо 1 по сле дующему правилу: QJ если V -я микрокоманда не является конечной в К-й автономной микропрограмме Рд) 1, ее пи V -я микрокоманда является конечной в К -и автономной микропрограмме РдцТакое кодирование третьего поля Ь позволяет однозначно идентифицировать каждую выполненную устройством авто- номную микропрограмму . (,тп и сформулировать на этой основе управляющие сигналы для пересыпки полученного результата выполнения данной микропрограммы на хранение. Идентификация ыдполненной автономной микропрограммы ,т путем записи в К.й раз- ряд регистра фиксации вьтолнения автономных микропрограмм единицы происходит при считывании из второго запомина- юшего блока последней микропрограммы реализуемой автономной микропрограммы РАН J ii Аналогично третьему полю второго запоминающего блока Ъ проведено кодирование четвертого поля первого запоминающего блока с(п, ,ГП0. При этом с|р О, если номер текущей микрокоманды dg не соответствует К.-и вътанамаой микрО программе ,ар г 3,если номер текущей микрокоманды а в соответствует К-й автономной микропрограмме Рд). Поэтомупри необходимости повторного выполнения некоторой автономной микропрограммы РАК, K liTT в очередных программах F ,i VT при считывании микрокоманды 0р, четвертом выходе перового запоминающего блока появляется fg К-м разряде четвертого поля ей. Следовательно, на выходе К-го элемента И третьей группы элементов И появляется 1. Этот сигнал через элемент ИЛИ-НЕ и четвертую группу элементов И 3anpemaet подачу с пятого выхода первого запоминающего блока информации о номере те- кушей автономной микропрограммы Рдц на шифратор. В то же время этот же сигнал поступает на третий выход устройства для считывания хранящегося результата выполнения автономной микропрограммы Рд(с.и его пересылки в адрес того устройства, где он получится в результате повторного выполнения адаптивным микрюпрограммным устрЫ4ством управления автономной микропрограммы Рд,. Кроме того, так как счетчик микрокоманд остается в нуле, то импульс генератора тактовых импульсов через первый и второй элементы задержки, первый элемент И вторую группу элементов И передает косвенный номер следующей микрокоманды первого запоминающего блока, соответствующий очередной микропрограмме программы , Ti.1,N в регистр адреса. Поскольку время протекания описанных процессов меньше времени выполнения самой автономной микропрограммы, то тем самым достигается эффект выполнения быстрюдействия устройства в целом. Это позволяет расширить применение предлагаемого устройства. На чертеже представлена функциональная схема предлагаемого адаптивного микропрограммного устройства управ- . ления. Устройство содержит регистр 1 адреса, первый дешифратор 2, первый запоминающий блок, регистр 4 логических условий, первую группу элементов И 5, буферный регистр 6, вторую группу элементов И 7, регистр 8 фиксации выполнения автономных микрокоманд, третью группу элементов И 9, элемент ИЛИ-НЕ 1О, четвертую группу элементов И 11, игафратор 12, счетчик 13 микрок(анд, третий элемент И 14, первый элемент 15 задержки, первый элемент И 16, счетчик 1-7 адресов, второй дешифратор 18, второй запоминающей блок 19, второй элемент НЕ 2О, генератор 21 так1193товых импульсов, второй элемент 22 задержки, четвертый элемент И 23, первый элемент НЕ 24, второй элемент И 25, Символом 26 обозначен первый вход устройства - первый, второй, третий, четвертый и пятый выходы первого запоминающего блока соответственно, 32 - второй вход устройства, 33 - третий выход устройства, 34 - первый выход второго запоминающего блока, являющийся одновременно первым выходом устройства, 35 - второй вход второго запоминающего блока, 36 - третий выход второго запоминающего блока, являющийся одновременно вторым выходом устройства. В первом запоминающем блоке 3 хранятся микрокоманды с|р,(,гПдсостоящие из пяти полей, каждая из которых соответствует микропрограмме Р- ,ni0,. В первом поле dg,Иг-1,1(3разрядностью сЗт Poqf,(7 считываемом по первому выходу 27, содержится косвенный адрес номера следующей микропрограммы. Во втором поле С5р,рг1|тд,состоящем из одного разряда и считываемом по второму выходу 28, задается сигнал сброса регистра 1 адреса. В третьем поде Йр,В:;-|,т содержащем 84 разрядов и считываемом по третьему выходу 29, хранится код . проверяемых логических условий. В четвертом поле ag,,mQ разрядностью m считываемом по четвертому выходу ЗО, задается признак- (идентификатор) автономности текущей микропрограммы. В пятом поле а|, 2 i,m(j, содержащем cf разрядов и считываемом по nflToiv y выходу 31, хранится номер текущей микропрограммы. Регистр фиксации выполнения автоиомных микропрограмм 8 предназначен дпя хранения информации о выполненных уже адаптивным микропрограммным устройством управления автономных микропрограм мах Рд ,, т. Третья группа элементов И 9 управяя ет формированием сигналов, необходимых для управления считыванием соответствующего результата первого выполнения автономной микропрограммы РА, ( и его пересыпкой по требуемому адресу. Элемент обеспечивает выда чу на четвертую группу элементов И 11 сигнала, запрешаюшего пересыпку номера текущей автсдаомной микропрограммы, содержащего в пятом попе первого запоминаквдего блока cig в шифратор 12 при условии, что эта автономная микропрограмма уже однажды выпопнялась. 112 Во втором запоминающем бпоке 19 ( записаны микрокоманды из которых формируются все микропрограммы P/i состоящие из некоторых го1нейных последовательностей микрокоманд, количество которых соответствует текущему номеру микропрограммы, задаваемому в пятом попе РЛ, fl m nepBoro запоминающего блока 3. Каждая микрокоманда Ъу, ,Q состоит из трех полей разрядностью HQ И m соответственно. В первом, поле Ъу считываемом по первому выходу 34, задаются сигналы микроопераций, Сигнал со второго поля Ъ считываемый по второму выходу 35, осуществляет прибавление единицы к содержимому счетчика 17 адреса, а в случае, когда , кроме того, вычитание единицы из содержимого счетчика микрокоманд 13. В третьем поле toy, считываемом по третъему выходу 36, записывается единица, если данная микрокоманда принадлежит автономной микрокоманде , ,т к является в ней последней, Устройство работает следующим образом. Б исходном состоянии все элементы памяти находятся в нулевом состоянии, Код операции через первый вход 26 устройства поступает на регистр 1 адреса, задавая адрес соответствующей ячейке в первом запоминающем блоке 3. Генератор 21 тактовых импульсов через второй элемент 22 задержки и четверть1Й элемент И 23 при получении сигнала разрешения с выхода третьего элемента И 14, соответствующего нулевому содержимому счетчика 13 микрокоманд, производит установку в нуль счет ™ адреса, регистра 4 логических условий и буферного регистра 6, а также осуществляет пуск первого дешифратора 2. По сигналу дешифратора 2 с первого запоминающего блока 3 считывает микрокоманда ар 2 1,тр соответствующая первой выполняемой микропрограмме В ,-1,0 первой реализуемой программы , it.1,N.C выхода 27 первого запоминающего блока 3 в буферный регастр 6 записывается косвенный адрес номера следующей микропрограммы. Сигнал с выхода 28 устанавливает регистр 1 адреса в исходное состояние. С выхода 29 в регистр 4 логических условий записывается код проверяемых логических условий. Одновременно сигнал, соответствующий номеру текущей микропрограммы, с выхода 31 поступает через четвертую группу элементов И 11,

1393447114

открытую разрешающим сигналом с выхо- первый элемент И 16 и вторую группу

да элементов ИЛИ-НЕ вследствие {1улевого состояния всех выходов третьей группы элементов И 9, на вход шифратора 12, Нулевое состояние всех выходов тре тьей группы элементов И 9 обусловлено в этой ситуации нулевым содержанием всех m разрядов регистра 8 фиксации выполнения автономных микропрограмм. С выходов шифратора 12 в счетчик 13 микрокоманд записывается признак длины текущей микропрограммы, а в счет чик 17 адреса - адрес первой микрокоманды ,(Д текущей микропрограммы Pj .J .. После считывания информации из первого запоминающего блока 3 импульс 21 генератора через элементы 22 и 15 задержки первый элемент И 16 открывает вторую группу элементов И 7 и разрещает перезапись информации с регистра 6 на регистр 1. После считывания микрокоманд из пер вого запоминающего блока 3 и записи в счетчик 13 микрокоманд кода длины текущей микропрограммы его показания отличны от нуля. Поэтому сигнал на выходе третьего элемента И 14 принимает нулевое зна- чение и через первый элемент НЕ 24 от тсрывает второй элемент И 25, через который следующий тактовый импульс генератора 21 запускает второй дешифратор . 18, Далее по каждому тактовому импульсу генератора 21 в соответствии с адресом, записанном в счетчике 17 адреса из запоминающего блока 19 считываются микрокоманды .. ,С выхода 34 второго запоминающего блока считываются сигналы микроопераций, с выхода 35сигналы, увеличивающие на единицу содержимое счетчика 17 адресов и уменьшающее при Ъу ч иа единицу содержимое счетчика 13 микрокоманд. При показании счетчика 13 микрокоманд, отличных от нуля, следующий тактовый импульс аналогично описанному осуществляет считывание микрокоманд из второго запоминающего блока 19, В процессе работы адаптивного микропpoгpa lмнoгo устройства управления при получении на первом входе устройства 32 соответствующего сигнала с выходов элементов И первой группы 5 возможно изменение показаний буферного регистра 6, Если показание счетчика 13 микрокоманд равно нулю, то импульс генераторе 21 через элементы 22 и 15 задержки.

элементов И 7 передает адрес номера следующей микрокоманды, соответству-

ющий следующей а1кропрограмме реапи- зуемой программы R-,i 1|M с буфернс го регистра 6 на регистр 1 адреса. Следующий импульс генератора 21 через второй элемент 22 задержки и чет-вертый элемент И 23 устанавливает в исходное состояние счетчик 18 адреса, регастр 4 логических условий и буферный регистр 6. Кроме того, осуществляется запуск дешифратора 2, считывается микрокоманда dg,Р 1,т0из первого запоминающего блока 3 и работа устройства осуществляется аналогично описанному выше. В стучае считывания из первого запоминающего блока 3 микрокомандь, соот- ветствующей первой автономной микрокоманде Р,. , K,m выходов 30 на К-и элемент И третьей группы элементов И 9 поступает единичный сигнал, Однежо выходы третьей группы элементов И 9 по-пpeжнe Iy сохраняют нулевое состояние, так как все m разрядов регистра фиксации выполнения автономных микропрограмм 8 находятся в нулевом состоянии. Поэтому работа устройства осуществаяется аналогично описанному выще до пор, пока из второго запоминаюшего блока 19 не будет считана последняя микрокоманда Ъ, автономной микропрограммы Рд(. ,т.При этом на третьих выходах 36 второго запоминающего блока 19 снимается сигнал, в -м разряде которого записана единица. Этот сигнал подается на второй выход устройства для управления пересылкой попучае ° ° результате выполнения автономной микропрограммы РАО, ,Tt результата на хранение, с целью его дальиейщего использования при реализации других программ, содержащих автономную микропрограмму Р, ,т. Кроме того, этот же сигнал подается на вход регистра 8 фиксации выполнения автономных микропрограмм для запна в его Ц. -м разряде единицы. Пусть теперь в процессе дальнейшей работы при реализации некоторой другой программы потребуется выполнить автономную микропрограмму Р/((, ,т которая уже раз вьшолнялась адаптивным микропрограммным устройством управления, В этом случае при считывании микрокоманды, соответствующей требуемой автономной микропрограмме Рд|, ,т на четвертом выходе 30 в К - разряде появится единичный сигнал, который по ступит на К -и элемент третьей группы эпементов И 9. Этот элемент oткpытj по скольку в 1C -м разряде регистра фикса ции выполнения автономных микропрограмм 8 записана единица. В результате на выходе элемента ИЛ НЕ 1О формируется сигнал, запрещающий передачу через четвертую группу элемен тов И 11 текущего номера микрокоманды соответствующего данной автономной микрокомандне Р&у, K-,tn с пятого выхода 31 первого запоминающего блока 3 на вход шифратора 12. Одновременно с третьего выхода 33 устрой ства подается управляюидай сигнал на считывание хранящегося результата выпо нения автдаюмной. микропрограммы, Так как в этой ситуации счетчик 13 микрокоманд остается в нулевом состояНИИ, то импульс генератора 21 через элементы 22 и 15 задержки, первый эле мент И 16 и вторую группу элементов И 7 передает косвенный номер следующей микрокоманды ) первого запоминающего блока 3 в регистр 1 адреса, Дальще устройство работает аналогично описанному выше, В случае необходимости вьшолнения рассматриваемой автономной микропрограммы Рдц, К 1, m в третий, четвертый, .,., раз устройство работает Точно так же, как и при вторичном ее вьшолнении. При реализации любой другой автоном ной микрокоманды из подмножества Рд работа адаптивного микропрограммного устройства управления отличается только расположением единиц в считываемых кО mxaJ.Pzi; , . При поступлении на вход 26 нового кода операции после вьшолнения набора программ, кроме записи его в регистр 1 адреса, осуществляется установка в нуль регибтра 8 фиксации выполнения автоном ных микропрограмм. Таким образом, соединение третьего выхода .36 второго запоминающего блока 19 с вторым выходом устройства и первым входом регистра 8 фиксации выполнения автономных микропрограмм, вход установки в нуль которого соединен с пе вым входом 26 устройства, а выход соединен с первыми входами элементов И третьей группы элементов И 9, вторяле вхопы которых подключены к четвертому выходу ЗО первого запоминающего блока 3, а выходы соединены с третьим выходом 33 устройства и входами элемента 10 ИЛИ-НЕ, выход которого соединен с первыми входами элементов И четвертой группы элементов И 11, вторые входы которых соединены с пятыми выходами 31 первого запоминающего блока 3, а выход соединен с входом шифратора 12, позволяет повысить быстродействие устройства в целом. Это следует из того, что при последовательной реализации всех N программ м1 южества R:R.,if1,M каждая Рд, .т автономная микропрограмма подмножества Р вьшопняется адаптивным микропрограммным устройством управления не N С г23 К . -ki . М раз, как это делается в известном, а только однажды. Если автономная микропрограмма Pju. выполняется за время , то за счет отсутствия повторной реализации одной микропрограммы выигривается время fN ,Следовательно, при последовательной реализации всего подмножества , ,1 величину выигрьпиа времени (повьпиения быстродействия) можно определить по формуле -МдТ ПлП :131т Ши Формула изобрет. ения Адаптивное микропрограммное устройство управления, содержащее регистр адреса, первый и второй дешифраторы, первый и второй запоминающие блоки, регистр логических условий, перую и вторую группы элементов И, буферный регистр, шифратор, счетчик микрокоманд, первый, второй, третий и четвертый элементы И, первый и второй элементы задержки, счетчик адресов, первый и второй элементы НЕ и генератор тактовых импульсов, причем адресный вход регистра адреса подключен к первому входу устройства, выход регистра адреса соединен с первым входом первого дешифратора,, а выход - с входом первого запомимннающего блока, первый, второй и третий выходы КОТОРОГО соединены соответственно с входом адреса буферного регистра, входом установки в нуль регистра адреса и информационным входом регистра логических условий, выходы которого соединены с первыми входами элементов И первой группы, вторые входы которых подкгаочены к второй группе входов устройства, а выходы соединены с группой входов логических условий буферного регистра, выходы которого соединены с первыми входами элементов И второй группы, вторые вхсады и выходы которых соединены соответственно с выходом первого элемента И и группой входов

косвенного адреса регистра адреса, первый «лход шифратора соединен с первым входом счетчика микрокоманд, первый и второй входы второго элемента И соединены соответственно с ш 1ходом генератора тактовых импульсов и выходом первого элемента НЕ, вход которого соединен с вь1ходом третьего элемента И и первым входом четвертого элемента И, второй вход которого соединен с входом первого и выходом второго элементов задержки, первый и второй входы первого элемента задержки соединены соответственно с выходами первого элемента задержки и третьего элемента И, вход второго элемента задержки соединен с выходом генератора тактовых импульсов, выход Четвертого элемента И соединен с BTOfftiM входом первого дешифратора, входами установки в нуль регистра логических условий и буферного регистра и первым входом счетчика адресов, втсфой и третий входы и которого соединены соответственно с входом второго элемента НЕ, вторым выходом шифратора и первым входом второго дешифрато- ра, второй вход и выход которого соединены соответственно с выходом второго элемента И и входом второго запоминающего блока,группа выходов кода микрооперации которого является групповым выходом кода микрооперации устройства, а выход адресного признака соединей с

входом второго элемента НЕ, выход которого соединен с вторым входом счетчика микрокоманд, выходы которого соединены с входами третьего элемента И, о т л и чающееся тем, что, с целью повышения быстродействия, в него введены регистр фиксации выполнения автономных микропрограмм, третья и четвертая группы элементов И и элемент ИЛИ-НЕ, причем группа информационных входов, вход установки в нуль и выходы регистра фиксации выполнения автономных микропрограмм соединены соответственно с группой выходов признака автономности микропрограммы второго запоминающего блока, первым входом регистра адреса и первыкЛ входами элементов И третьей группы, вторые входы и выходы которых :соединены соответственно с группой выходов признака автономности текущей микропрограммы первого запоминающего блока и входами элемента ИЛИ-НЕ, выход которого соединен с первыми входами элементов И четвертой группы, вторые входы и выходы которых соединены соответственно с группой выходов номера текущей микропрограммы первого запоминающего блока и входами шифратора, группа выходов признака автономности текущей микропрограммы второго запоминающего блока является групповым выхсмом признака автономности текущей микропрограммы устройства, выходы элементов И третьей группы являются группой выходов признака считывания результата устройства.

Источники информации, принятые во внимание при экспертизе

кл. G 06 F 9/16, 1978 (прототип).

Авторы

Даты

1982-06-07—Публикация

1980-04-25—Подача