1

Изобретение относится к импульсной технике.

Известен делитель частоты импульсов с управляемым коэффициентом деления, состоящий из двух основных частей: делителя с целочисленным переменным коэффициентом деления (ДПКД) и программирующего устройства, в определенной последовательности изменяющего коэффициенты деления в различных циклах в процессе работы делителя. В результате при усреднении коэффициенты не равны целому числу. Такие делители используются при построении цифровых синтезаторов частот и предназначены для снижения уровня пульсаций опорного колебания в управляющем сигнале, а также повышения динамических свойств системы за счет увеличения частоты сравнения при сохранении малого щага дискретности частот выходного сигнала 1.

Однако у известных ДИКД минимальная дискретность приращения коэффициента деления в различных циклах деления равна единице.

Наиболее близким по технической сущности к данному изобретению является управляемый цифровой делитель частоты, содержащий делитель частоты с переменным коэффициентом деления, один вход которого соединен с выходом блока исключения импульсов.

а выход соединен со входом блока программы, один выход которого подключен к первому входу блока исключения импульсов, второй вход которого соединен с источником

входного сигнала, а третий вход - со вторым выходом делителя частоты с переменным коэффициентом деления ,2.

Недостатком такого делителя является малая дискретность изменения коэффициента деления.

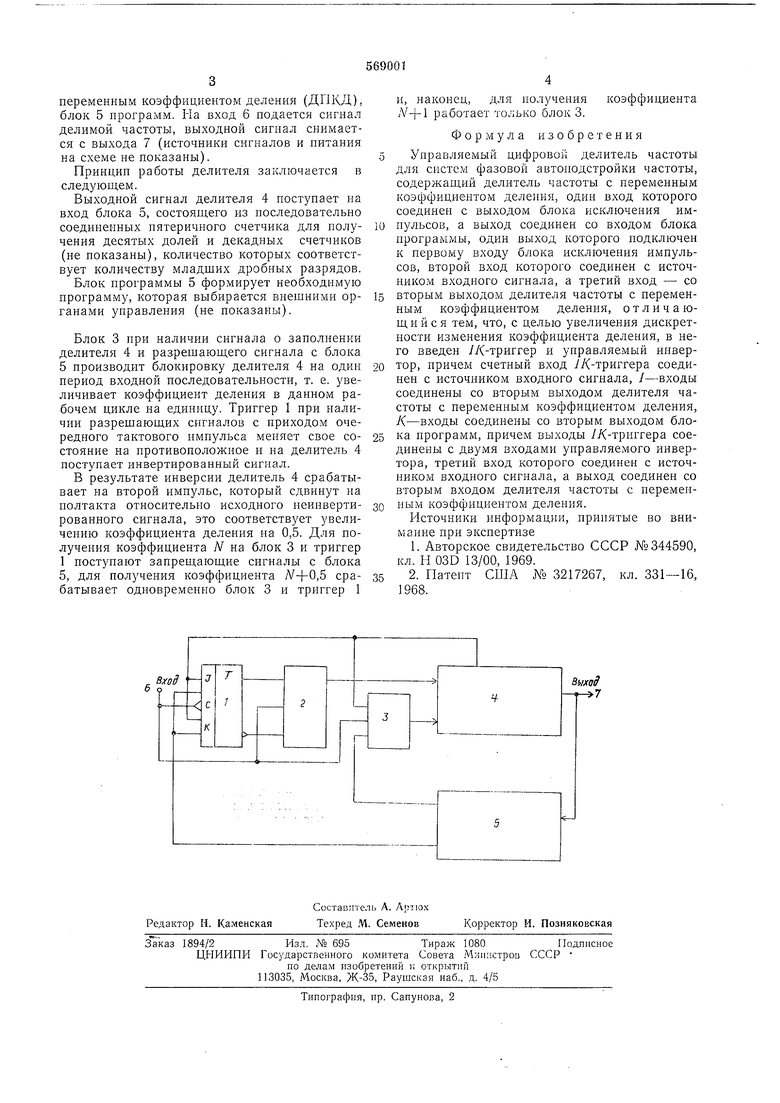

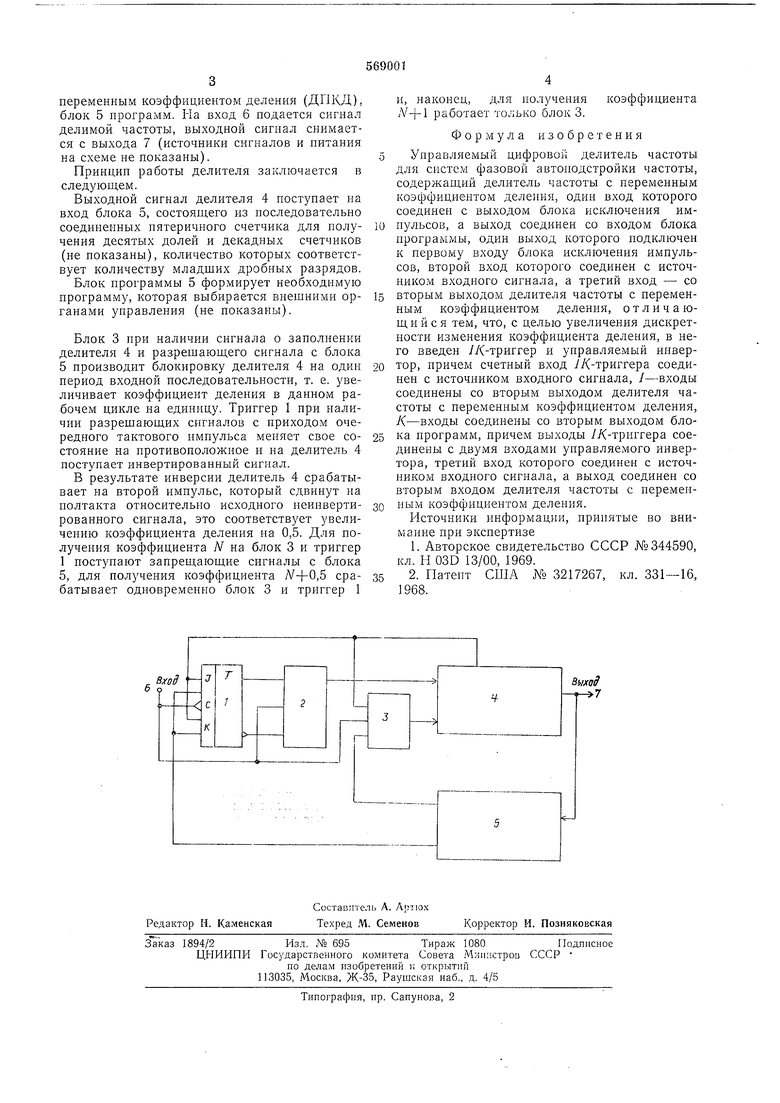

С целью увеличения дискретности изменения коэффициента деления в предлагаемый делитель частоты введен //(-триггер и управляемый инвертор, причем счетный вход

//(-триггера соединен с источником входного сигнала, I - входы соединены со вторым выходом делителя частоты с переменным коэффициентом деления, К. - входы соединены со вторым выходом блока программ, причем выходы //(-триггера соединены с двумя входами управляемого инвертора, третий вход которого соединен с источником входного сигнала, а выход соединен со вторым входом делителя частоты с переменным коэффициентом деления.

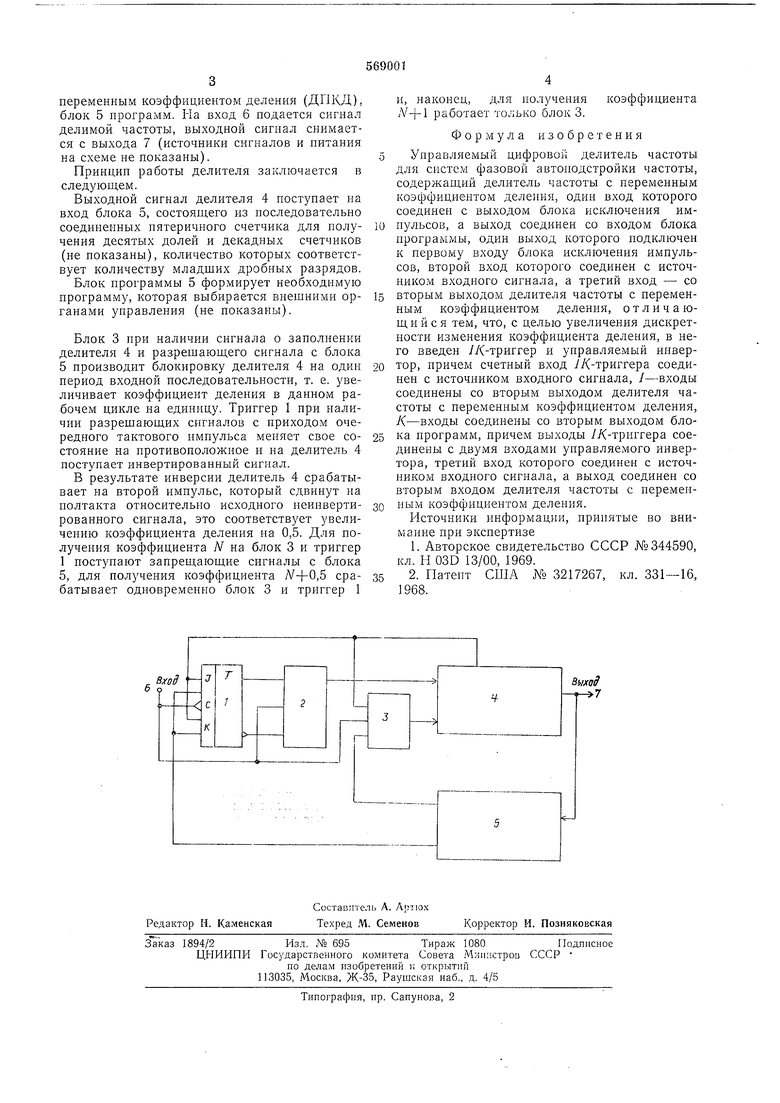

На чертеже приведена структурная электрическая схема предлагаемого делителя.

Делитель содерл ит триггер //(-тина 1, управляемый инвертор 2, блок 3 исключения

импульсов, делитель 4 частоты импульсов с

переменным коэффициентом деления (ДГ1КД), блок 5 нрограмм. На вход 6 подается сигнал делимой частоты, выходной сигнал снимается с выхода 7 (источники сигналов и питания на схеме не показаны).

Принцип работы делителя заключается в следующем.

Выходной сигнал делителя 4 поступает па вход блока 5, состоящего из носледовательпо соедипепных пятеричного счетчика для получения десятых долей и декадных счетчиков (не показаны), количество которых соответствует количеству младших дробных разрядов.

Блок программы 5 формирует необходимую программу, которая выбирается внешними органами управления (не показаны).

Блок 3 при наличии сигнала о заполнении делителя 4 и разрешающего сигнала с блока 5 производит блокировку делителя 4 на один период входной последовательности, т. е. увеличивает коэффициент деления в данном рабочем цикле па единицу. Триггер 1 при наличии разрешающих сигналов с приходом очередного тактового импульса меняет свое состояние на противоположное и па делитель 4 поступает инвертированный сигнал.

В результате инверсии делитель 4 срабатывает на второй импульс, который сдвинут на полтакта относительно исходного неипвертированного сигнала, это соответствует увеличению коэффициента деления иа 0,5. Для получения коэффициента jV на блок 3 и триггер 1 поступают запрещающие сигналы с блока 5, для получения коэффициента //+0,5 срабатывает одновременно блок 3 и триггер 1

коэффициента

и, наконец, для получения jV+1 работает только блок 3.

Формула изобретения

Управляемый цифровой делитель частоты для систем фазовой автоиодстройки частоты, содержащий делитель частоты с переменным коэффициентом деления, один вход которого соединен с выходом блока исключения импульсов, а выход соединен со входом блока программы, один выход которого подключен к первому входу блока исключения импульсов, второй вход которого соединен с источником входного сигнала, а третий вход - со

вторым выходом делителя частоты с переменным коэффициеитом деления, отличающийся тем, что, с целью увеличения дискретности изменения коэффициента деления, в него введен //(-триггер и управляемый иивертор, причем счетный вход //(-триггера соединен с источииком входного сигиала, /-входы соединены со вторым выходом делителя частоты с переменным коэффициентом деления, /(-входы соединены со вторым выходом блока программ, причем выходы //(-триггера соединены с двумя входами управляемого инвертора, третий вход которого соединен с источником входного сигнала, а выход соединен со вторым входом делителя частоты с неременным коэффициентом деления.

Источники информации, принятые во внимаиие при экспертизе

1. Авторское свидетельство СССР №344590, кл. Н 03D 13/00, 1969.

2. Патепт США N° 3217267, кл. 331-16, 1968.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления частоты следования импульсов | 1978 |

|

SU746915A1 |

| Делитель частоты следования импульсов | 1981 |

|

SU953738A1 |

| Программируемый делитель частоты | 1976 |

|

SU657615A1 |

| Устройство для преобразования частоты | 1982 |

|

SU1086553A1 |

| Синтезатор частот | 1985 |

|

SU1312732A1 |

| Делитель частоты с переменным коэффициентом деления | 1973 |

|

SU482898A1 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| Цифровой синтезатор частот | 1986 |

|

SU1483632A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2379830C1 |

т

с /

к

Авторы

Даты

1977-08-15—Публикация

1976-03-30—Подача