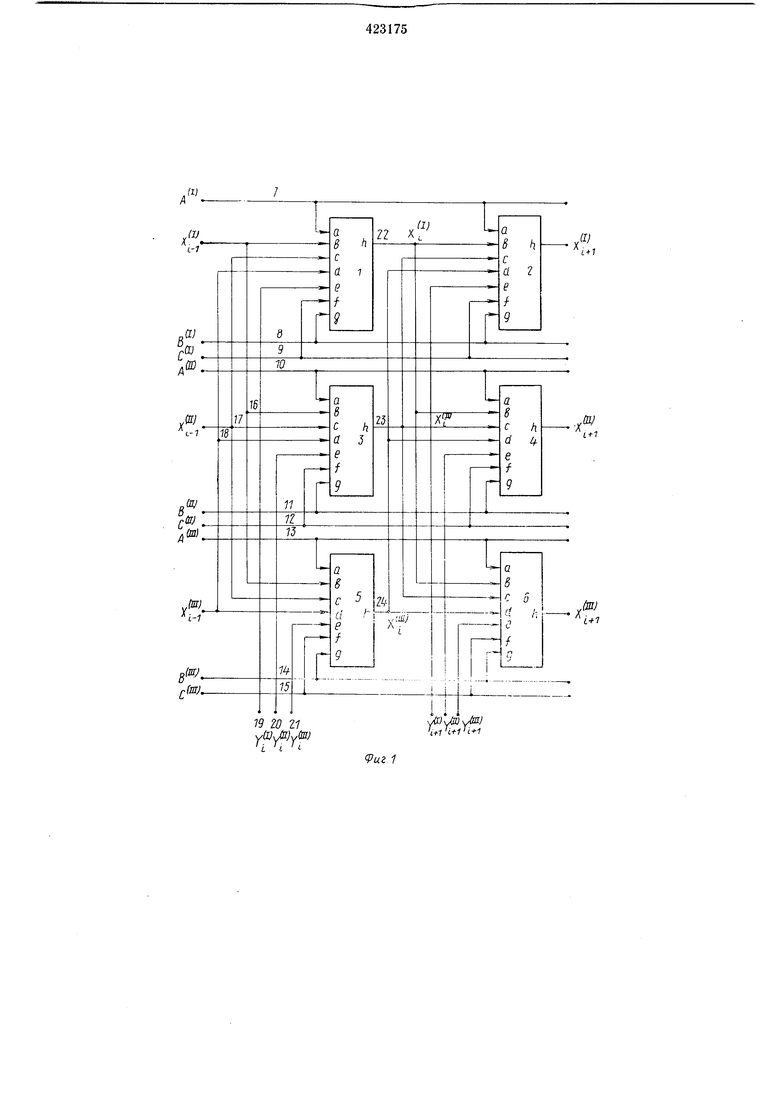

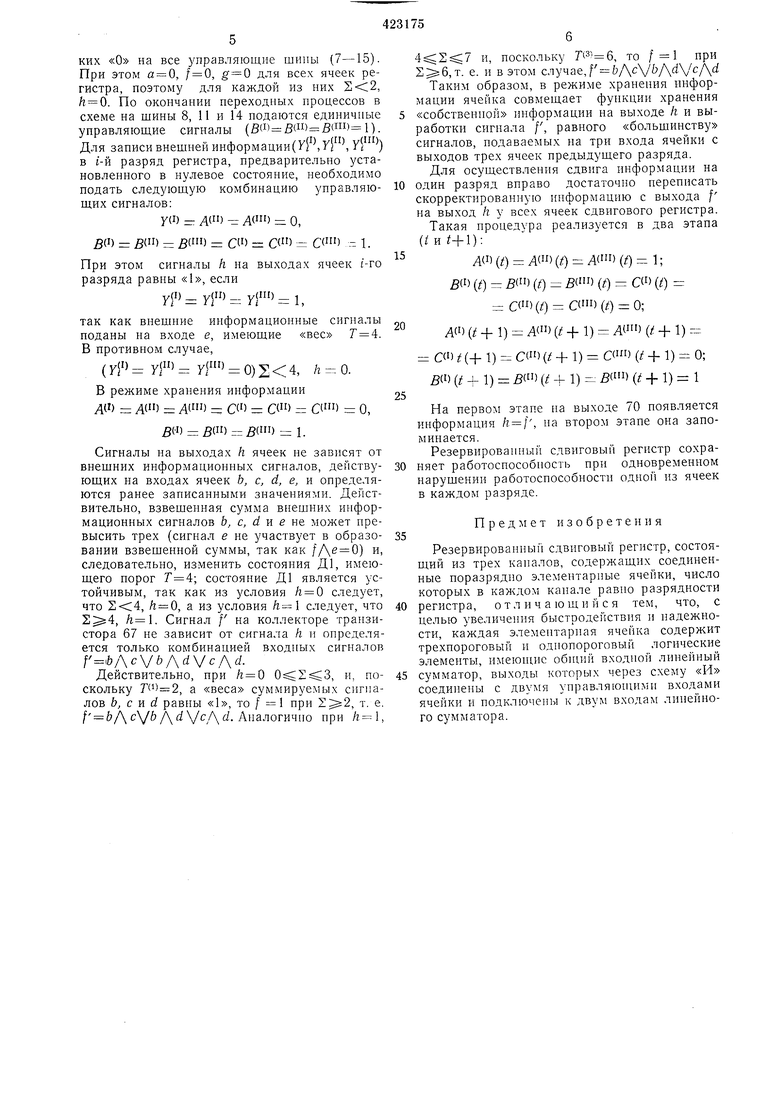

соединены через соответствующие «весовые резисторы 43-47 с положительным источником питания 48. Катоды диодов 26, 28, 30, 33, 36 и 39 объединены в точке 49, соединенной через три последовательно включенных «суммирующнх резистора 50-52 с отрицательным источником питания 53. Точка 54 объединения резисторов 50 и 51 соединена с эмиттером транзистора 55, база которого через резистор 56соединена с источником нитания 48. Точка 57объединения резисторов 51 и 52 присоединена к базе транзистора 58, эмиттер которого «заземлен. Точка 49 соединена с нервым эмиттером двухэмиттерного транзистора 59, база которого через резистор 60 соединена с источником питания 48. Коллектор транзистора 55 соединен с базой транзистора 61, эмиттер которого «заземлен. Коллектор транзистора 61, объединенный со вторым эмиттером транзистора 59 и с анодом диода 62, соединен через резистор 63 с источником нитания 4-2. Катод диода 62, объединенный с базой транзистора 64, соединен через резистор 65 с «земляной шиной. Коллектор транзистора 59 соединен с базой транзистора 66, эмиттер которого «заземлен. Точка объединения коллекторов транзисторов 66 и 58 и базы транзистора 67, имеющего «заземленный эмиттер, соединена через резистор 68 с положительным источником питания 42 и через резистор 69 с «земляной щиной. Коллектор транзистора 64, объединенный с катодом диода 40 в точке 70(выход /1 ячейки), соединен через резистор 71с источником питания 42. Коллектор транзистора 67 (точка /) соединен с точкой объединения анодов диодов 25 и 26. Линейный сумматор состоит из элементов 25-41, 43-47, 50-52, однопороговый дискриминатор (Д1) -из элементов 55, 56, 61-65 и 71, трехпороговый дискриминатор (Д2) из элементов 55, 56, 58, 59-61, 63-41. Резистор 41 является общим для линейного сумматора и дискриминатора Д2, а элементы 55, 56, 61, 63 - для дискриминаторов Д1 и Д2. Регистр работает следующим образом. Линейный сумматор предназначен для суммирования токов, протекающих через «весовые резисторы 41, 43.-47 в точку 49. Суммарный ток протекает через резисторы 50-52 к источнику нитания 53. Сопротивления «весовых резисторов обратно пропорциональны их «весам. Причем «веса резисторов 43-45 равны единице, «веса резисторов 46 и 47 - четырем, а «вес резистора 41 должен быть больще или равен щести. При наличии тех или иных комбинаций входных сигналов (входами линейного сумматора являются катоды диодов 25, 27, 29, 31, 32, 34, 35, 37, 38, 40) ток через суммирующие резисторы 50-52 можно характеризовать так называемой взвещенной суммой (S), равной сумме «весов тех весовых резисторов, через которые течет ток в точку 49. Например, если на катоды диодов 27, 29, 31, 32, 34, 38 и 40 нодан высокий положительный потенциал (ло гическая «1), а на катоды диодов 25, 35, 37- низкий (логический «О), то взвешенная сумма, характеризующая величину тока через «суммирующие резисторы 50-52, равна семи. Однонороговый дискриминатор Д1, входом которого является точка 54, имеет «порог, равный четырем (Г 4), т. е. сигнал на его выходе (точка 70) /г 1 только в том случае, когда взвещенпая сумма . При этом потенциал в точке 54 достаточно высок для того, чтобы ток от источника питания 48 втекал в базу транзистора 61 через транзистор 55, что обеспечивает выключение транзистора 64 и ноявление логической «1 в точке 70 (на выходе h ячейки). Если , то ток от источника нитания 48 течет через резистор 56 и нереход база-эмиттер транзистора 55 в точку 54, что приводит к выключению транзистора 61. При этом ток от источника питания 42 течет через резистор 63 и диод 62 в выходной каскад, транзистор 64 открывается, и в точке 70 устанавливается низкий потенциал (/г 0). Трехпороговый дискриминатор Д2, входами которого являются точка 49 и резисторы 45 и 47, вырабатывает на выходе f (коллектор транзистора 67) сигнал «Ь только в тех ситуациях, когда взвещенная сумма удовлетворяет одному из следующих условий: Г(1) или (3) 6. Первое условие соответствует случаю, когда потенциал в точке 49 оказывается выше порога срабатывания инвертора на транзисторах 59 и 66, но ниже норога срабатывания инвертора на транзисторах 55 и 61 и ниже порога открывания транзистора 58. При этом транзистор 66 включается, транзисторы 58 и 67 выключаются, и потенциал на коллекторе транзистора 67 соответствует логической «1. При выполнении второго условия () потенциал в точке 57 достаточен для открывания транзистора 58, что также приводит к появлению потенциала логической «1 на коллекторе закрытого транзистора 67. При потенциалы в точках 49, 54 и 57 недостаточны для открывания- транзисторов 66, 61 и 58 соответственно, что приводит к появлению потенциала логического «О на коллекторе открытого транзистора 67. При потенциал в точке 54 достаточно высок для открывания инвертора на транзисторах 55 и 61, а потенциал в точке 57 недостаточен для отпирания транзистора 58. Это приводит к тому, что ток от источника нитания 48 нротекает через резистор 60 и второй эмиттер транзистора 59 в коллектор открытого транзистора 61, что, в свою очередь, вызывает запирание транзистора 66 и, следовательно, включение выходного транзистора 67, на коллекторе которого появляется потенциал логического «О. Рассмотрим цикл работы исправного резервированного сдвигового регистра. Для установки регистра в исходное (нулевое) состояние подают потенциалы логических «о на все управляющие шипы (7-15). При этом а 0, , 0 для всех ячеек регистра, поэтому для каждой из них , ft 0. По окончании нереходных процессов в схеме на шины 8, 11 и 14 подаются единичные управляющие сигналы (S(i) (). Для записи внещней информации (И У ) в t-й разряд регистра, предварительно установленного в нулевое состояние, необходимо подать следующую комбинацию управляющих сигналов:

у(1) - д(11) - д(111) - о,

Б() 5( 5() С() - ) - 1.

п,.

При этом сигналы h па выходах ячеек 1-го

разряда равны «1, если

,

так как внещние информационные сигналы поданы па входе е, имеющие «вес 7 4. В противном случае,

()УР) yp 0), ft.0. В режиме храпения информации

Д(1) - Д(11) Д(П1) - С(1) С(П) С(1И) о,

g() - 5() 5() 1.

Сигналы па выходах h ячеек не зависят от внещпих информационных сигналов, действующих на входах ячеек Ь, с, d, е, и определяются ранее записанными значениями. Действительно, взвещенная сумма внещпих информационных сигналов Ь, с, d и е не может превысить трех (сигнал е не участвует в образовании взвешенной суммы, так как /Де 0) и, следовательно, изменить состояния Д1, имеющего порог состояние Д1 является устойчивым, так как из условия /г 0 следует, что , Л 0, а из условия h следует, что , . Сигнал / на коллекторе транзистора 67 не зависит от сигнала /г и определяется только комбинацией входных сигналов ,d.

Действительно, при /i 0 , и, поскольку Г(, а «веса суммируемых сигналов Ь, с и d равны «1, то f 1 при , т. е. / A V A V A -Аналогично нри ,

и, поскольку Г(, то f 1 при ,т. е. и в этом случае, f

Таким образом, в режиме хранения информации ячейка совмещает функции хранения «собственной информации на выходе Л и выработки сигнала /, равного «больщинству сигналов, подаваемых на три входа ячейки с выходов трех ячеек предыдущего разряда.

Для осуществления сдвига информации па один разряд вправо достаточно переписать скорректированную информацию с выхода f на выход h у всех ячеек сдвигового регистра.

Такая процедура реализуется в два этапа ():

Л(1)() Л()(;) Л()() 1; 5(1) (/) 5() (О - 5(1) (/) С(1) (/)

С() (О О ) ((} 0; АО ( + 1) А) ( + 1) А() (( + 1) г СО t(+l} С() (г -f 1) C(i) ( + 1) 0; 5(1) (i + l) 5() (( + 1) : 5(1) (г 4-1) 1

На первом этапе на выходе 70 появляется информация h f, на втором этапе она запоминается.

Резервированный сдвиговый регистр сохраняет работоспособность при одновременном нарушении работоспособности одной из ячеек в каждом разряде.

Предмет изобретения

Резервированный сдвиговый регистр, состоящий из трех каналов, содержащих соединенные поразрядно элементарные ячейки, число которых в каждом канале равно разрядности регистра, о т л и ч а ю щ и и с я тем, что, с целью увеличения быстродействия и надежности, каждая элементарная ячейка содержит трехнороговый и однопороговый логические элементы, имеюище общий входной линейный сумматор, выходы которых через схему «И соедииены с двумя унравляюн1ими входами ячейки и подключены к двум входам линейного сумматора.

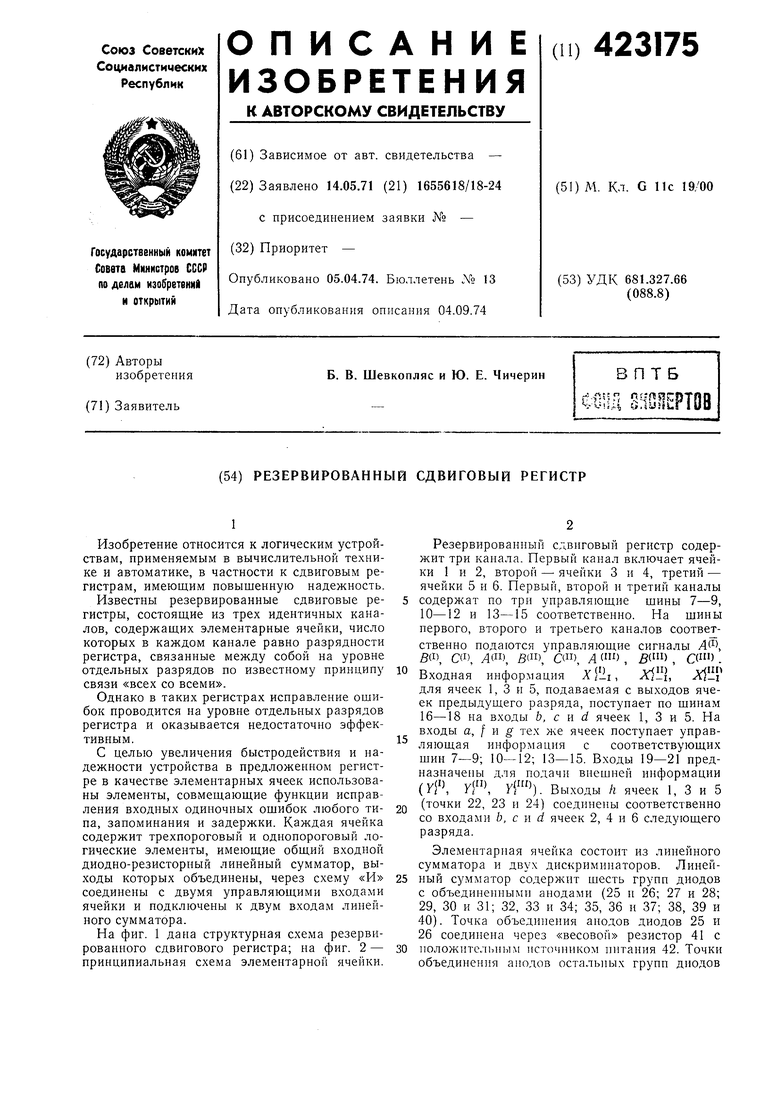

19 20 11 )у(Ш) L L i

n.in-ii -i

9иг 1

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1971 |

|

SU319077A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО ДЛЯ РЕГУЛЯТОРОВ СКОРОСТИ с ИМПУЛЬСНЫМИ ДАТЧИКАМИ СКОРОСТИ | 1971 |

|

SU296381A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПЕРЕДАЧИ ПОСЛЕДОВАТЕЛЬНОСТИ СИГНАЛОВ | 2005 |

|

RU2299474C2 |

| Шахматные часы | 1988 |

|

SU1693619A1 |

| Оптоэлектронный модуль | 1984 |

|

SU1274155A1 |

| Многопороговый логический элемент | 1983 |

|

SU1132366A2 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1973 |

|

SU370728A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ И ПЕРЕДАЧИ СИГНАЛОВ | 2004 |

|

RU2282246C2 |

Даты

1974-04-05—Публикация

1971-05-14—Подача