1

Изобретение относится к импульсной технике.

Известен управляемый делитель частоты, содержащий входную шину, счетчик, информационный вход которого через устройство записи обратного кода соединен с шиной информационного входа, и выходную шину.

(Эднако известный делитель имеет недостаточную надежность и быстродействие.

Целью изобретения является повышение надежности работы и быстродействия.

Для этого в нем дополнительно установлены второй счетчик и второе устройство записи обратного хода, схема «ИЛИ, две схемы совпадения «И и триггер, причем входная шина через схемы совпадения «И соединена со счетными входами первого и второго счетчиков, информационный вход второго счетчика через второе устройство записи обратного кода соединен с шиной информационного входа, нулевой выход триггера соединен с первой схемой совпадения «И и вторым устройством записи обратного кода, ед,иничный выход триггера соединен со второй схемой совпадения «И и первым устройством записи обратного кода, а выходы счетчиков соединены с нулевым и единичным входами триггера и схемой «ИЛИ, выход которой подключен к выходной шине.

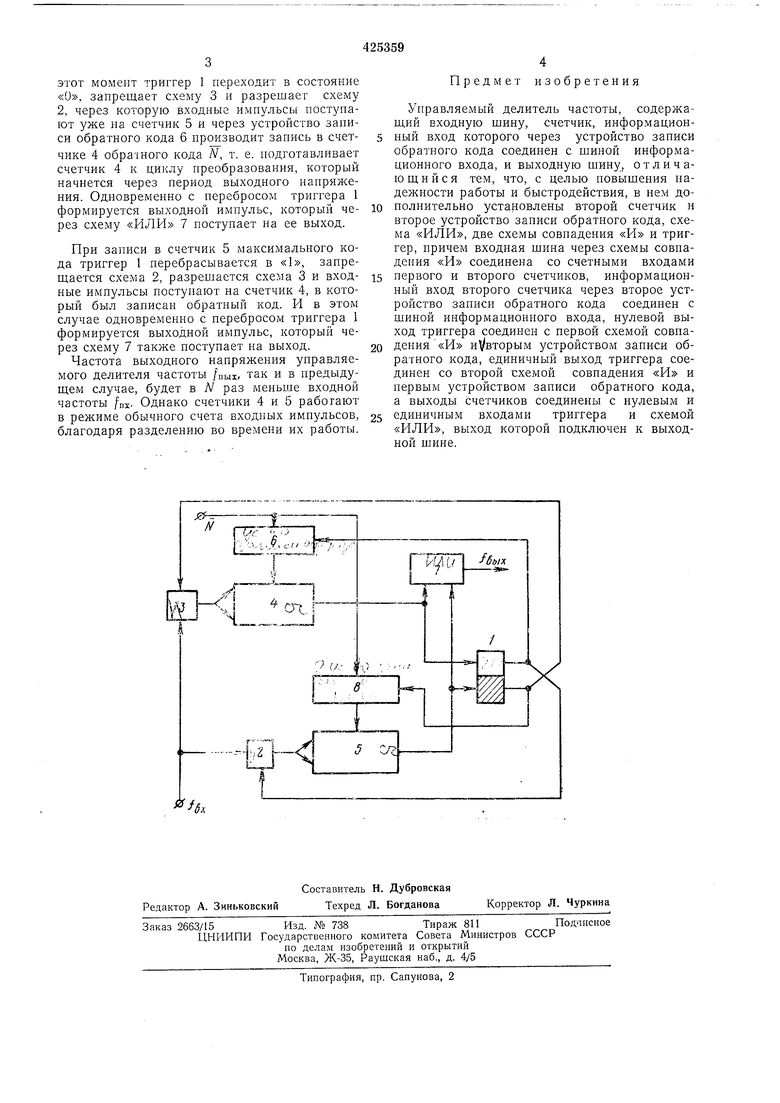

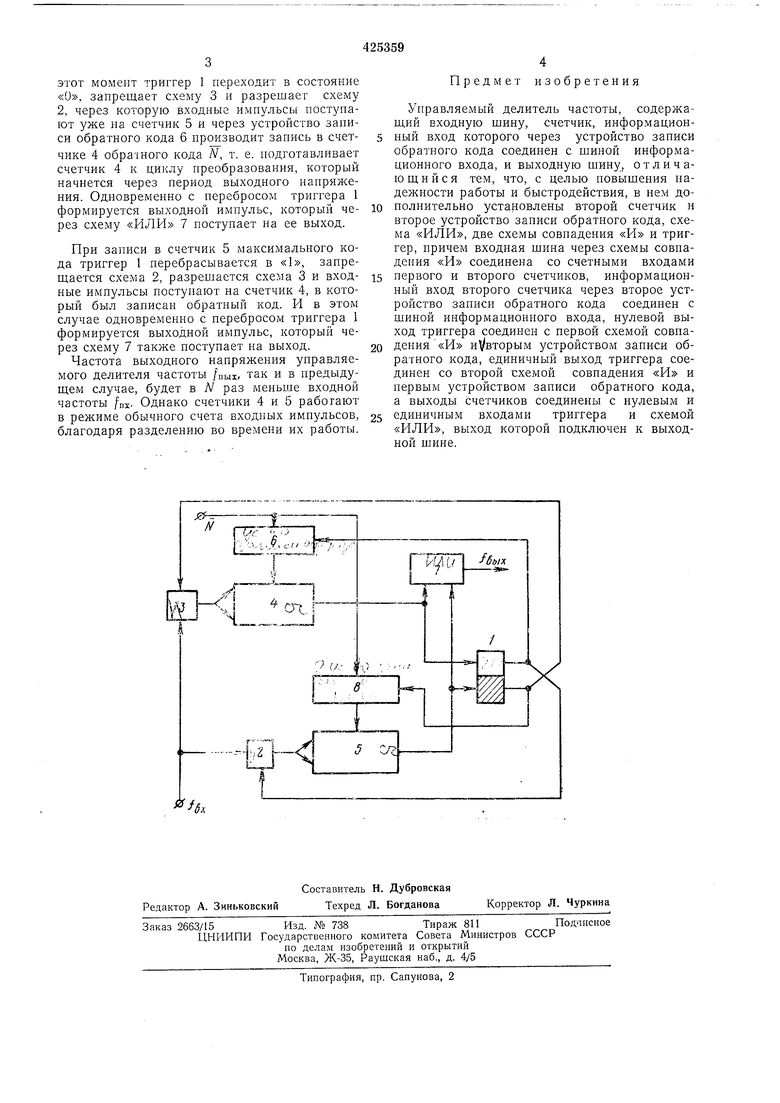

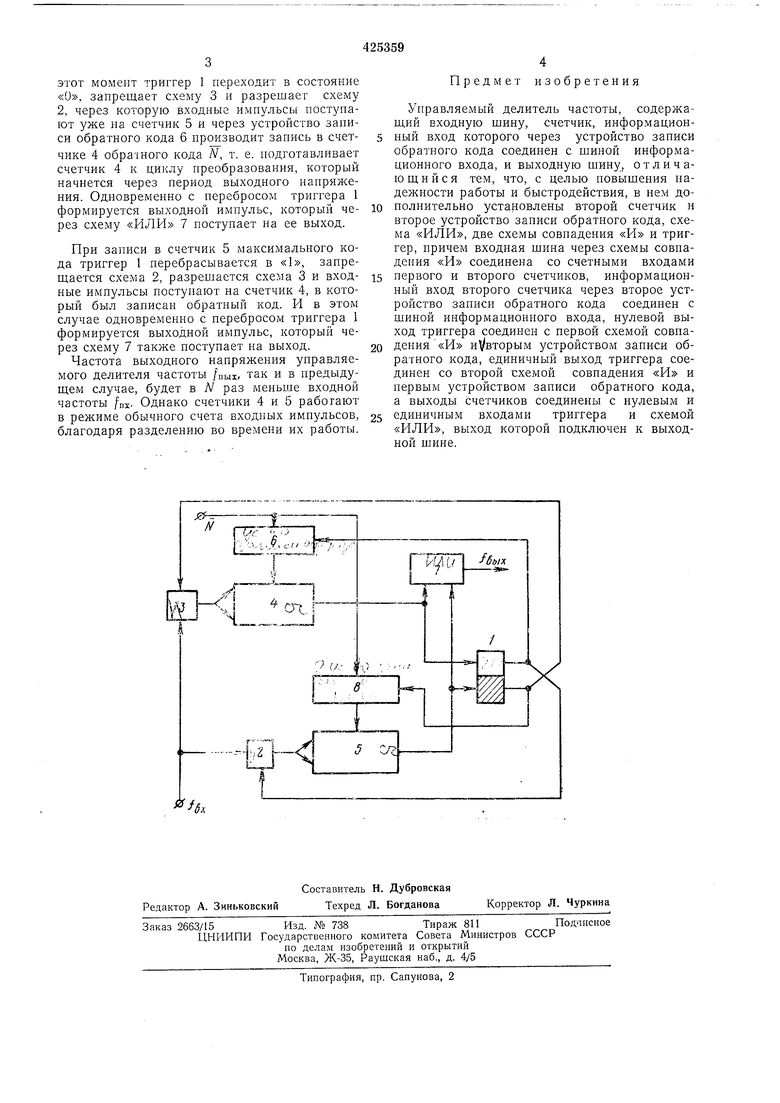

На чертеже приведена блок-схема делителя.

Управляемый делитель частоты содержит триггер I, схемы совпадения «И 2, 3, счетчики 4, 5, устройство записи обратного кода 6, схема «ИЛИ 7, второе устройство записи обратного, кода 8, причем информационные входы счетчиков 4, 5 соединены через устройства записи обратного кода б, 8 соответственно с

шиной информационного входа; входная шина через схемы совпадения «И 2, 3 соединена со счетными входами первого и второго счетчиков 4, 5, нулевой выход триггера 1 соединен со схемой совпадения «И 3 и вторым устройством записи кода 8, единичный выход триггера 1 соединен со схемой совпадения «И 2 и устройством записи обратного кода 6, а выходы счетчиков 4, 5 с единичным и нулевым входами триггера и схемой «ИЛИ 7, выход которой подключен к выходной шипе.

Делитель частоты работает следуюш,им образом.

Пусть триггер 1 находится в состоянии «I, при котором на схему совпадения «И 2 поступает запрет, а на схему совпадения «И 3 - разрешение. Импульсы входного нанряжения, поступающие непрерывно на схемы 2 и 3, будут проходить только через схему 3 и подсчитываться счетчиком 4 до тех пор, пока

в нем не запишется максимальный код. В

этот момент триггер 1 переходит в состояние «О, запрещает схему 3 и разрешает схему 2, через которую входпые импульсы поступают уже на счетчик 5 и через устройство записи обратного кода 6 производит запись в счетчике 4 обратного кода Л, т. е. подготавливает счетчик 4 к циклу преобразования, который начнется через период выходного иапрял ения. Одновременно с перебросом триггера 1 формируется выходной импульс, который через схему «ИЛИ 7 поступает на ее выход.

При записи в счетчик 5 максимального кода триггер 1 перебрасывается в «1, запрещается схема 2, разреидается схема 3 и входные импульсы поступают на счетчик 4, в который был записан обратный код. И в этом случае одновременно с перебросом триггера 1 формируется выходной импульс, который через схему 7 также поступает на выход.

Частота выходного напряжения управляемого делителя частоты /вых, так и в предыдущем случае, будет в Л раз меньше входной частоты /их. Однако счетчики 4 и 5 рабогают в режиме обычного счета входных импульсов, благодаря разделению во времени их работы.

Предмет изобретения

Управляемый делитель частоты, содержащий входную щину, счетчик, информационный вход которого через устройство записи обратного кода соединен с щиной информационного входа, и выходную щину, отличающийся тем, что, с целью повышения надежности работы и быстродействия, в нем дополнительно установлены второй счетчик и второе устройство записи обратного кода, схема «ИЛИ, две схемы совпадения «И и триггер, причем входная шина через схемы совпадения «И соединена со счетными входами

первого и второго счетчиков, информационный вход второго счетчика через второе устройство записи обратного кода соединен с шиной информационного входа, нулевой выход триггера соединен с первой схемой совпадения«И иУвторым устройством записи обратного кода, единичный выход триггера соединен со второй схемой совпадения «И и первым устройством записи обратного кода, а выходы счетчиков соединены с нулевым и

единичным входами триггера и схемой «ИЛИ, выход которой подключен к выходной шине.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь пачек импульсов | 1983 |

|

SU1150738A1 |

| Делитель частоты следования импульсов с программным управлением | 1979 |

|

SU873416A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Устройство для циклового программного управления | 1986 |

|

SU1381432A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU875642A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1248062A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Делитель частоты следования импульсов с автоматически изменяющимся коэффициентом деления | 1984 |

|

SU1221746A1 |

| Делитель частоты с переменным коэффициентом деления | 1990 |

|

SU1812636A1 |

| Управляемый делитель частоты следования импульсов | 1980 |

|

SU953734A1 |

Даты

1974-04-25—Публикация

1971-12-16—Подача