оо ас

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1262504A1 |

| Сигнатурный анализатор для поиска перемежающихся неисправностей | 1986 |

|

SU1495799A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2007814C1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для проверки исправности многопроводных кабелей | 1987 |

|

SU1638673A1 |

Изобретение относится к области автоматики и может быть использовано в системах программного управления объектами. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения отработки независимых программ управления. Устройство обеспечивает параллельную отработку нескольких независимых программ управления, а благодаря наличию многократного погруппового опроса датчиков положения обеспечивается повышение достоверности информации о состоянии датчиков положения и сокращение информационных линий связи. 2 3. п. ф-лы, 8 ил.

Изобретение относится к автоматике и может быть использовано в системах программного управления объектами.

Цель изобретения - расширение функциональных возможностей устройства путем обеспечения отработки независимых программ управления.

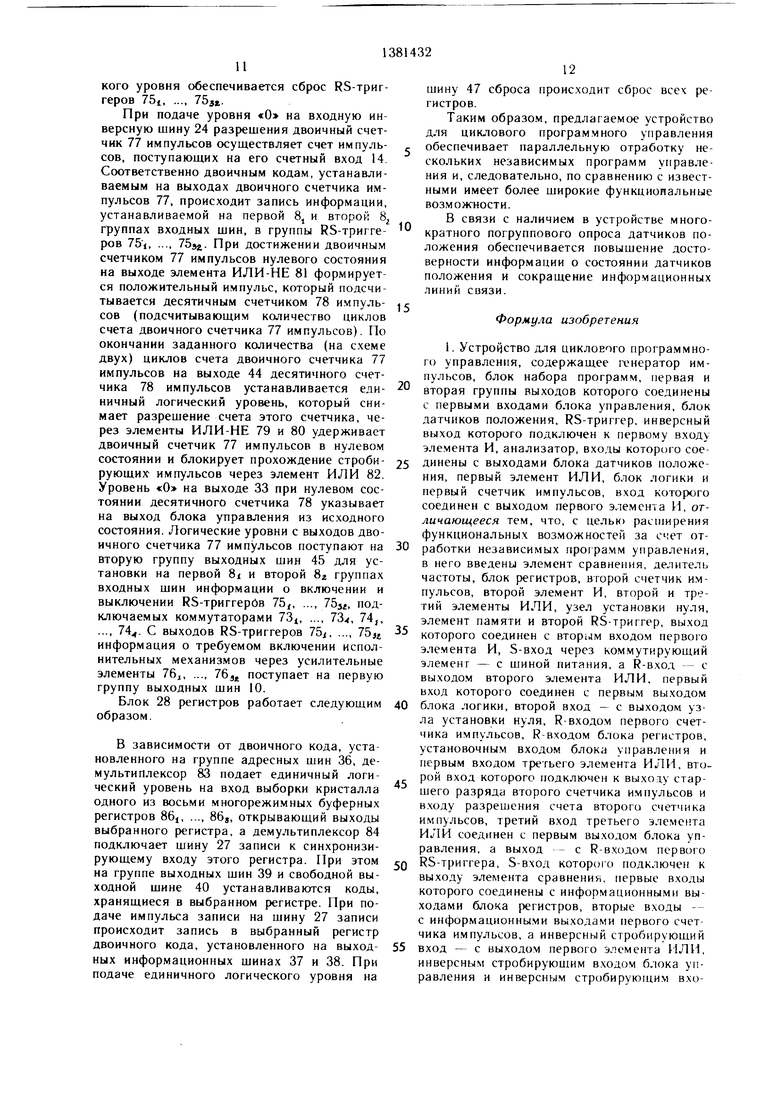

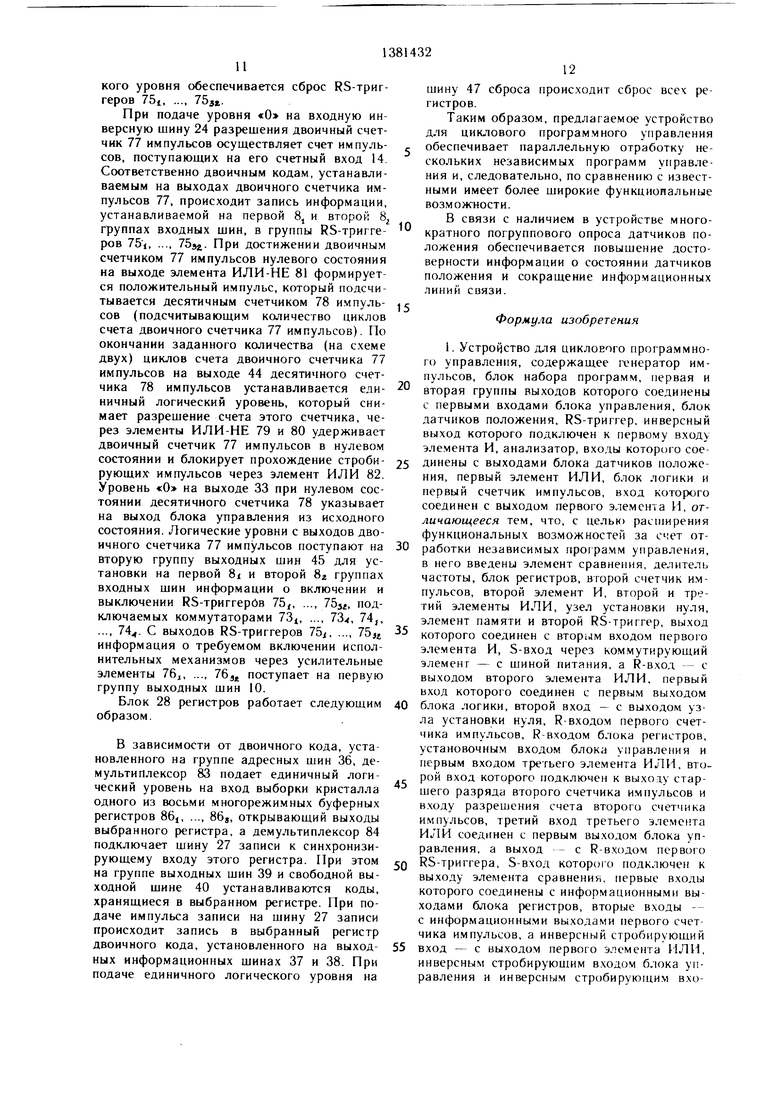

На фиг. 1 и 2 приведена функциональная схема устройства для циклового программного управления (на восемь параллельных программ по шестнадцать шагов каждая); на фиг. 3 - схема анализатора; на фиг. 4 - схема узла режимов анализатора; на фиг. 5 - схема узла несовпадения анализатора; на фиг. 6 - схема блока управления; на фиг. 7схема блока регистров; на

фиг. 8 временная диаграмма выделения строба.

Устройство для циклового программного управления содержит элемент 1 сравнения, выход равенства которого соединен с входом установки первого RS-триггера 2, инверсный выход 3 которого соединен с первым входом первого элемента И 4. Выход первого элемента И 4 соединен с входом разрешения счега двоичного счетчика 5 импульсов, выходы 6 которого соединены с первой группой адресных входов блока 7 набора программ, первая 81И вторая 8 группы выходов которого соединены с соответ- ствуюшими группами входом блока 9 управления. Первая группа выходов 10 блока 9 управления соединена с объектом 11 управления. Генератор 12 импульсов соединен с входом делителя 13 частоты, первый выход 14 которого соединен со счетным входом двоичного счетчика 5 импульсов. Блок 15 датчиков положения выходами 16 соединен с информационными входами анализатора 17. Инверсный выход 3 первого триггера 2 соединен с инверсным входом разрешения анализатора 17, первый 18j, второй 18 и третий 18 выходы которою соединены с соответствующими входами блока 19 логики, первый выход 20 которого соединен с адресным входом элемента 21 памяти, второй выход 22 - с первым входом первого элемента ИЛИ 23, третий выход 24 - с инверсным входом разреи1ения блока 9 управления, а четвертый выход 25 - с входом сброса десятичного счетчика 26 и.мпульсов. Счетный вход десятичного счетчика 26 импульсов соединен с первым выходом 14 делителя 13 частоты, свободными входами анализатора 17 и блока 9 управления, выход 27 младшего разряда - с входом записи блока 28 регистров, выход 29 старшего разряда - с его входом разрешения счета и первым входом второго элемента ИЛИ 30, а нулевой выход - с первым входом второго элемента И 31. Второй вход второго элемента И 31 соединен с четвертым выходом 32 анализатора 17, третий вход соединен с первым вы0

5

0

5

0

5

0

5

0

5

ходом 33 блока 9 управления, а выход 34 соединен с вторым входом первого элемента И 4. Группа выходов 6 двоичного счетчика 5 импульсов соединена с группой адресных входов элемента 21 памяти и адресными входами анализатора 17, выходы 35 младших разрядов этой группы соединены с первой группой входов элемента 1 сравнения, а выходы 36 старших разрядов этой группы соединены с группой адресных входов блока 28 регистров. Информационные входы 37 и 38 блока 28 регистров соединены с соответствующими выходами 37 и 38 элемента 21 памяти, группа выходов 39 - с второй группой входов элемента I сравнения, свободный выход 40 - с четвертым входом блока 19 логики. Первый 14 и второй 41 выходы делителя 13 частоты через третий элемент ИЛИ 42 соединены с инверсными стробирующими входами 43 анализатора 17, элемента 1 сравнения и блока 9 управления. Второй выход 44 блока 9 управления соединен с вторым входом второго элемента ИЛИ 30, а вторая группа выходов 45 - с второй группой адресных входов блока 7 набора программ. Узел 46 установки нуля соединен с входами 47 сброса блока 28 регистров и двоичного счетчика 5 импульсов, входом установки нуля блока 9 управления, вторым входом первого элемента ИЛИ 23 и третьим входом второго элемента ИЛИ 30, выход которого соединен с входом сброса первого RS-триггера 2. Выход первого элемента ИЛИ 23 соединен с входом сброса второго RS-триггера 48, вход установки которого соединен через коммутирующий элемент 49 с шиной 50 питания. Выход второго RS-триггера 48 соединен с третьим входом первого элемента И 4.

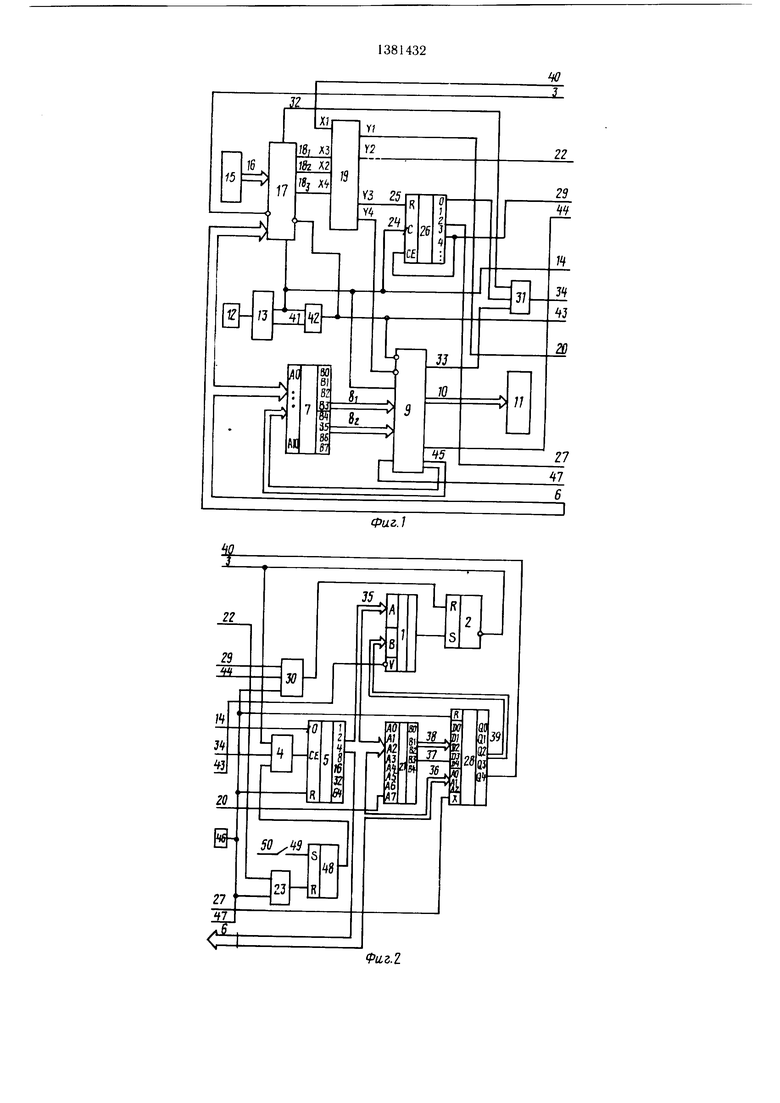

Анализатор 17 содержит узел 51 режимов, группа выходных шин 52 которого соединена с первой группой адресных входов элемента 53 памяти и адресными входами коммутатора 54, информационные входы которого соединены с информационными шинами 16, а выходы 55 -- с первыми группами входов первого 56 и второго 57 узлов несовпадения, вторые группы входов 58 и 59 которых соединены с соответствующими группами выходов элемента 53 памяти, вторая группа адресных входов которого соединена с адресными шинами 6. Выходы 60 и 61 первого 56 и второго 57 узлов несовпадения соединены с соответствующими первым и вторым входами узла 51 режимов, третий инверсный вход которого соединен с шиной 3 разрешения, четвертый вход - со свободной входной шиной 14, а четыре выхода - с выходными шинами IS,, IB, 18д и 32. Инверсные стробирующие входы первого 56 и второго 57 узлов несовпадения соединены с шиной 43 стробирования.

Узел 51 режимов содержит двоичный счетчик 62 импульсов, счетный вход которого соединен со свободной входной шиной 14, а выходы соединены с группой выходных шин 52 и входами первого элемента ИЛИ- НЕ 63, выход которого соединен со счетными входами первого 64 и второго 65 десятичных счетчиков импульсов и с входом установки RS-триггера 66. Инверсный выход RS-триггера 66 соединен со счетным входом третьего десятичного счетчика 67 импульсов. Один из выходов второго 65 и третьего 67 десятичных счетчиков импульсов соединены с их входами разрешения и первой 18 и второй 18 выходными шинами. Нулевой выход первого десятичного счетчика 64 импульсов соединен с четвертой выходной шиной 32, а один из его свободных выходов соединен с третьей выходной шиной IBj, его входом разрешения и первым входом первого элемента ИЛИ 68, выход которого соединен с входом сброса двоичного счетчика 62 импульсов. Первый вход второго элемента ИЛИ 69 соединен с первой входной шиной 60, а его выход соединен с входом сброса второго десятичного счетчика 65 импульсов. Вход сброса RS-триггера 66 соединен с второй входной шиной 61. Входная шина 3 разрешения соединена с вторыми входами первого 68 и второго 69 элементов ИЛИ и входами сброса первого 64 и третьего 67 десятичных счетчиков импульсов.

Узел 56 несовпадения содержит элементы ИЛИ-НЕ 70i, ..., 704, 71 и 72, первую 55 и вторую 58 группы входных шин, инверсную стробирующую шину 43 и выходную шину 60.

Блок 9 управления содержит коммути- руюшие элементы 73i, ..., 7l«, 74i, ..., 744, RS-триггеры 75, ..., 75, усилительные элементы 76i, ..., 76ja, двоичный счетчик 77 импульсов, десятичный счетчик 78 импульсов, элементы ИЛИ-НЕ 79-81, элемент ИЛИ 82, первую 8i и вторую 8 группы входных шин, инверсную стробируюшую шину 43, входную шину 47 установки нуля, входную инверсную шину 24 разрешения и свободную входную шину 14, а также первую 10 и вторую 45 группы выходных шин, первую 33 и вторую 44 выходные шины.

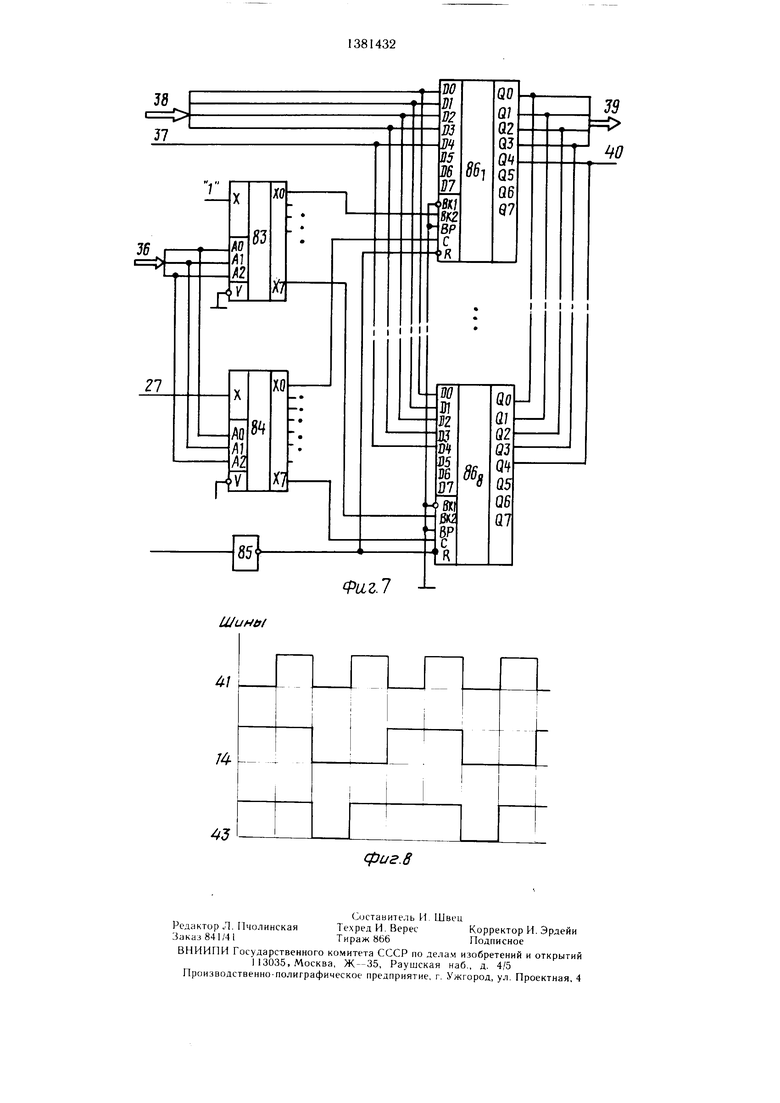

Блок 28 регистров содержит демульти- плексоры 83 и 84, инвертор 85, многорежимные буферные регистры 86/, ..., 86/, группу адресных шин 36, информационные шины 37 и 38, шину 47 сброса, шину 27 записи, группу выходных шин 39 и выходную шину 40.

Устройство для циклового программного управления работает следующим образом.

При подаче питающего напряжения узел 46 установки нуля кратковременной подачей единичного логического уровня по шине 47 ориентирует в нулевое состояние двоичный счетчик 5 импульсов (при этом на шинах

5

первой группы выходов 8 элемента 7 памяти устанавливаются нулевые логические уровни, а на шинах второй группы выходов Вг - единичные логические уровни), блок 9 управления и блок 28 регистров, а также через первый 23 и второй 30 элементы ИЛИ - второй 48 и первый 2 RS-триггеры соответственно. Единичный логический уровень с инверсного выхода первого RS-триггера 2 по шине 3 удерживает анализатор 17 в исходном состоянии, при этом на первой 18(, второй третьей 18 шинах установлены уровни «О, а уровень «1 на четвертой выходной шине 25 блока 19 логики устанавливает десятичный счетчик 26 импульсов в 5 левое состояние.

Блок 19 логики реализует следующие логические функции;

YI X1JX2-X3-X4;

Y2 (Х2-ХЗ + Х1-Х2-.;ГЗ + XJ-X2-X3)-X4; г.Y3 (Х2-ХЗ +Х1 Х2 ХЗ)-Х4;

Y4 Х1-Х2-%3-Х4,

где , XI - логический уровень на четвертом входе 40 блока 19 логики; Х2,ХЗ, Х4 - логические уровни соответственно на первом 18i, втором 182 и третьем 18 входах блока 19 логики;

Y1 - логический уровень на четвертом выходе 20 блока 19 логики; Y2 - логический уровень на втором Qвыходе 22 блока 19 логики;

Y3 - логический уровень на четвертом выходе 25 блока 19 логики;Y4 - логический уровень на третьем

выходе 24 блока 19 логики.

5 При кратковременном замыкании коммутирующего элемента 49 единичный логический уровень с шины 50 питания поступает на вход установки второго RS-триггера 48. Так как на выходе второго элемента И 31 установлен единичный логический уровень, то с выхода первого элемента И 4 на вход разрешения счета двоичного счетчика 5 импульсов поступает уровень «1. На вход делителя 13 частоты поступают импульсы с генератора 12 импульсов. На выходах 14 и 41 5 делителя 13 частоты вырабатываются последовательности импульсов согласно фиг. 8. На выходе элемента ИЛИ 42 вырабатывается последовательность стробирующих импульсов с уровнем «О (фиг. 8).

0 Четырьмя младшими разрядами двоичного счетчика 5 импульсов формируются коды шестнадцати шагов программ, а тремя старшими разрядами - коды номеров программ.

5

В элементе 21 памяти для каждого шага каждой программы с учетом выполнения условия перехода (логический уровень, поступающий по шине 20) записан код следующего шага (выходы 38) и его признак перехода (выход 37, на котором уровень «1 указывает на наличие условного перехода, а уровень «О - на наличие безусловного перехода).

В зависимости от логических уровней трех старших разрядов двоичного счетчика 5 импульсов к информационным входам 37 и 38, группе выходов 39 и свободному выходу 40 блока 28 регистров подключается один из его восьми регистров, в которых содержатся коды и признаки отрабатываемых шагов каждой из программ.

Двоичный счетчик 5 импульсов при поступлении единичного .логического уровня на его вход разрешения обеспечивает счет импульсов, поступающих на его счетный вход 14. С выходов двоичного счетчика 5 импульсов код шага поступает на группу входов 35 элемента I сравнения, а на его группу входов 39 поступает код шага с регистра блока 28 регистров, включенного в соответствии с кодом программы, поступаю- шим со -старших разрядов двоичного счетчика 5 импульсов на группу адресных вхо дов 36. При совпадении кодов на группах входов 35 и 39 элемента 1 сравнения по приходу стробирующего импульса на его инверсный стробируюш.ий вход 43 единичный логический уровень с его выхода устанавливает RS-триггер 2. При этом нулевой логический уровень с инверсного выхода 3 RS- триггера 2 снимает разрешение счета двоичного счетчика 5 импульсов и поступает на инверсный вход 3 разрешения анализатора 17. Анализатор 17 обеспечивает выдачу управляющих сигналов на первую 18i, вторую 18;j и третью 18,, шины по итогам сравнения состояния блока 15 датчиков положения с требуемым состоянием этого блока, хранимым в памяти анализатора 17, на каждом шаге каждой программы, код которой поступает на адресные входы 6 анализатора 17. Для обеспечения анализа и синхронизации работы анализатора 17 на его свободный вход 14 и инверсный стробирую- щий вход 43 поступают импульсные последовательности в соответствии с фиг. 8.

Уровень «1 на первом выходе 18 анализатора 17 устанавливается при совпадении состояния блока 15 датчиков положения 15 с хранимым в памяти анализатора 17 состоянием этого блока, определяющим окончание отработки текущей команды, на втором выходе 18;j - при несовпадении состояния блока 15 датчиков положения с хранимым в памяти анализатора 17 состоянием этого блока, определяющим блокировку, а на третьем выходе 18j - по окончании работы анализатора 17. Уровень «О устанавливаемый на четвертом выходе 32 анализатора 17 при выходе его из исходного состояния, подтверждает запрет счета двоичного счетчика импульсов 5.

Уровень «О, поступающий с выхода 24 блока 19 логики на инверсный вход разре- щения блока 9 управления, разрешает работу последнего. При этом на первом выходе 33 блока 9 управления устанавливается уровень «О, подтверждающий запрет счета двоичного счетчика 5 импульсов, а на

Q группе выходов 45 устанавливается двоичный код, поступающий на группу адресных входов блока 7 набора программ и последовательно изменяющийся по переднему фронту импульсов, поступающих на его вход 14. Блок 7 набора программ устанавливает информацию о включении (первая группа выходов 8j) и выключении (вторая группа выходов 8) исполнительных механизмов объекта 11 управления на шаге программы, двоичный, код которого поступает на группу

Q адресных входов 6 в соответствии с изменением двоичного кода, поступающего на группу адресных входов 45. Блок 9 управления в соответствии с поступающей на его первую 8 и вторую 8 группы входов информацией через группу выходов 10 обеспечивает включе5 ние и выключение исполнительных механизмов объекта 11 управления. По окончании работы блока 9 управления на его выходе 44 устанавливается уровень «1, который через элемент ИЛИ 30 сбрасывает первый RS-триггер 2. Для синхронизации работы

блока 9 управления на его инверсный стро- бирующий вход 43 поступает последовательность импульсов в соответствии с фиг. 8. Уровень «О, поступаюший с выхода 25 блока 19 логики на вход сброса десятичного

счетчика импульсов 26, разрешает счет импульсов, поступающих на его счетный вход 14. При этом по переднему фронту импульса на нулевом выходе десятичного счетчика 26 импульсов устанавливается уровень «О, подтверждающий запрет счета двоичного счет0 чика 5 импульсов. При пересчете десятичным счетчиком 26 импульсов трех импульсов уровень «1 с его выхода 27 младшего разряда вызывает запись поступающих с элемента 21 памяти кода следующего шага и

5 его признака перехода в регистр программы, включенный в соответствии с кодом программы, поступающим на группу адресных входов 36 блока 28 регистров, а при пересчете четвертого импульса уровень выхода 29 старшего разряда снимает разрешение сче0 та десятичного счетчика 26 импульсов и через элемент ИЛИ 30 сбрасывает первый RS-триггер 2. Одновременно с уровнем «О на четвертом выходе 25 блока 19 логики, при невыполнении проверяемого анализатором 17 условия и наличии уровня «1 на четвертом входе 40 блока 19 логики на его выходе 20 устанавливается уровень «1, который поступает на адресный вход элемента

21 памяти и устанавливает на его выходах 37 и 38 признак перехода и код следующего шага.

Уровень «1 на выходе 22 блока 19 логики через элемент ИЛИ 23 сбрасывает RS-трнггер 48.

При сбросе RS-триггера 2 уровень «1 с его инверсного выхода 3 подготавливает разрешение счета двоичного счетчика 5 импульсов и устанавливает в исходное состояние анализатор 17. При этом на выходе 32 анализатора 17 устанавливается уровень «1, а на его первом 18х., втором 18 и третьем 18 выходах уровни «0. Уровень «О, поступаю- ш,ий на третий вход 18j блока 19 логики, устанавливает на его выходах 20 и 22 уровни «О, а на выходах 24 и 25 - уровни «I. Уровень «1 с выходов 24 и 25 блока 19 логики переводит в исходное состояние блок 9 управления и сбрасывает десятичный счетчик 26 импульсов. При этом уровни «1 поступаю- щие с четвертого выхода 32 анализатора 17, нулевого выхода десятичного счетчика 26 импульсов и выхода 33 блока 9 управления на входы элемента И 31, разрешают счет двоичного счетчика 5 импульсов.

При увеличении на единицу кода стар- ших разрядов двоичного счетчика 5 импульсов (кода программы) к входам и выходам блока 28 регистров подключается регистр следующей программы и при равенстве кода младших разрядов двоичного счетчика 5 импульсов и кода шага, записанного в регистр программы блока 28 регистров, двоичный счетчик 5 импульсов останавливается н производится отработка шага следующей программы.

При сбросе RS-триггера 48 уровень «О с его выхода снимает разрешение счета двоичного счетчика 5 импульсов.

Таким образом, при установке RS-триггера 48 двоичный счетчик 5 импульсов обеспечивает поиск текущего шага ближайшей программы, записанного в блоке 28 регист- ров. При этом устанавливается RS-триггер 2, который фиксирует двоичный счетчик 5 импульсов на текущем шаге и включает анализатор 17. Анализатор 17 определяет совпадение состояния датчиков блока датчиков положения 15 с требуемыми их состояниями на данном шаге. По результатам работы анализатора 17 и с учетом признака перехода (условный или безусловный переход), поступающего с блока 28 регистров, блок 19 логики обеспечивает:

- при наличии безусловного перехода, отсутствии блокировок и неподтверждении отработки команды включение блока 9 управления, который обеспечивает включение и выключение исполнительных механизмов объекта 11 управления в соответствии с информацией блока 7 набора программ на текущем щаге;

s

Q 15 20

о

35

0

5

-при наличии безусловного перехода, отсутствии блокировок и подтверждении отработки команды запись кода следующего шага программы и признака перехода, хранимых в элементе 21 памяти, в блок 28 регистров;

-при наличии условного перехода запись кода следующего шага программы и признака перехода, хранимых в элементе 21 памяти, с учетом выполнения или невыполнения условия (логический уровень шины 20) в блок регистров 28;

-при наличии блокировок или запрещенных состояний (одновременное появление сигналов совпадения и несовпадения или их отсутствие при наличии условного перехода носле окончания работы анализатора) сброс RS-триггера 48.

По окончании работы блока управления 9 или записи в блок 28 регистров кода следующего Qiara и признака перехода обеспечивается сброс RS-триггера 2, который переводит в исходное состояние анализатор 17. При этом уровни «1 на выходах 24 и 25 блока 19 логики переводят в исходное состояние блок 9 управления и сбрасывают десятичный счетчик 26 импульсов, в результате чего поступает сигнал разрещения счета двоичного счетчика импульсов 5 и поиска текущего шага следующей программы, отработка которого происходит аналогично описанному и т. д., следовательно, отработка шагов каждой программы происходит последовательно во времени с большой частотой повторения.

Анализатор 17 работает следующим образом.

При поступлении уровня «О на вход узла 51 режимов двоичный код на группе выходных щин 52 последовательно изменяется по переднему фронту импульсов, юступаю- щих на его четвертый вход 14. На группах выходов 58 и 59 элемента 53 памяти на шаге программы, код которого поступает на его вторую группу адресных входов 6, согласно с изменением двоичного кода на первой группе адресных шин 52 устанавливается предварительно записанная информация о состоянии группы датчиков, вызывающем переход к следующему шагу программы (груп- ia выходных шин 58), и блокировках (группа выходных щин 59), а на выходах 55 коммутатора 54 устанавливается информация о текущем состоянии этой же группы датчиков, поступающая на его информационные выходы 16. При установке уровня «О на шине 43 стробирования первый 56 и второй 57 узлы несовпадения осуществляют опрос включенного состояния датчиков, заданных уровнями «О на группах выходных шин 58 и 59 (включенному состоянию датчика соответствует уровень «I на выходах 55 коммутатора 54). При включенном состоянии

хотя бы одного из датчиков, заданных уровнем «О на соответствующем выходе элемента 53 памяти, на выходах 60 и 61 первого 56 и второго 57 узлов несовпадения устанавливаются уровни «1, поступающие со- ответственно на входы узла 51 режимов, на первом 181, втором 182 и третьем 18j выходах которого устанавливается информация о результатах работы анализатора, а на его четвертом выходе 32 - о выходе анализатора из исходного состояния.

Узел 51 режимов работает следующим образом.

При поступлении уровня «0 на входную шину 3 разрешения двоичный счетчик 62 импульсов начинает счет импульсов, посту- пающих на его счетный вход 14. При достижении двоичным счетчиком импульсов 62 нулевого состояния на выходе элемента ИЛИ-НЕ 63 выделяется положительный импульс, который устанавливает триггер 66 и увеличивает на единицу состоянне первого 64 и второго 65 десятичных счетчиков импульсов.

Таким образом, первый 64 и второй 65 десятичные счетчики импульсов подсчитывают количество циклов пересчета двоично- го счетчика 62 импульсов.

После четырех циклов пересчета двоичного счетчика 62 импульсов на выходе 18 первого десятичного счетчика 64 импульсов и выходе 18i второго десятичного счетчика 65 импульсов устанавливаются уровни «1 которые блокируют дальиейший счет указанных счетчиков. Кроме того, уровень ixl с выхода 18з первого десятичного счетчика 64 импульсов удерживает в нулево.м состоянии двоичный счетчик 62 импульсов. Уровень «О на выходе 32 первого десятичного счетчика 64 импульсов при его ненулевом состоянии указывает на выход узла режимов из исходного состояния. При поступлении импульсов несовпадения иа первый вход 60 второго элемента ИЛИ 69 происходит сброс второго десятичного счетчика 65 импульсов, а при поступлении импульсов несовпадения на вход 61 сброса RS-триггера 66 на его инверсном выходе устанавливается единичный логический уровень, который сбрасывается при достижении двоичны.м счетчико.м 62 импульсов нулевого состояния. Третий десятичный счетчик 67 импульсов подсчитывает количество импульсов на инверсном выходе RS- триггера 66.

Следовательно, уровень «1 на третьей выходной шине 18,, устанавливается после четырех циклов пересчета двоичного счетчика 62 импульсов и указывает на окончание работы узла режимов. Уровень «1 на первой выходной шине I8i устанавливается при окончании работы анализатора и отсутствии импульсов несовпадения на первой входной шине 60 и указывает на окоичание отработ

0

5

0

0 5

ки шага программы, а уровень «1 на второй выходной шине 18 устанавливается при наличии хотя бы одного импульса несовпадения на второй входной шине 61 в каждом цик ле пересчета двоичного счетчика 62 импуЛь- сов и указывает на наличие блокировок. Логические уровни с выходов 52 двоичного счетчика 62 импульсов использую ся для переключения узлов анализатора 17.

Узел 56 несовпадения работает следующим образом.

Иа второй группе входов 58 элемента несовпадения уровнями «0 задаются датчики, включенное состояние которых проверяется, а на первой группе входов 55 устанавливаются логические уровни, соответствующие текущему состоянию этой же группы датчиков (включенному состоянию датчика соответствует уровень «1, а выключенному - «0). При выключенном состоянии датчика, заданного уровнем «О на одном из входов второй группы 58 элементов 70j, ..., 70, и нулевом логическом уровне на инверсной стробирующей шине 43 на выходной шине 60 устанавливается уровень «1. Узел 57 несовпадения идентичен узлу 56, при этом уровнями «0 задаются проверяемые датчики блокировок по второй группе входов 59, поступающих вместо второй группы входов 58, указанной на фиг. 5. Прохождение логических уровней по элементам ИЛИ-ИЕ 70, ..., 70, 71 и 72 видно на схеме фиг. 5.

Блок управления работает следующим обра.чом.

При подаче единк-ного логического уровня на входную шину 47 установки нуля двоичный счетчик 77 импульсов осушествляет счет импульсов, поступающих на его вход 14. В соответствии с кодом двоичного счетчика 77 импульсов коммутирующие элементы 73i, ..., 73 и 74t, ..., 74 подключают к первой 8i и второй 8г. группам входных шин R- и S-входы группы из четырех RS-тригге- ров 75j, ..., 75jg. Уровень «О на инверсной стробирующей шине 43 вызывает запись информации, установленной на первой 8 и второй 8г группах входных шин, в группу из чегырех RS-триггеров (сигналом установки нуля с выходов элемента 7 памяти на первую группу входных шии 8 устанавливаются уровни «О, а на вторую группу входных шин Bg - уровни «1.

При последующих изменениях состояния двоичного счетчика 77 импульсов происходит запись информации в последующие группы из четырех RS-триггеров 75, ..., 75. Десятичный счетчик 78 импульсов удерживается в нулевом состоянии единичным логическим уровнем, поступающим на входную инверсную шииу 24 разрешения.

Таким образом, при подаче на входную шину 47 установки нуля единичного логичесИ

кого уровня обеспечивается сброс RS-триг- геров 75i, ..., 75з.

При подаче уровня «О на входную инверсную шину 24 разрешения двоичный счетчик 77 импульсов осуш,ествляет счет импульсов, поступающих на его счетный вход 14. Соответственно двоичным кодам, устанавливаемым на выходах двоичного счетчика импульсов 77, происходит запись информации, устанавливаемой на первой 8 и второй 8 группах входных шин, в группы RS-тригге- ров 75 i, ..., 75э2. При достижении двоичным счетчиком 77 импульсов нулевого состояния на выходе элемента ИЛИ-НЕ 81 формируется положительный импульс, который подсчитывается десятичным счетчиком 78 импуль- сов (подсчитывающим количество циклов счета двоичного счетчика 77 импульсов). По окончании заданного количества (на схеме двух) циклов счета двоичного счетчика 77 импульсов на выходе 44 десятичного счетчика 78 импульсов устанавливается еди- ничный логический уровень, который снимает разрешение счета этого счетчика, через элементы ИЛИ-НЕ 79 и 80 удерживает двоичный счетчик 77 импульсов в нулевом состоянии и блокирует прохождение строби- рующих импульсов через элемент ИЛИ 82. Уровень «О на выходе 33 при нулевом состоянии десятичного счетчика 78 указывает на выход блока управления из исходного состояния. Логические уровни с выходов двоичного счетчика 77 импульсов поступают на вторую группу выходных шин 45 для установки на первой 8i и второй 8 группах входных щин информации о включении и выключении RS-триггерйв 75, ..., 75зг, подключаемых коммутаторами 73, ..., 73х, 74,,

..., 74. С выходов RS-трнггеров 75/ 75

информация о требуемом включении исполнительных механизмов через усилительные

элементы 76, поступает на первую

группу выходных шин 10.

Блок 28 регистров работает следующим образом.

В зависимости от двоичного кода, установленного на группе адресных шин 36, де- мультиплексор 83 подает единичный логический уровень на вход выборки кристалла одного из восьми многорежимных буферных регистров 86i, ..., 86j, открывающий выходы выбранного регистра, а демультиплексор 84 подключает шину 27 записи к синхронизирующему входу этого регистра. При этом на группе выходных шин 39 и свободной выходной шине 40 устанавливаются коды, хранящиеся в выбранном регистре. При подаче импульса записи на шину 27 записи происходит запись в выбранный регистр двоичного кода, установленного на выход- ных информационных шинах 37 и 38. При подаче единичного логического уровня на

12

шину 47 сброса происходит сброс всех регистров.

Таким образом, предлагаемое устройство для цик ювого программного управления обеспечивает параллельную отработку нескольких независимых программ управления и, следовательно, по сравнению с известными имеет более широкие функциональные возможности.

В связи с наличием в устройстве многократного погруппового опроса датчиков положения обеспечивается повышение достоверности информации о состоянии датчиков положения и сокращение информационных линий связи.

Формула изобретения

дом анализатора, информационные выходы которого соединены с первыми входами блока логики, второй вход которого соединен с выходом блока регистров, адресный выход блока логики подключен к адресному входу блока памяти, информационные выходы которого соединены с входами блока регистров, соединенного адресными входами с выходами первого счетчика импульсов, вход записи блока регистров соединен с выходом младшего разряда второго счетчика импульсов, нулевой выход которого подключен к первому входу второго элемента И, второй вход которого соединен с выходом анализатора, третий вход - с вторым выходом блока управления, а выход - с третьим входом пер- вого элемента И, выход генератора импульсов соединен с входом делителя частоты, первый выход которого подключен к первому входу первого элемента ИЛИ, второй выход - к входу анализатора, счетным входам первого и второго счетчиков импульсов, второму входу блока управления, вход сброса второго счетчика импульсов соединен с третьим выходом блока логики, четвертый выход которого соединен с входом разрешения блока управления, первая группа выхо- дов которого соединена с первой группой адресных входов блока набора программ, вторая группа адресных входов которого подключена к выходам первого счетчика импульсов и к адресным входам анализатора, инверсный вход которого соединен с инверс- ным выходом первого триггера.

0 5 0

5 0

ми выходов элемента памяти, вторая группа адресных входов элемента памяти соединена с адресными шинами анализатора, выходы первого и второго узлов несовпадения соединены соответственно с первым и вторым входами узла режимов, третий инверсный вход которого соединен с шиной разрешения, четвертый вход - с входной шиной, а вторые выходы - с выходными шинами анализатора, инверсные стробирующие входы узлов несовпадения соединены с шиной стро- бирования.

фиг. 5

Фиг.б

Шинш

| Устройство для циклового программного управления манипулятором | 1976 |

|

SU595705A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для циклового программного управления | 1979 |

|

SU773573A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-03-15—Публикация

1986-11-28—Подача