Изобретение относится к импульсной техн;-п е.

Известен делитель частоты, содержащий рекуррентный регистр сдвига с дешифратором, последовательный регистр сдвига, переключатели, блок сброса и повторного запуска и вентили.

Цель изобретения - расшир1:ть диапазон изменения коэффициента деления, а тахже повысить надежность устройства.

Предлагаемый делитель частоты отличается тем, что вхсдь дополнительных с.хем «И соединены с выходами вентилей, соответствующих Выходам переключателя и дешифратора, а ьыходы дополнительных схем со вновь введе 1нь;м блоком ко)троля последователь1:ости операций, с которым связаны вторые входы всех вентилей и вход блока сброса и повторного запуска. Выходы схем «И объединены с выходами соответствующих блоков переноса, первые входы которых соединены с нулевым входом соответствующего переключателя, вторые - со входом последовательного регистра сдвига, а выходы вентилей дещифраiopa гюдключсны к блоку сброса и повторного запуска.

Кровле этого, нулевой выход дещифратора и выходы последовательного регистра сдвига подключены к запрещающим входам блока сброса и повторного запуска.

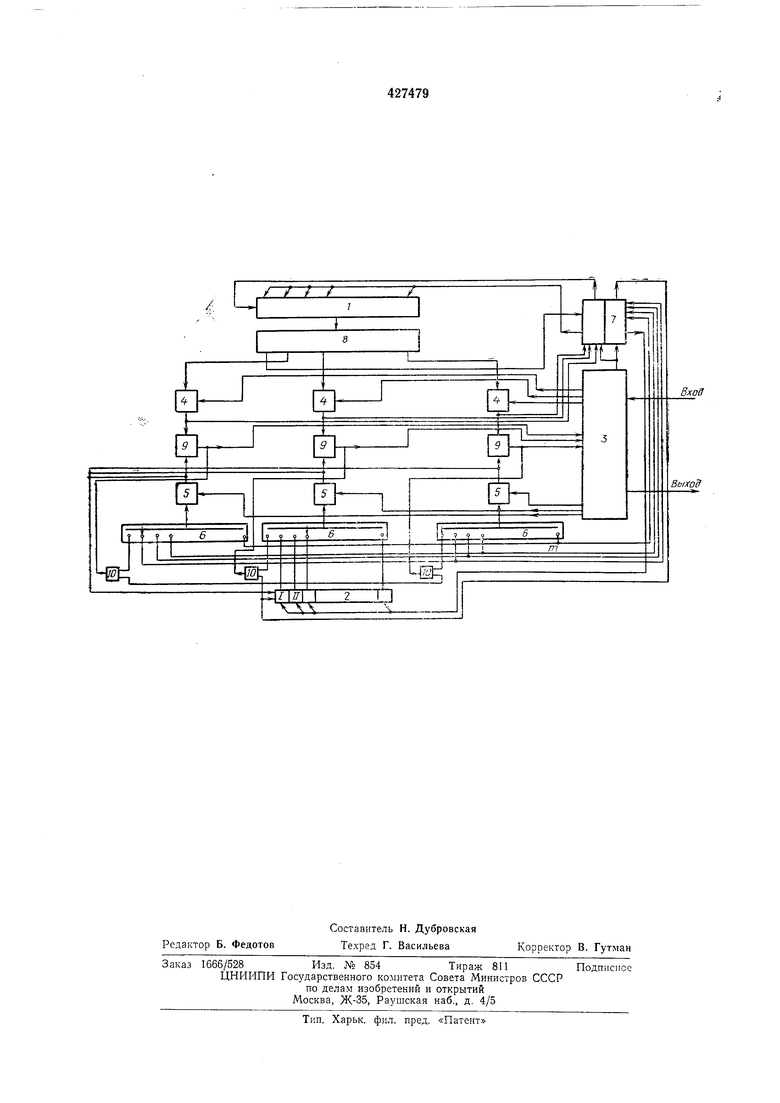

На чертеже приведена схема устройства.

В начальный момент времени рекуррентный

регистр сдвига / и последовательный регистр

сдвига 2 находятся в нулевых состояниях.

Блок контроля последовательности операций 3

возбуждает вентили 4 н 5 младшего разряда

делителя (левые по схеме). Таким образом,

регистр 2 замкнут в кольцевую схему с коэффицкентсм пересчета, равным номеру входа

(па схеме - положенгю «единица), на котором находится подвижный контакт переключателя 6 младшего разряда.

При поступлении на вход первого из импульсов, частота которых подлежит делению,

блок контроля 3 разрещает работу блока сброса и повторного запуска 7. Он в свою очередь пропускает единичный импульс на входы регистров сдвига / и 2. Далее входные импульсы, частота которых используется как тактовая

для всего устройства, продвигают записанную в регистры информацию по их ячейкам. Па выходе дещифратора 8 через число импу.-гьсов I, частота которых подлежит делению, появляется выходной импульс, проходящий на

вход соответствующей схемы «И 9. При установке переключателя 6 младшего разряда в единицу импульсы на входах схемы «И этого раЗ;1)яда совпадут черел /X/ и.пульсов на входе устройства, где / - коэффициент делеНИИ регистра / для младщего разряда; 1-коэффициент деления регистра 2 в этом же разряде. При установке переключателя 6 в любое положение (кроме нуля и единицы) импульс с дешифратора 8 (с коэффициентом деления /) проходит через возбужденный вентиль 4 на блок 7, вызывая сброс и повторный запуск только регистра /. Поэтому в общем случае импульсы на входах схемы «И совпадают через /X импульсов на входе всего устройства, где г - номер входа переключателя 6 данного разряда, на котором находится его подвижный контакт. Схема «И выдает импульс на блок 5, который отключает вентили 4 и 5 младшего разряда, с помощью блока 7 одновременно сбрасывает в нулевое состояние регистры / и 2, а также возбуждает вентили 4 5 следующего разряда делителя. Затем блок 7 подает на входы регистров 1 и 2 единичные импульсы запуска. В изображенном на чертеже положении схема «И следующего разряда срабатывает через рХЗ входных импульсов, где р - коэффициент, деления этого разряда регистра /; 3 - коэффициент деления регистра 2 в этом разряде. Импульс схемы «И 9 проходит на блок 3 и выполняет описанные выше операции, возбуждая следующую пару вентилей 4 и 5 и т. д. В случае установки очередного переключателя 6 в положение «нуль .возбуждается блок переноса 10 этого разряда, а его выход подключается непосредственно « выходу соответствующей схемы «И. В результате этого коэффициент деления устройства сдвигается на один разряд. Импульс с выхода схемы «И 9 старшего разряда (правый по схеме) поступает через блок 3 на выход всего устройства, одновременно подготавливая все его элементы н блоки к очередному циклу. Таким образом, общий коэффициент деления К делителя равен сумме коэффициентов деления всех разрядов, каждый из которых в свою очередь равен произведению коэффициентов деления регистров 1 т 2. При этом он лежит в пределах 1 X I К т X g, где т и g - соответствующие максимальные коэффициенты деления регистров 2 и 1. Предмет изобретения 1. Делитель частоты, содержащий рекуррентный регистр сдвига с дешифратором, последовательный регистр сдвига, переключатели, блок сброса и повторного запуска и вентили, причем выходы последовательного регистра сдвига соединены с одноименными входами переключателей, выход каждого переключателя соединен со входом своего вентиля и каждый выход дешифратора соединен со входом своего вентиля, отличающийся тем, что, с целью расширения диапазона изменения коэффициента деления, входы дополнительных схем «И соединены с выходами вентилей, соответствующих выходам переключателя и дешифратора, а выходы дополнительных схем «И - со вновь введенным блоком контроля последовательности операций, с которым связаны вторые входы всех вентилей и вход блока сброса и повторного запуска, выходы схем «И объединены с выходами соответствующих блоков переноса, первые входы которых соединены с нулевым входом соответствующего переключателя, вторые - со входом последовательного регистра сдвига, а выходы вентилей дещифратора подключены к блоку сброса и повторного запуска. 2. Делитель по п. 1, отличающийся тем, что, с целью повышения надежности, нулевой выход дешифратора и выходы последовательного регистра сдвига подключены к запрещающим входам блока сброса и повторного запуска. I 2 ri

| название | год | авторы | номер документа |

|---|---|---|---|

| Десятичный счетчик импульсов | 1973 |

|

SU443486A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU613504A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1970 |

|

SU278761A1 |

| Адаптивный цифровой частометр с нормированием динамической погрешности | 1972 |

|

SU447636A1 |

| Устройство для коррекции шкалы времени | 1991 |

|

SU1781669A1 |

| Генераторное устройство с искробезопасным выходом | 1986 |

|

SU1425352A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Генератор случайных процессов | 1979 |

|

SU849464A2 |

| Генератор псевдослучайных последовательностей | 1979 |

|

SU877533A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

Авторы

Даты

1974-05-05—Публикация

1972-10-31—Подача