1

Изобретение относится к имиульсиой технике и может найти широкое примеиение в устройствах вычислительной техники при построении синтезаторов частоты и блоков опорной частоты.

Известен делитель частоты с переменным коэффициентом деления, содержащий рекуррентный регистр сдвига, дешифратор состояний этого регистра, последовательный регистр сдвига, 2/г вентилей, п элементов И, п переключателей на т положений каждый и л блоков переноса (где я - число разрядов делителя, а т-число разрядов последовательного регистра сдвига), блок контроля последовательности операций и блок сброса и повторного заиуска 1.

Однако в таком устройстве частое принудительное обиуленне и новторный зануск регистров ограничивают быстродействие схемы.

Кроме того, применение двух регистров и управление их работой (блок сброса и повторного запуска и блок контроля последовательности операций) и применение дешифратора, раснлифровываюш;его л состояний, усложняют это устройство.

Наиболее близким по технической сущности является делитель с переменным коэффициентом деления, содержащий регистр и переключатели, входы которых соединены с источником напряжения, а выходы с потенциальными входами элементов И, импульсные входы которых объединены и связаны со входом делителя, а выходы их поразрядно нодсоединены к установочным входам триггеров регистра, выход которого в свою очередь через элемент задержки и блок управления подключен к другим установочным входам триггеров регистра 2. Быстродействие схемы этого устройства

также ограничено, что связано, во-первых, с прнменением элемента задержкн, во-вторых, с тем, что в делителе ио каждому импульсу входной частоты происходит суммирование ноказаний «-разрядного регистра с л-разрядным двоичным кодом, имеющимся на выходах элементов И, и по каждому импульсу выходной частоты происходит дополнительное суммирование показаний регистра с заранее выбранным л-разрядным двоичным кодом. Таким образом, быстродействие делителя определяется суммой задержек импу.тьса в 2л разрядах регистра и в элементе задержки. Такое устройство сложно по конструкции, что связано с примененнем регистра, выиолняющего функцию «-разрядного сумматора.

Целью изобретения является увеличение быстродействия и повышение надежности работы устройства. Для этого в делитель частоты с переменным коэффициентом делення, содержащий

регистр и переключатели, входы которых подключеиы к шинам единичного и нулевого уровня, введены блок начальной установки и разрешения счета и дешифратор, одни входы которого соединены с выходами разрядов регнстра, другие входы - с выходами нереключателей, а выход - с элементом обратной связн регистра, установочные и тактовые входы разрядов которого нодключены к выходам блока начальной установки и разрешения счета, один из входов которого подключен к входной шине, а другне входы соединены с выходами переключателей.

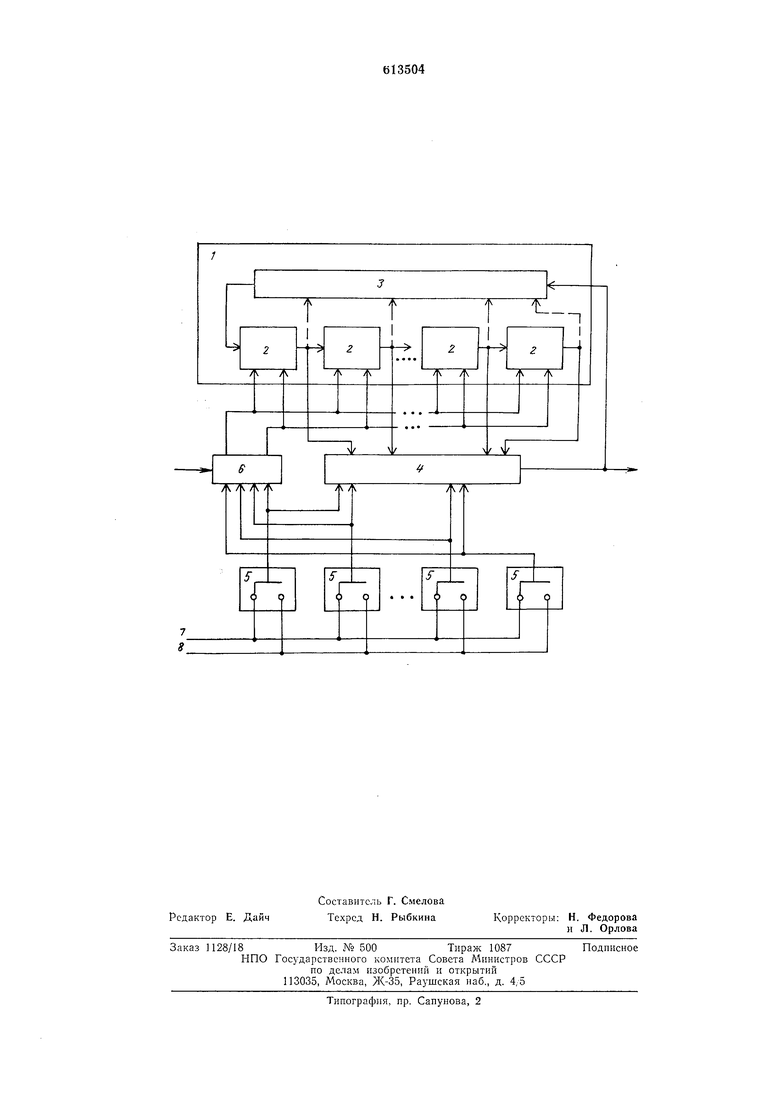

На чертеже изображена структурная электрическая схема делителя частоты с переменным коэффнцнентом.

Устройство состонт из регистра 1, в состав которого входит п разрядов 2 и элемент 3 обратной связи, дешифратора 4, п переключателей 5 и блока 6 начальной установки и разрешеиия счета.

Каждый переключатель 5 нмеет два положения. Первые входы нереключателей 5 подсоединены к шинам 7 единичного уровня, вторые - к шинам 8 нулевого уровня. В зависимости от положения переключателя 5 на выходе его можно нолучнть либо еднинчный, либо нулевой уровень. На выходах переключателей 5 в зависимости от их положений мол1но получать любой л-разрядный двоичный параллельный код.

В устройстве используется рекуррентный регнстр сдвига, который с тактовым импульсом, поступаюшим на него, изменяет свое состояние, начиная с начального, в онределенпой последовательности, определяемой элементом 3 обратной связи и выбором соединеннй этого элемента с разрядами 2 регнстра 1. Через некоторое число тактов, ностуннвших на регистр 1, последний вновь припимает свое начальное состоянне, носле чего цикл изменения состояний регистра 1 повторяется. Число тактов одного цикла зависит от ностроення рекуррентного регнстра 1, но не более 2, так как регнстр 1 максимально может нрниять 2 состояний.

Неред началом работы делителя нереключатели 5 нереводятся в положения, соответствующие устанавлнваемому коэффициенту деления. Двоичный параллельный код с выходов переключателей 5 через блок б записывается Б разряды 2 регистра 1 и подается на дешифратор 4. Носле этого блок 6 начинает пропускать на тактовые входы регистра 1 импульсы, ноступаюгцие на вход делителя, частота которых подлежит делению. Эти тактовые импульсы изменяют состоянне регистра

1но определенному циклу, зависяш,ему от построения этого регистра. Состояние разрядов

2регистра 1 контролируется дешифратором 4. В момент совиадення кода, находящегося в разрядах 2 регистра 1, с кодом, подаваемым на входы дешифратора 4 нереключателя1ми 5, на выходе дешифратора 4 возникает нмпульс совпадения. Нри иоступленни этого импульса па элемент обратной связи регистр 1 переходит в состояпие, отличное от того состояния, которое он должен принять в соответствнн со свонм циклом. Нри этом цикл изменений состояний регистра 1 укорачивается. Каждый раз носле нрохождения т тактовых импульсов регистр 1 нрнннмает свое начальное состоянне, совнадающее с кодом на выходах переключателей 5, и на выходе дешифратора 4, одновременно являющимся выходом всего устройства, выделяется нмпульс совпадення. Таким образом, на выходе устройства ноявляются импульсы с частотой в т раз меньшей частоты следования нмнульсов на входе устройства. Меняя ноложенне переключателей 5, можно получить любое число тактовых импульсов, осуществляющих один цикл нзменення состояний регистра 1, в пределах от 1 до 2.

1ем самым можно нолучить любой коэффициент деления частоты в пределах от 1 до 2.

Форм у л а н 3 -О б р с т е а и я

Делитель частоты с перемепным коэффициентом деления, содержащий регистр и переключатели, входы которых подключепы к шннам единичного и нулевого уровня, отличающийся тем, что, с целью увеличения быстродействия и новышения надежности работы устройства, в него введены блок начальной установкн и разрешення счета н дешифратор, одни входы которого соединены с выходами разрядов регистра, другие входы - с выходами переключателей, а выход - с элементом обратной связи регистра, установочные и тактовые входы разрядов которого иодключены к выходам блока начальной установкн и разрешения счета, один из входов которого нодключен к входной шине, а другне входы соедннены с выходами переключателей.

Источники информации, принятые во вниманне при экспертизе

1.Авторское свидетельство СССР №427479, кл. Н ОЗК 23/00, 1974.

2.Авторское свидетельство СССР Ла 334643, кл. Н ОЗК 23/02, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1979 |

|

SU877533A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1970 |

|

SU278761A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ /г-3,НАЧНОГО ДВОИЧНОГО КОДА В р-ЗНАЧНЫЙ ДВОИЧНЫЙ КОД | 1968 |

|

SU220630A1 |

| Устройство для передачи сигналов синхронизации | 1985 |

|

SU1241508A1 |

| Генератор последовательности чисел | 1983 |

|

SU1166089A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Генератор последовательностей чисел | 1982 |

|

SU1067490A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

Авторы

Даты

1978-06-30—Публикация

1976-11-04—Подача