1

Предлагаемое изобретение относится к пересчетным схемам, выполненным на ферритполупроводниковых элементах автоматики п электроники.

Известны десятичные счетчики импульсов с регулируемым коэффициентом пересчета, выполненные на основе последовательных регистров сдвига.

Однако известные счетчики сложны, так как каждый его десятичный разряд должен состоять из десяти ячеек, при этом такие последовательные схемы больплой длины имеют низкую помехозащищенность.

С целью повышения надежности устройства выходы дещифратора подключены к продвигающим обмоткам последовательного регистра и обмоткам гащения рекуррентного регистра через ячейки памяти, выход которых соединен через собственную линию задержки с ее входом, вход повторного запуска рекуррентного регистра соединен с его обмотками гашения через линию задержки, выход переключателя каждого старшего разряда через блок переноса соединен с входами записи ячейки памяти и блока переноса последующего младшего разряда, а через линию задержки - с пулевым входом переключателя последующего младшего разряда, выходы всех блоков переноса соединены непосредственно с обмотками гашения ячеек последовательного регистра и

через линию задержки - с входом записи его первой ячейки, а выход блока переноса низшего разряда подсоединен непосредственно к входу записи блока переноса первого старшего разряда, и через линию задержки - к нулевому входу переключателя этого разряда.

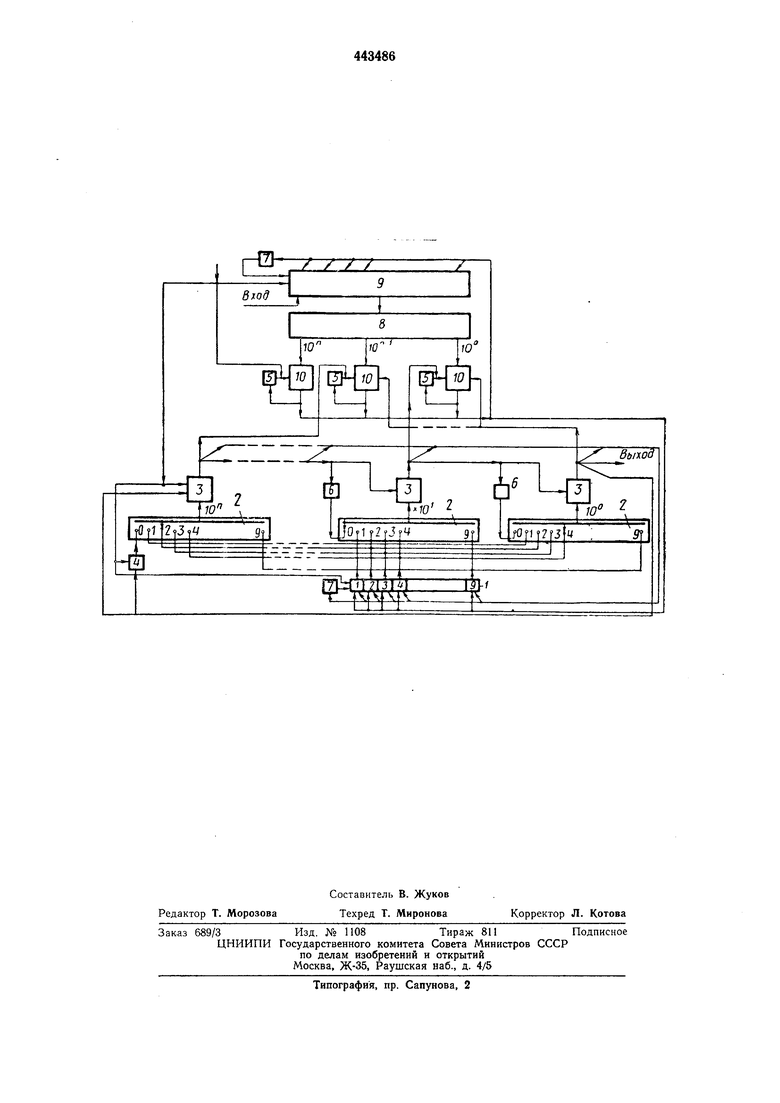

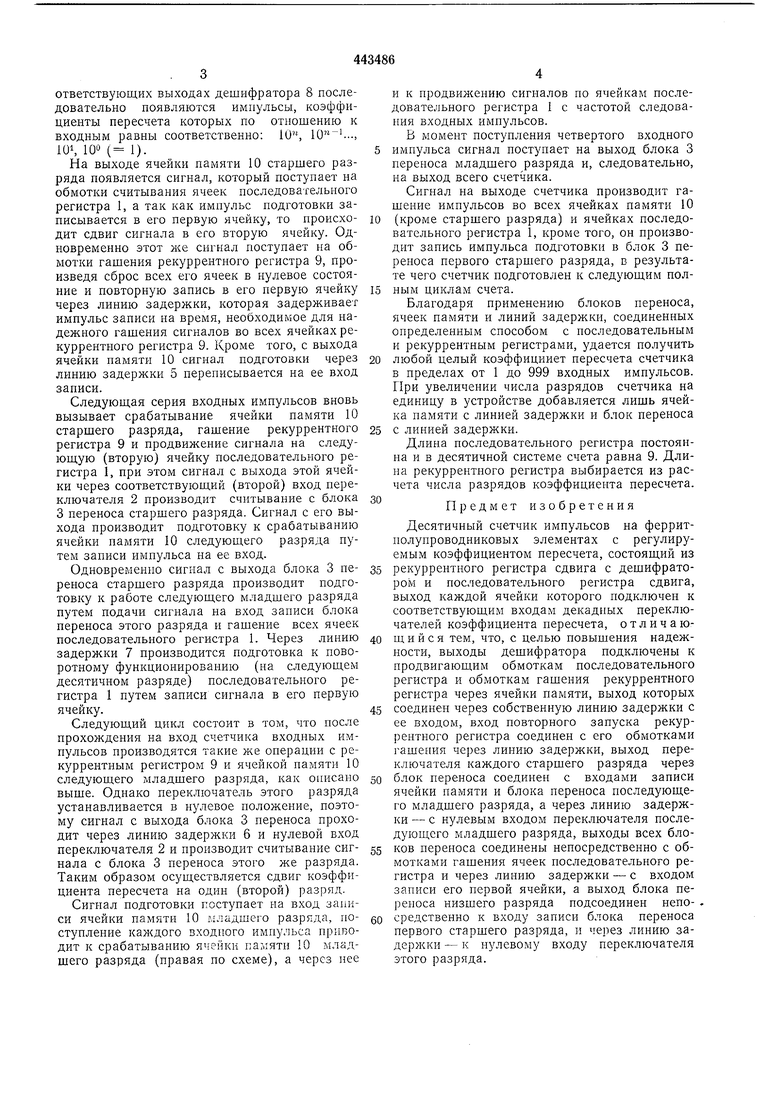

На чертеже показано предлагаемое устройство.

Десятичный счетчик имп -льсов содержит регистр 1 сдвига, переключатели 2 коэффициента пересчета, блок 3 переноса, линии задержки 4 - 7, дешифратор 8, рекуррентный регистр 9 и ячейки памяти 10.

Устройство работает следующим образом.

С помощью переключателей 2 устанавливается требуемый коэффициент пересчета в десятичном исчислении.

От отдельного устройства, не показанного па чертеже, производится подготовка счетчика к фупкционированию. Для этого, например, вручную с помощью кнопки одиночный импульс подготовки записывается в первые ячейки соответственно последовательного и рекуррентного регистров 1 и 9 сдвига, а также в блок 3 переноса и ячейку памяти 10 старшего (левого по схеме) разряда. Далее все операции пропзводятся автоматически.

Импульсы, подлежащие счету, подаются на вход счетчика в качестве считываемых на все ячейки рекуррентного регистра 9. На соответствующих выходах дешифратора 8 последовательно появляются импульсы, коэффициенты пересчета которых по отношению к входным равны соответственно: 10, ..., 10 100 ( 1).

На выходе ячейки памяти 10 старшего разряда появляется сигнал, который поступает на обмотки считывания ячеек последовательного регистра 1, а так как импульс подготовки записывается в его первую ячейку, то происходит сдвиг сигнала в его вторую ячейку. Одновременно этот же сигнал поступает на обмотки гашения рекуррентного регистра 9, произведя сброс всех его ячеек в нулевое состояние и повторную запись в его первую ячейку через линию задержки, которая задерживает импульс записи на время, необходимое для надежного гашения сигналов во всех ячейках рекуррентного регистра 9. Кроме того, с выхода ячейки памяти 10 сигнал подготовки через линию задержки 5 переписывается на ее вход записи.

Следуюш,ая серия входных импульсов вновь вызывает срабатывание ячейки памяти 10 старшего разряда, гашение рекуррентного регистра 9 и продвижение сигнала на следующую (вторую) ячейку последовательного регистра 1, при этом сигнал с выхода этой ячейки через соответствующий (второй) вход переключателя 2 производит считывание с блока 3 переноса старшего разряда. Сигнал с его выхода производит подготовку к срабатыванию ячейки памяти 10 следующего разряда путем записи импульса на ее вход.

Одновременно сигнал с выхода блока 3 нереноса старшего разряда производит подготовку к работе следующего младшего разряда путем подачи сигнала на вход записи блока переноса этого разряда и гашение всех ячеек последовательного регистра 1. Через линию задержки 7 производится подготовка к новоротному функционированию (на следующем десятичном разряде) последовательного регистра 1 путем записи сигнала в его первую ячейку.

Следующий цикл состоит в том, что после прохождения на вход счетчика входных импульсов производятся такие же операции с рекуррентным регистром 9 и ячейкой памяти 10 следующего младшего разряда, как описано выше. Однако переключатель этого разряда устанавливается в нулевое положение, поэтому сигнал с выхода блока 3 переноса проходит через линию задержки 6 и нулевой вход переключателя 2 и нронзводит считывание сигнала с блока 3 переноса этого же разряда. Таким образом осуществляется сдвиг коэффициента пересчета на один (второй) разряд.

Сигнал нодготовки поступает на вход записи ячейки памяти 10 младшего разряда, поступление каждого входного импульса приводит к срабатыванию ячейки памяти 10 младшего разряда (правая по схеме), а через нее

и к продвилсению сигналов по ячейкам последовательного регистра 1 с частотой следования входных нмнульсов.

В момент поступления четвертого входного импульса сигнал ноступает на выход блока 3 переноса младшего разряда и, следовательно, на выход всего счетчика.

Сигнал на выходе счетчика производит гашение импульсов во всех ячейках памяти 10 (кроме старшего разряда) и ячейках последовательного регистра 1, кроме того, он производит запись импульса нодготовки в блок 3 переноса первого старшего разряда, в результате чего счетчик подготовлен к следующим полным циклам счета.

Благодаря применению блоков переноса, ячеек памяти и линий задержки, соединенных определенным способом с последовательным и рекуррентным регистрами, удается получить любой целый коэффицниет пересчета счетчика в пределах от 1 до 999 входных импульсов. При увеличении числа разрядов счетчика на единицу в устройстве добавляется лишь ячейка памяти с линией задержки и блок переноса с линией задержки.

Длина последовательного регистра постоянна и в десятичной системе счета равна 9. Длина рекуррентного регистра выбирается из расчета числа разрядов коэффициента пересчета.

Предмет изобретения

Десятичный счетчик импульсов на ферритполупроводниковых элементах с регулируемым коэффициентом пересчета, состоящий из рекуррентного регистра сдвига с дешифратоpOiVi и последовательного регистра сдвига, выход каждой ячейки которого подключен к соответствующим входам декадных переключателей коэффициента пересчета, отличающийся тем, что, с целью повышения надежности, выходы дешифратора подключены к продвигающим обмоткам последовательного регистра и обмоткам гашения рекуррентного регистра через ячейки намяти, выход которых соединен через собственную линию задержки с ее входом, вход повторного запуска рекуррентного регнстра соединен с его обмотками гашения через линию задержки, выход переключателя каждого старшего разряда через блок переноса соединен с входами записи ячейки памяти и блока переноса последующего младшего разряда, а через линию задержки - с нулевым входом переключателя последующего младшего разряда, выходы всех блоков переноса соединены непосредственно с обмотками гашения ячеек носледовательного регистра и через линию задержки - с входом записи его первой ячейки, а выход блока переноса низшего разряда подсоединен непо-. средственно к входу записи блока переноса первого старшего разряда, и через линию задерлски - к нулевому входу переключателя этого разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 1965 |

|

SU171171A1 |

| УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1973 |

|

SU367426A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для задания циклов в системах числового программного управления | 1989 |

|

SU1619233A1 |

| Реверсивный счетчик | 1980 |

|

SU907813A1 |

| Устройство для индикации | 1989 |

|

SU1667150A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

Авторы

Даты

1974-09-15—Публикация

1973-01-23—Подача