1

Изобретение относится к области запоминающих устройств, в частности к устройствам для проверки запоминающих модулей.

Известно устройство для контроля запоминающих модулей, содержащее регистр сдвига, одни входы которого подключены к выходам регистра начального состояния, сумматор по модулю два, информационный регистр, выходы которого подсоединены к схеме контроля, регистр адреса и схемы «И. Регистр информации выполнен на триггерах со счетным входом, что позволяет осуществлять проверку запоминающих модулей в режиме эталона для этого режима, а схема сравнения производит сравнение эталонных кодов с кодами, считанными из запоминающего устройства на информационный регистр.

Недостаток известного устройства состоит в том, что оно позволяет создать ограниченное число проверочных режимов запоминающих модулей.

Целью предложения является расщирение функциональных возможностей устройства.

С этой целью устройство содержит регистры маски, выходы которых подключены к управляющим входам схем «И первой и второй групп соответственно, информационные входы которых соединены с соответствующими выходами регистра сдвига, дополнительные сумматора по модулю два по количеству разрядов

регистра сдвига, одни входы которых подключены к выходам соответствующих схем «И второй группы, другие входы всех дополнительных сумматоров, кроме первого, подсоединены к выходам предыдущего разряда регистра сдвига, а выходы - к другим входам регистра сдвига. Выходы схем «И первой группы подключены ко входам сумматора, выход которого соединен со входом первого дополнительного сумматора, а выходы произвольных, групп разрядов регистра сдвига соединены со входами регистра адреса и информационного регистра.

Применение предложенного устройства позволяет создать разнообразные режимы проверки запоминающих модулей. Следует отметить, что это устройство универсально, так как заложенные в него принципы позволяют контролировать запоминающие модули с любым количеством адресных и разрядных линий, в пределах, определяемых числом триггеров регистра сдвига.

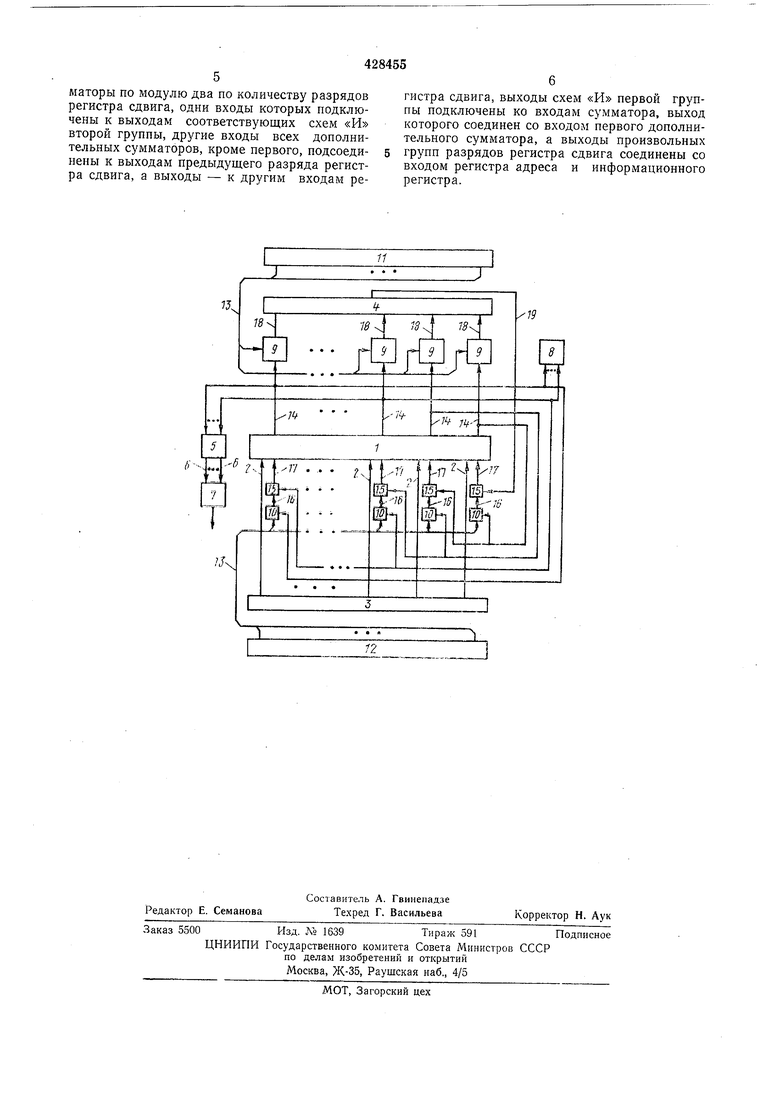

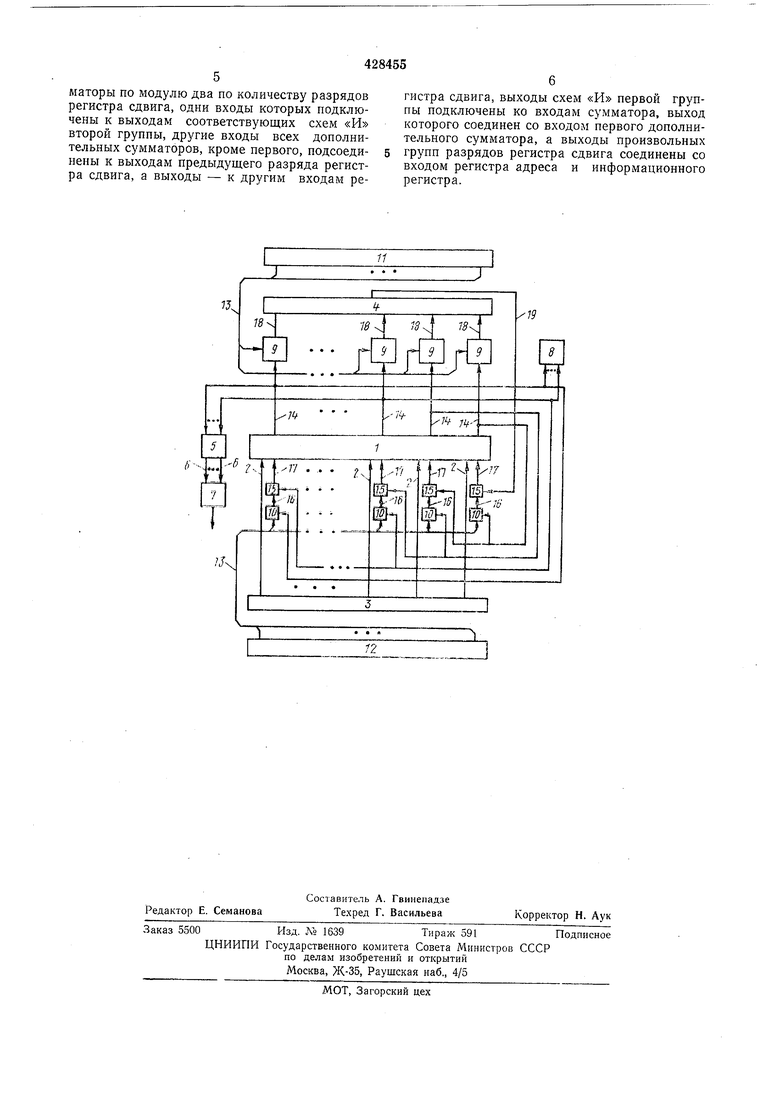

Блок-схема устройства приведена на чертеже.

Устройство состоит из регистра сдвига /, одни входы которого подключены к выходам 2 регистра начального состояния 3, сумматора 4 по модулю два, информационного регистра 5, выходы 6 которого подсоединены к схеме 7 контроля, регистра адреса 8, схем «И первой группы 9 и второй группы 10 и регистров маски 11 и 12, выходы 13 которых соединены с управляющими входами схем «И первой группы 9 и второй группы 10 соответственно. Информационные входы схем «И первой группы 9 и второй группы 10 соединены с соответствующими выходами 14 регистра сдвига I. Кроме того, устройство содержит дополнительные сумматоры 15, количество которых равно числу разрядов регистра сдвига /. Одни входы дополнительных сумматоров /5 подключены к выходам 16 соответствующих схем «И второй группы 10, другие входы дополнительных сумматоров 15, кроме первого, подсоединены к выходам 14 предыдущего разряда регистра сдвига 1, а выходы 17 соединены со вторым входом регистра сдвига 1. Выходы 18 схем «И первой группы 9 подключены ко входам сумматора 4, а выход 19 сумматора 4 подключен к входу первого дополнительного сумматора 15. Выходы произвольных разрядов регистра сдвига / соединены со входами регистра адреса 8 и информационного регистра 5, Все коды, реализуемые предлагаемым устройством, разделяются на два класса - ли-нейные коды и нелинейные коды. Работа устройства в режиме получения линейных кодов осуществляется следующим образом. Код начального состояния с регистра начального состояния 3 поступает на одни входы регистра сдвига / и, пройдя через схемы «И первой группы 9, суммируются сумматором 4. Результат суммы с выхода 19 сумматора 4 передается через дополнительный сумматор 15 на второй вход первого разряда регистра сдвига 1. При этом конкретный вид преобразования определяется кодом, занесенным на регистр маски 11, выходы 13 которого соединены с управляющим входом схем «И первой группы 9. На регистр маски 12 заносится нулевой код, отличающий схемы «И второй группы 10 от дополнительных сумматоров 15. Выходы произвольных разрядов регистра сдвига 1 подключены ко входам регистра адреса 8 и информационного регистра 5 и задают псевдослучайную последовательность записываемой в запоминающий модуль информации. Правильность считанной из запоминающего модуля информации, поступающей на вход информационного регистра 5 (на чертеже эта связь не показана), контролируется схемой 7. Преобразование, осуществляемое устройством проверки запоминающих модулей, описывается линейной возвратной последовательностью: А, . X, где;:, (Х1,Х2,...,Х„ 0000 . Коэффициенты а, задаются регистром маски У7 и могут принимать значения О или 1, общее число преобразований - 2 . В режиме получения нелинейных кодов на регистр маски 12, выходы 13 которого соединены с управляющими входами схемы «И второй группы 10, заносится код нелинейного преобразования. Нелинейное преобразование может быть описано нелинейной возвратной последовательностьюгде У / (У 0000 . а 1 Коэффициенты b J задаются регистром маски 12 и могут принимать значения О или 1. При этом, если коэффициент йу 1, то соответствующий разряд регистра сдвига 1 работает в режиме со счетным входом, а в противном случае - в режиме сдвига. Общее число нелинейных преобразований- 22 . Предложенное устройство для проверки запоминающих модулей позволяет существенно увеличить число проверочных текстов и, соответственно, повысить достоверность контроля запоминающих модулей. Тесты, генерируемые устройством, включают в себя все известные тесты проверки запоминающих модулей. Пред м е т и з о б р е т е н и я Устройство для контроля запоминающих модулей, содержащее регистр сдвига, одни входы которого подключены к выходам регистра начального состояния, сумматор по модулю ва, информационный регистр, выходы которого подсоединены к схеме контроля, регистр адреса и схемы «И, отличающееся тем, что, с елью расщирения функциональных возможостей устройства, оно содержит регистры аски, выходы которых подключены к управяющим входам схем «И первой и второй рупп соответственно, информационные входы оторых соединены с соответствующими выодами регистра сдвига, дополнительные сумматоры по модулю два по количеству разрядов регистра сдвига, одни входы которых подключены к выходам соответствующих схем «И второй группы, другие входы всех дополнительных сумматоров, кроме первого, подсоединены к выходам предыдущего разряда регистра сдвига, а выходы - к другим входам регистра сдвига, выходы схем «И первой группы подключены ко входам сумматора, выход которого соединен со входом первого дополнительного сумматора, а выходы произвольных групп разрядов регистра сдвига соединены со входом регистра адреса и информационного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Датчик кодов для устройства контроля запоминающих блоков | 1974 |

|

SU521608A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU310308A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля блоков памяти | 1980 |

|

SU926725A1 |

| Ассоциативное оперативное запоминающее устройство | 1987 |

|

SU1462420A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Буферное запоминающее устройство с произвольной выборкой двумерного фрагмента | 1986 |

|

SU1444784A1 |

| Устройство для контроля памяти | 1983 |

|

SU1167660A1 |

18

18

HjJ Hj4 Г

Авторы

Даты

1974-05-15—Публикация

1972-07-28—Подача