( 5) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Генератор испытательных последовательностей | 1987 |

|

SU1543396A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для диагностирования аппаратуры обработки данных | 1985 |

|

SU1390610A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для диагностического контроля оперативной памяти | 1991 |

|

SU1807525A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1543442A1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU790019A1 |

I

Изобретение относится к запоминающим устройствам (ЗУ), в частности к устройствам контроля ЗУ.

Известно устройство контроля ЗУ, содержащее блоки формирования контрольных кодов D 1.

Наиболее близким к предлагаемому является устройство для контроля запоминающих модулей, содержащее регистр сдвига, регистр начального состояния, сумматоры по модулю два, ин({юрмационный регистр, схему контроля, регистр адреса, регистры маски и схемы И.

Известное устройство реализует линейные и нелинейные коды, что позволяет существенно увеличить число проверочных тестов С2.

Недостатками известных устройств являются ложность и малое быстродействие при (|юрмировании тестов, что делает невозможным контроль ЗУ на предельных частотах обращения.

Цель изобретения - повышение быстродействия устройства для контроля блоков памяти.

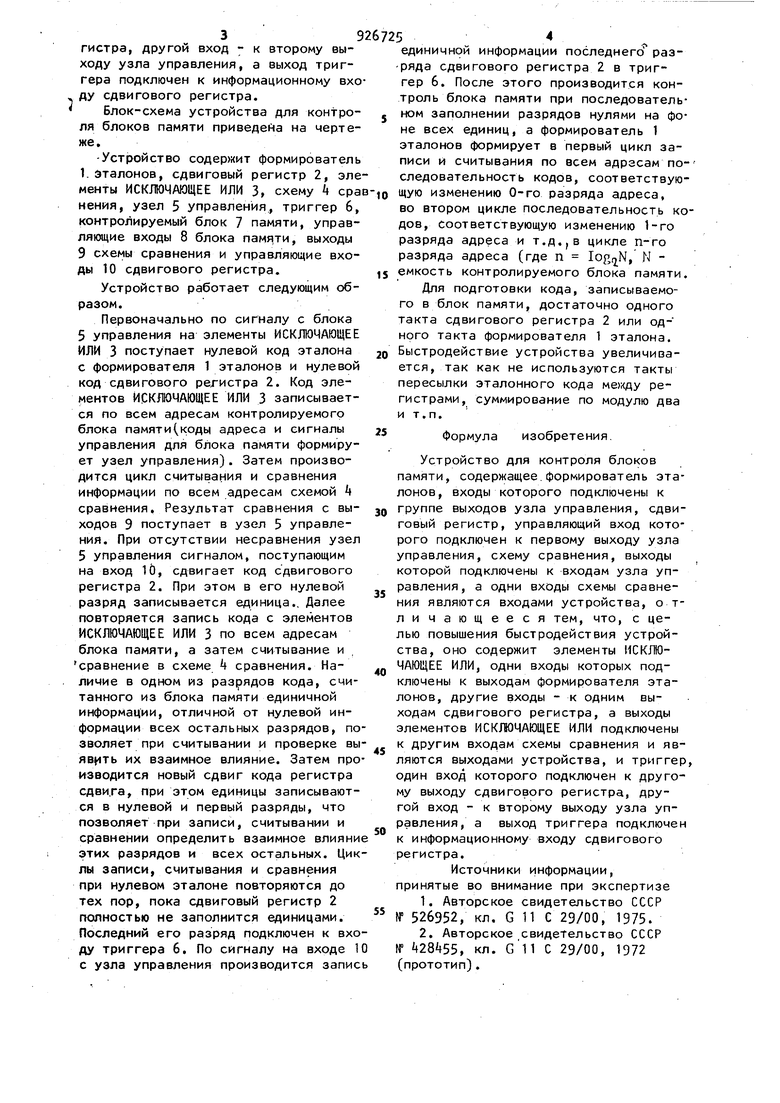

Поставленная цель достигается тем, что в устройство для контроля блоков памяти,содержащее формирователь эталонов, входы которого подключены к группе выходов узла управления, сдвиговый регистр, управляющий вход которого подключен к первому выходу

10 узла управления, схему сравнения, выходы которой подключены к входам узла управления, а одни входы схемы сравнения являются входами устройства, дополнительно введены элементы

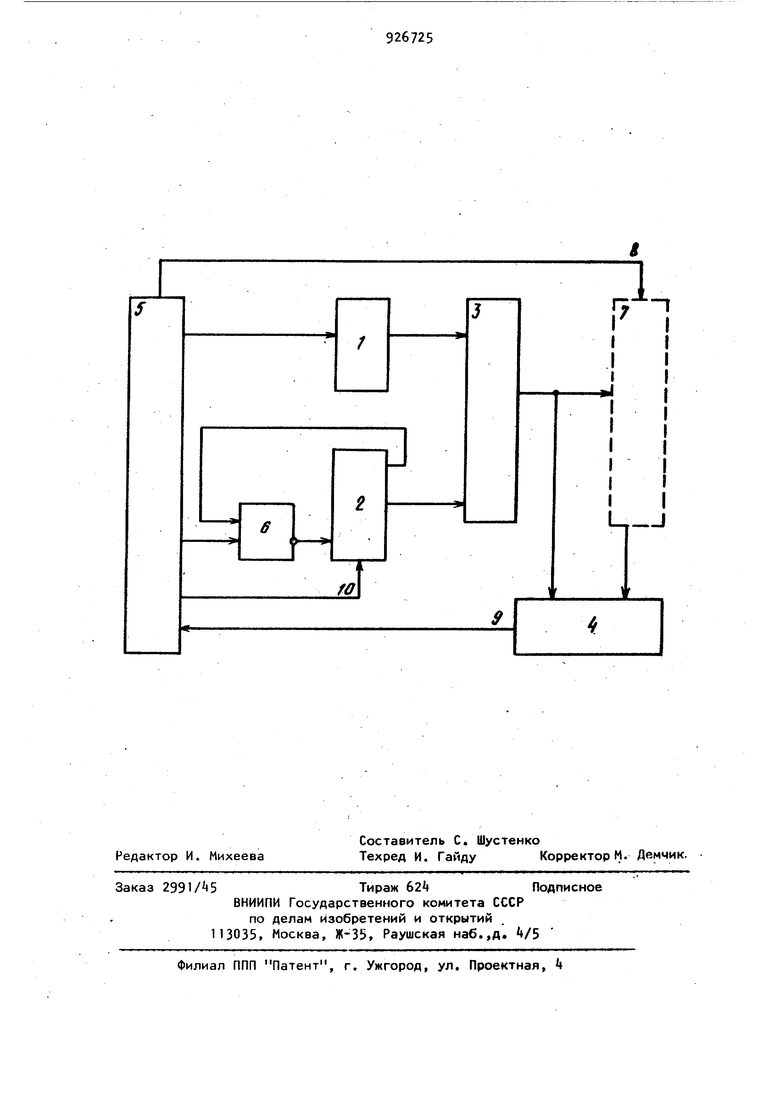

15 ИСКЛЮЧАЮЩЕЕ ИЛИ, одни входы которых подключены к выходам формирователя эталонов, другие входы - к одним выходам сдвигового регистра, а выходы элементов ИСКШЧАЮЩЕЕ .ИЛИ подключе20ны к другим входам схемы сравнения и являются выходами устройства, и триггер, один вход которого подключен к другому выходу сдвигового рё39гистра, другой вход - к второму выходу узла управления, а выход триггера подключен к информационному вхо ду сдвигового регистра. Блок-схема устройства для KOHtpoля блоков памяти приведена на чертеже, -Устройство содержит формирователь 1. Эталонов, сдвиговый регистр 2, эле менты ИСКЛЮЧАЮЩЕЕ ИЛИ 3, схему k сра нения, узел 5 управления, триггер 6, контролируемый блок 7 памяти, управляющие входы 8 блока , выходы 9 схемы сравнения и управляющие входы 10 сдвигового регистра. Устройство работает следующим образом. Первоначально по сигналу с блока 5 управления на элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3 поступает нулевой код эталона с формирователя 1 эталонов и нулевой код сдвигового регистра 2. Код элементов ИСКЛЮЧАЮЩЕЕ или З записывается по всем адресам контролируемого блока памяти(коды адреса и сигналы управления для блока памяти формирует узел управления). Затем производится цикл считывания и сравнения информации по всем адресам схемой k сравнения. Результат сравнения с выходов 9 поступает в узел 5 управления. При отсутствии несравнения узел 5 управления сигналом, поступающим на вход 1U, сдвигает код сдвигового регистра 2. При этом в его нулевой разряд записывается единица.. Далее повторяется запись кода с элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 по всем адресам блока памяти, а затем считывание и сравнение в схеме 4 сравнения. Наличие в одном из разрядов кода, считанного из блока памяти единичной информации, отличной от нулевой информации всех остальных разрядов, по зволяет при считывании и проверке вы их взаимное влияние. Затем про изводится новый сдвиг кода регистра сдви.га, при этом единицы записываются в нулевой и первый разряды, что позволяет при записи, считывании и сравнении определить взаимное влияни этих разрядов и всех остальных. Цик лы записи, считывания и сравнения при нулевом эталоне повторяются до тех пор, пока сдвиговый регистр 2 полностью не заполнится единицами. Последний его разряд подключен к вхо ду триггера 6, По сигналу на входе 1 с узла управления производится запис единичной информации последнего разряда сдвигового регистра 2 в триггер 6. После этого производится контроль блока памяти при последовательном заполнении разрядов нулями на фоне всех единиц, а формирователь 1 эталонов формирует в первый цикл записи и считывания по всем адресам последовательность кодов, соответствующую изменению 0-го разряда адреса, во втором цикле последовательность кодов, соответствующую изменению 1-го разряда адреса и т.д.,в цикле п-го разряда адреса (где п , N емкость контролируемого блока памяти. Для подготовки кода, записываемого в блок памяти, достаточно одного такта сдвигового регистра 2 или одного такта формирователя 1 эталона. Быстродействие устройства увеличивается, так как не используются такты пересылки эталонного кода между регистрами, суммирование по модулю два и т.п. Формула изобретения. Устройство для контроля блоков памяти, содержащее.формирователь эталонов , входы которого подключены к группе выходов узла управления, сдвиговый регистр, управляющий вход которого подключен к первому выходу узла управления, схему сравнения, выходы которой подключены к входам узла управления, а одни входы схемы сравнения являются входами устройства, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, одни входы которых подключены к выходам формирователя эталонов, другие входы - к одним выходам сдвигового регистра, а выходы элементов ИСКЛОЧАЮЩЕЕ ИЛИ подключены к другим входам схемы сравнения и являются выходами устройства, и триггер, один вход которо.го подключен к другому выходу сдвигового регистра, другой вход - к второму выходу узла управления, а выход триггера подключен к информационному входу сдвигового регистра. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 526952, кл. G 11 С 29/00, 1975. 2,Авторское свидетельство СССР № , кл, GII С 29/00, 1972 (прототип).

Авторы

Даты

1982-05-07—Публикация

1980-05-05—Подача