ДАТЧИК КОДОВ ДЛЯ УСТРОЙСТВА КОНТРОЛЯ БЛОКОВ ЗАПОМИНАЮЩИХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное запоминающее устройство | 1978 |

|

SU701349A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для диагностики неисправностей цифровых узлов | 1987 |

|

SU1481773A1 |

| Устройство для вычисления коэффициентов обобщенных функций Хаара | 1979 |

|

SU942036A1 |

| Устройство для контроля и диагностики логических блоков | 1985 |

|

SU1302284A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

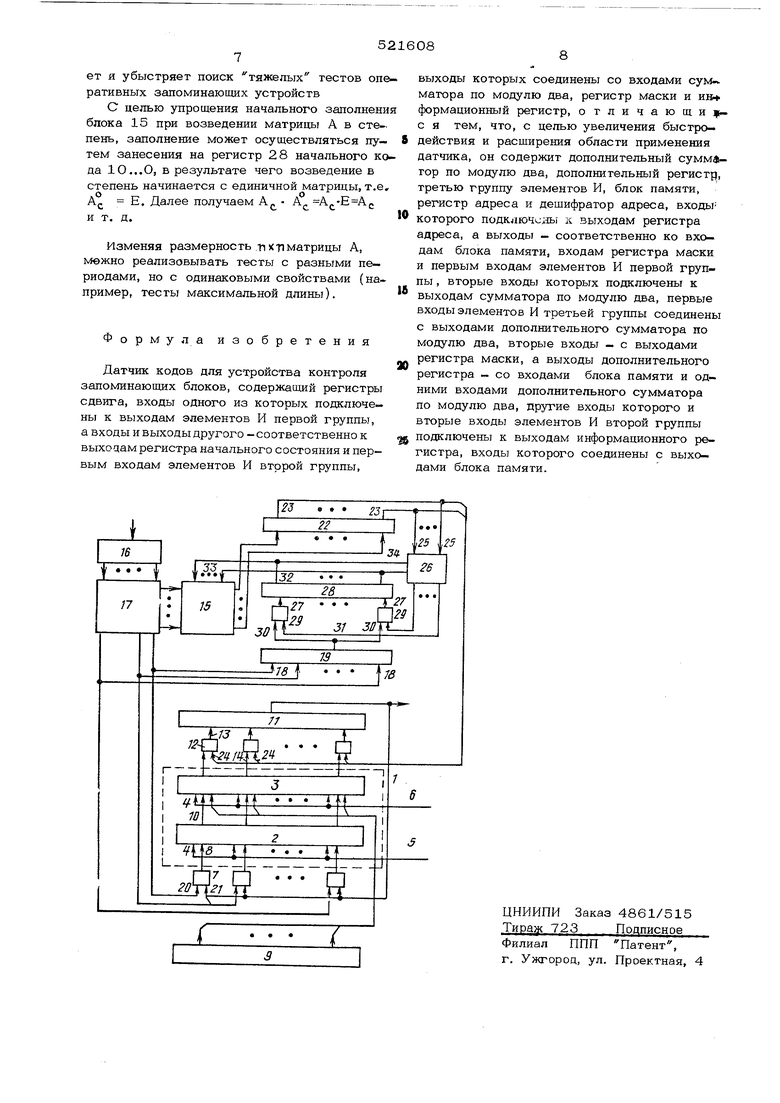

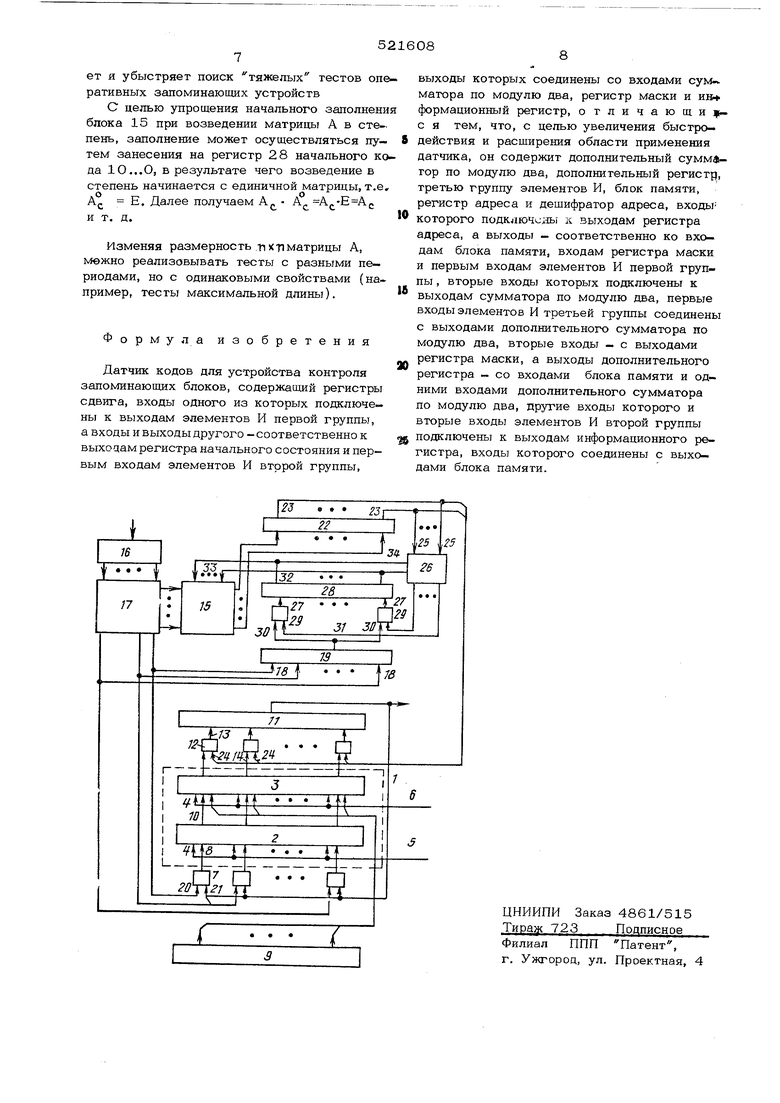

Изобретение относится к области запоминающих устройств. Известен датчик кодов для устройства контроля запоминающих блоков, содержащий регистры сдвига, входы одного из которых подключены к выходам элементов И первой группы, а входы и выходы другого - соответственно к выходам регистра начального состояния и первым входам элементов И второй группы, выходы которых соединены с входами сумматора по модулю два, регистр маски и информапионный регистр. Недостаток известного датчика состоит в том, что управление процессом генерации диагностических тестов (в данном случае линейных и нелинейных возвратных последовательностей) осуществляется от внешнего источника, а именно от тумблерных регистров маски (в простейшем случае) или от внешнего вычислительного устройства (упра ляющей ЭВМ). С целью уменьшения времени проверки запоминающих блоков за счет введения в состав устройства аппаратных средств для автоматизации процесса смены, тестов, генерируемых датчиком, и повышения точности контроля за счет существенного увеличения количества тестов и усложнения ихструк- туры предлагаемый датчик содержит дополнительный сумматор по модулю два, дополнительный регистр, третью группу элементов И , блок памяти, регистр адреса и дешифратор адреса, входы которого подключены к выходам регистра адреса, а выходы соотвегсгвенно к входам блока памяти, входам регистра маски и первым входам элементов И первой группы, вторые входы которых подключены к выходам сумматора по модулю два, первые входы элементов И третьей группы соединены с выходами дополнительного сумматора по модулю два, вторые входы - с выходами регистра маски, а выходы дополнительного регистра - со входами блока памяти и одними входами дополнительного сумматора по модулю два, другие входы которого и вторые входы элементов И второй группы подключены к выходам информационного регистра, входы которого соединены с выходами блока памяти. На чертеже приведена блок-схема предла латаемого датчика. Датчик содержит регистр 1 сдвига, состоящего из первого и второго регистров 2 и 3 сдвига, к синхронизирующим входам 4 которых подсоединены соответственно шины 5 и 6 синхроимпульсов. Элементы И 7 первой группы присоединены к входам 8 регистра 2, а выходы регистра 9 начального состояния подключены к входам 1О регист- ра 3. Датчик содержит также сумматор 11 по модулю два и элементы И 12 второй группы, выходы 13 последних соединены с входами сумматора 11, а первые входы 14 - с соответствующими выходами регист- ра 3. Кроме того, датчик содержит блок 15 памяти и регистр 16 адреса, подключенный к блоку 15 через дешифратор 17 адреса, выходы которого также соединены с соответствующими входами 18 регистра 19 маски и первыми входами 2 О элементов И 7. К вторым входам 21 элементов И 7 присоединен выход сумматора 11. К выходам блока 15 подсоединены входы информационного регистра 22, а его выходь 2 3 соединены с вторыми входами 24 соответствующих элементов И 12 и входами 25 дополнительного сумматора 26 по модулю два, связанного выходами с входами 27 дополни тельного регистра 28 через элементы И 29 третьей группы, входы 30 которых поссоединены к выходу 31 регистра 19. Выходы 32 регистра 28 подключены к соответствующим входам 33 блока 15 и входам 34 сумматора 26. Преобразование, осуществляемое датчико описывается матричным преобразованием -4i А.г,, 11« гт Коэффициенты матрицы А и координаты векторов Ъ- и Х . принимают значени О или 1. Для хранения координат вект ра I используется регистр 3, а для хранениякоординат вектора Z.- регистр 2. Коэффициенты матрицы А хранятся в блоке 15, причем емкость блока составляет п ячеек по n разрядов, и коэффициенты матрицы А записываются в блок 15 построчно, т. е. каждая строка матрицы записывается в отдельную П -разрядную ячейку блока 15. Работа датчика в режиме генерации теста с фиксированной матрицей А преобразования осуществляется следующим образом. Код TQ начального состояния заносится на регистр 3, с выходов которого он посту- пает на входы 14 элементов И 12. В соответствии с начальным кодом адреса, занесенным на вход регистра 16, посредством воз буждения соответствующих выходов дешифратора 17 выбирается определенная ячейка блока 15. Регистр 16 адреса вдальнейшем работает в режиме счетчика, изменяя на единицу свое состояние в каждом такте рабо ты датчика. Информация, считанная иэ блока 15, пост пает на входы регистра 22, с выходов которого она передается на входы 24 элементов И 12. Если на регистре 16 находится код ОО...О, то в блоке 15 выбирается код, соответствующий первой строке матрицы А, т. е. первый код маски. Информация с вы-, ходов регистра 3 пропускается на вход сумматора 11 только через те элементы И 12, соответствующие единицам кода маски. Полученная сумма с выхода сумматора 11 передается на входы 21 элементов И 7 и через элементы, соответствующие выбран, ной ячейке блока 15 (например, первый элемент И справа на чертеже), она поступает на вход первого разряда регистра 2 и записывается в него после прихода ближай шего синхроимпульса по щине 5. Информация с выхода сумматора 11 используется в ка честве выходной информационной последовательности датчика. В следующем такте регистр 16 измен5 ет свое состояние на единицу, из блока 15 выбирается вторая строка матрицы А, т. е. второй код маски, новое значение суммы с выхода сумматора 11 поступает на выход датчика и записывается во второй разряд регистра 2 и т. д. В п- такте информация с выхода сумматора 11 записывается в нос ледний разряд регистра 2. После этого ближайщий синхроимпульс, пришедщий по ши не 6, осуществляет параллельную перепись информации с регистра 2 на регистр 3, а далее счетчик адреса, т. е. регистр 16, сбрасывается в состояние 00..,О и процесс матричного преобразования пов-уоряется над новым вектором Х , 1,2, и т д. В частном случае, когда матрица А дана в виде последовательность, генерируемая датчиком, иредставляет собой линейную возвратную последовательность. В случае произвольной матрицы А последовательность на выходе датчика представляет собой суперпозицию п линейных возвратных последовательностей, подчиняющихся одному и тому же линейному преобразованию, показанному в выражении (3), но сдвинутых одно относительно другого на величину, которая определяется конкратным преобразованием, показанным в выраженни (2). С целью реализации автоматического пе- ребора различных преобразований с различными коэффициентами О, 0 .. , 01 в датчике может быть реализован режим возведения матриць: А. в любую последовательную степень, начиная с первой - А, . , ..; .., А, А, ..., AJ, 1. При этом в блок 15 записывается начальное значение матрицы Aj для чего на регистр 28 заносится начальны код 010...О, который переписывается в ячей ку блока 15 с номером О...01, далее код на регистре 28 сдигается на одну позицию вправо и записывается в ячейку с номером О...10 и т. д. В ячейку с номером Я записывается код с регистра 19 маски, предвари тельно переписывающимся в регистр 28 (цепи, по которым осуществляется эта передача, на чертеже не показаны). Возведение матрицы А в следующую сте пень происходит следующим образом. Регистры 28 и 16 устанавливаются в состояние О...00. В соответствии с кодом, записанным в регистре 16, на регистр 22 выбирается содержимое первой ячейки блоха 15, эта информации складывается по модулю два с информацией, записанной в регистре 28 с помощью сумматора 26. Сумма заносится на регистр 28, через элементы И 29, если в первом разряде регистра 19 хранится код 1. Опрос регистра 19 маски, выявляющий информацию, которая хранится в соответствующем разряде этого регистра, производится с помощью дещифратора 17. Последовательно считывая информа цию из всех ячеек блока 15, можно получить сумму строк матрицы А., соответствуюших местоположению единицы в коде маеки. Сумма накапливается на регистре 28. Далее счетчик адреса переключается в режим вычитания, и на регистр 16 заносится двоичный код п . Код из ячейки блока 15 с номером Т1 считывается на регистр 22, а в блок 15 по этому же адресу записывается код суммы с регистра 28. Из содер.жимого регистра 16 вычитается единица, код с регистра 22 переписывается в регистр 28 (специальные цепи, по ко- торым осуществляется перепись, на чертеже не показаны), перепись можно про- изводить через сумматор 26, если при этом блокируются входы 34 этого суммато- ра, с выхода 31 регистра 19 на управляющие входы элементов И 29 поступает сигнал единицы, а код, считанный из ( П 1)ячейки блока 15, поступает на регистр 22. В этом же такте код с регистра 28 записывается в (п - 1)-ую ячейку блока 15. Процесс продолжается до появления на регистре 16 кода О...ОО,когда в блоке 15 сформируется новое значение матрицы А-А. , А , А и т. д. Если в качестве начального кода маски выбирается примитивный двоичный многочлен, то последовательное возведение соответству- ющей матрицы А в степень эквивалентно возведению в ту же степень корня этого многочлена, поэтому линейное преобразование, порождающее суперпозицию линейных возвратных последовательностей на выходе датчика, может быть описано многочленом, корень которого равен корню начального (первообразного) многочлена, возведенному соответствующую степень. Последователь возведение АС в степень перечисляет все возможные неприводимые многочлены данной степени. Таким образом, в датчике реализуется автоматический перебор всех возможных линейных и матричных преобразований с заданными свойствами, например, примитивных (период которых равен 2-1), неприводимых непримитивных и приводимых (период которых меньше 2 .- 1). Используя этот датчик в сочетании с устройством для контро ля запоминающих блоков, в котором создаются и фиксируются путем измерений наихуд- щие условия эксплуатации проверяемых тблоков, например изменяются напряжения в цепях питания блоков и сопоставляются зафиксированные значения исследуемого параметра блока, полученные для разных преобразований матрицы А , AJ., А ,... можно выделить один или несколько наиболее тяжелых тестов для данного типа блоков. Такой направленный перебор существенно упрощает я убыстряет поиск тяжелых тестов опе ративных запоминающих устройств С целью упрощения начального заполнени блока 15 при возведении матрицы А в степень, заполнение может осуществляться путем занесения на регистр 28 начального ко да 10.„О, в результате чего возведение в степень начинается с единичной матрицы, т.е А° Е, Далее получаем А А, (, и т. д. Изменяя размерность пх 71 матрицы А, мвжно реализовывать тесты с разными периодами, но с одинаковыми свойствами (например, тесты максимальной длины). Формула изобретения Датчик кодов для устройства контроля запоминающих блоков, содержащий регистры сдвига, входы одного из которых подключены к выходам элементов И первой группы, а входы и выходы другого -соответственно к выходам регистра начального состояния и первым входам элементов И второй группы. выходы которых соединены со входами сумматора по модулю два, регистр маски и ин формационный регистр, отличающи с я тем, что, с целью увеличения быстродействия и расширения области применения датчика, он содержит дополнительный сумматор по модулю два, дополнительный регистр:, третью группу элементов И, блок памяти, регистр адреса и дешифратор адреса, входы которого подключс; к выходам регистра адреса, а выходы - соответственно ко входам блока памяти, входам регистра маски и первым входам элементов И первой группы , вторые входы которых подключены к выходам сумматора по модулю два, первые входы элементов И третьей группы соединены с выходами дополнительного сумматора по модулю два, вторые входы - с выходами регистра маски, а выходы дополнительного регистра - со входами блока памяти и одними входами дополнительного сумматора по модулю дра, другие входы которого и вторые входы элементов И второй группы подключены к выходам информационного регистра, входы которого соединены с выходами блока памяти.

Авторы

Даты

1976-07-15—Публикация

1974-01-16—Подача