1

Изобретение относится к технике передачи дискретной информации и предназначено для измерения статистических характеристик дискретных каналов.

Известно устройство для автоматического измерения характеристик дискретного канала, содержащее основную схему сравнения, дополнительную схему сравнения, основной регистр с сумматором по модулю два, дополнительный регистр с сумматором по модулю два и счетчик с цепью установки в нулевое состояние.

Однако известное устройство не дает возможности выделять поток фазовых сдвигов и дает большую погрешность в измерении числа аддитивных ошибок.

Целью изобретения является повышение достоверности измерения.

Для этого выход основной схемы сравнения подключен к одному из входов дополнительного регистра, соответствуюш,ие выходы которого подключены ко входам дешифратора и одновременно к первым входам сумматоров дополнительно введенного блока установки фазы эталонной последовательности, к другим входам сумматоров, соединенных со схемами совпадения этого же блока, подключены соответствуюш.ие выходы основного регистра, а первые выходы схем совпадения блока установки фазы эталонной последовательности

подключены соответственно ко входам дополнительно введенной схемы «Р1ЛИ и ко входам основного регистра, а к другим входам схем совпадения блока установки фазы эталонной последовательности подключен выход счетчика, ко второму входу которого одновременно подключены выход дешифратора и выход дополнительной схемы сравнения, при этом к другому входу ячейки памяти через второй инвертор подключен выход схемы «ИЛИ.

В предлон енном устройстве использовано известное свойство рекуррентных последовательностей, заключающееся в том, что сумма двух идентичных рекуррентных последовательностей (имеется в виду поэлементное суммирование по модулю два), сдвинутых друг относительно друга на любое, не кратное периоду последовательности, число шагов, дает рекуррентную последовательность с таким же законом построения, что и исходные последовательности. Следовательно, если проверять выполнение рекуррентных соотношений в последовательности импульсов, которая является результатом сравнения (поэлементного суммирования по модулю два) испытательной и эталонной последовательностей, то можно установить, является ли причиной несоответствия символов иснытательной и эталонной последовательности появление аддитивных

ошибок или же фазовое рассогласование. Если последовательность, являющаяся результатом сравнения, удовлетворяет рекуррентному закону, следует считать, что имеет место фазовое рассогласование. При этом можно определить фазу результирующей последовательности и установить фазы эталонной иоследовательности в соответствии с фазой принимаемой последовательности.

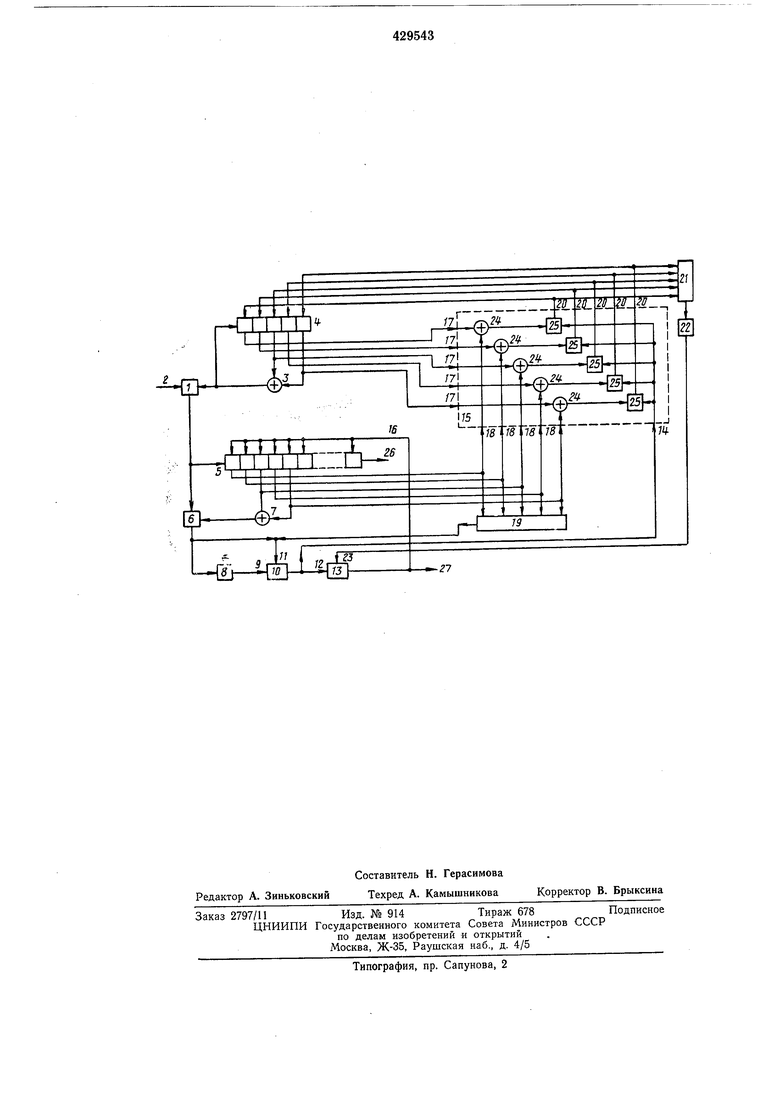

На чертеже приведена блок-схема устройства.

Устройство для автоматического измерения характеристик дискретного канала содержит основную схему 1 сравнения, вход 2 которой подключен -к выходу дискретного канала связи, а второй ее вход - к выходу сумматора 3 по модулю два, входы которого подключены к выходам третьей и пятой (нумерация слева направо) ячеед основного регистра 4 сдвига, вход которого подключен к выходу сумматоpa 3. Выход схемы 1 сравнения подключен параллельно ко входу дополнительного регистра 5 сдвига и к одному из входов дополнительной схемы 6 сравнения. Второй вход схемы 6 сравнения подключен к выходу сумматора 7 по модулю два, входы которого подключены к выходам третьей и пятой ячеек регистра 5 сдвига. Выход схемы 6 сравнения через инвертор 8 подключен к счетному входу 9 счетчика 10. Выход схемы 6 сравнения подключей ко входу 11 установки счетчика 10 в нулевое состояние. Выход счетчика 10 подключен параллельно ко входу 12 записи ячейки 13 памяти и ко входу 14 блока 15 установки фазы эталонной последовательности. Выход ячейки 13 подключен к цепи 16 установки ячеек регистра 5 сдвига в нулевое состояние.

Выходы всех ячеек основного регистра 4 сдвига подключены ко входам 17 блока 15. Выходы первых пяти ячеек дополнительного регистра 5 сдвига подключены ко входам 18 блока 15 установки фазы эталонной последовательности и параллельно ко входам дешифратора 19 нулевого состояния этих ячеек регистра 5 сдвига. Выход дешифратора 19 подключей ко входу И установки счетчика 10 в нулевое состояние.

Выходы 20 блока 15 подключены ко входам установки ячеек регистра 4 и параллельно ко входам схемы «ИЛИ 21, выход которой через инвертор 22 подключен ко входу 23 запрета ячейки 13 памяти.

Блок 15 содержит пять сумматоров 24 по модулю два и пять схем совпадения 25. Вхо.. .00100(1)0110011111000110111010100001001... - .. .(1)011001111100011011101010000100101100... - ...100(1)011001111100011011101010000100101... -

(В скобки помещены символы, условпо принятые за начала периодов рекуррентных последовательностей) .

ды 17 блока 15 подключены к одним входам сумматоров 24, а входы 18 - к другим входам сумматоров 24. Выходы сумматоров 24 подключены ко входам схем совпадения 25. Другие входы схем совпадения 25 подключены ко входу 14 блока 15. Выходы схем совпадения 25 являются выходами 20 блока 15. Включение сумматоров 24 и схем совпадения 25 осуществлено так, что один из входов /(-сумматотора (/(1, 2, ...5) 24 соединен с выходом /С-ой ячейки основного регистра 4 сдвига, второй вход - с выходом К-ои ячейки дополнительного регистра 5 сдвига, а выход К.-го сумматора 24 подключен ко входу той схемы совпадения 25, выход которой подключен ко входу установки К-ой ячейки регистра 4 сдвига.

Выход 26 регистра 5 сдвига может быть подключен к устройству, анализирующему или фиксирующему поток аддитивных ошибок. Выход 27 подключается к устройству, анализирующему или фиксирующему поток сбоев фазы по циклам.

Устройство работает .следующим образом.

Испытательная двоичная последовательность с выхода дискретного канала поступает на вход 2 схемы 1 сравнения. На второй вход схемы 1 сравнения, представляющей собой сумматор по модулю два, поступает двоичная эталонная (рекуррентная) последовательность, формируемая регистром 4 и сумматором 3 по модулю два.

Если поступающая с выхода дискретного канала испытательная последовательность не содер кит ошибок и ее фаза совпадает с фазой эталонной последовательности, поступающей с выхода сумматора 3, то на выходе схемы 1 будут сигналы, соответствующие нулям («О). Каждая ошибка в испытательной последовательности приведет к появлению на выходе схемы 1 сигнала, соответствующего «1. Если сравниваемые испытательная и эталонная рекурретные последовательности находятся не в фазе по циклу и ошибки в испытательном сигнале отсутствуют, то на выходе схемы 1 будет формироваться аналогичная рекуррентная последовательность, фаза которой не совпадает с фазами последовательностей, поступающих на входы схемы 1.

Пусть, например, сдвиг фазы между эталонной и испытательной последовательностями равен пяти символам. Тогда последовательности на входах схемы 1 и на ее выходе для рассматриваемой конкретной реализации будут следующими:

В общем случае при фазовом рассогласовании сравниваемых последовательностей и на55 личии ошибок в испытательной последовательиспытательная последовательность эталонная последовательность последовательность на выходе схемы 1 ности на выходе схемы 1 появится последовательность, полученная в результате поэлементного сложения по модулю два рекуррентной последовательности и последовательности, соответствующей потоку ошибок. Сигналы с выхода схемы 1 поступают на вход регистра 5 сдвига и на один из входов схемы 6 сравнения, представляющей собой сумматор по модулю два. Рассмотрим процессы автоматического выявления сбоя фазы по циклу и установки фазы эталонной последовательности. Предположим, что ошибки в испытательном сигнале отсутствуют. Рекуррентная последовательность с выхода схемы 1 последовательно продвигается по ячейкам памяти регистра 5. Сигналы с выходов третьей и пятой ячеек регистра 5 поступают на входы сумматора 7. При этом на выходе сумматора 7 формируется рекуррентная последовательность, которая поступает на второй вход схемы 6. Вид и фаза этой последовательности совпадает соответственно с видом и фазой рекуррентной последовательности, поступающей с выхода схемы I. В этом случае на выходе схемы б в тактовые моменты времени будут появляться сигналы, соответствующие нулям («О). Эти сигналы через инвертор 8 поступают на счетный вход 9 счетчика 10. Показания счетчика 10 увеличиваются на единицу, если в тактовый момент времени на его входе будет сигнал, соответствующий «1, т. е. если на выходе схемы б - сигнал, соответствующий «О. По предположению ошибки в испытательном сигнале отсутствуют, вследствие этого при расхождении фаз испытательной и эталонной последовательности, с выхода схемы 6 будут поступать только сигналы, соответствующие нулям («О). Следовательно, показания счетчика 10 будут увеличиваться на единицу в каждый тактовый

Последовательность

Принимаемая испытательная последовательностьЭталонная последовательность

Последовательность на выходе схе- мы 1

После коррекции расхождения фаз

0111010100001001.

0111010100001001. 0000000000000000. момент времени. После заполнения счетчика 10 на его выходе появится сигнал, поступающий параллельно на вход 12 ячейки 13 памяти и вход 14 блока 15 установки фазы эталонной последовательности. Сигнал с выхода ячейки 13 памяти поступает по цепи 16 «установки на нуль ячеек регистра 5 сдвига. Емкость регистра 5 сдвига и емкость счетчика 10 выбирают так. чтобы сигналы, вызванные расхождением фаз испытательной и эталонной последовательностей и поступающие с выхода схемы 1 сравнения, не успевали пройти регистр 5 сдвига и поступить на его выход 26. Автоматическое устранение сбоя фазы по циклу постигается при помощи блока 15. На входы 17 блока 15 поступают сигналы с ячеек регистра 4 сдвига, а на входы 18 блока 15 поступают сигналы с одноименных ячеек регистра 5 сдвига. В момент срабатывания счетчика 10 сигналом с его выхода «Открываются схемы совпадения 25 вследствие чего результат сложения с выходов сумматоров 24 блока 15 поступает через схемы совпадения 25 на входы установки ячеек регистра 4 сдвига. Причелт, на вход установки первой ячейки регистра 4 сдвига поступает сигнал с выхода того сумматора 24, на входы которого поступают сигналы с первых ячеек регистров 4 и 5 сдвига, на вход установки второй ячейки регистра 4 сдвига поступает сигнал с выхода того сумматора 24. на входы которого поступают сигналы со вторых ячеек регистров 4 и 5, и т. д. Таким образом, сигналами с выходов сумматоров 24 блока 15 ячейки регистра 4 сдвига устанавливаются в такое состояние, при котором на выходе сумматора 3 формируется эталонная последовательность, совпадающая по фазе с принимаемой испытательной последовательностью:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения статистических характеристик дискретного канала связи | 1975 |

|

SU558408A1 |

| Устройство для автоматического измерения характеристик дискретного канала связи | 1984 |

|

SU1197103A1 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Способ цикловой синхронизации с динамической адресацией получателя | 2016 |

|

RU2621181C1 |

| Устройство для автоматического измерения характеристик дискретного канала связи | 1983 |

|

SU1141578A2 |

| Устройство фазового пуска | 1986 |

|

SU1350839A1 |

| Генератор псевдослучайной последовательности | 1979 |

|

SU857984A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1686697A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ НА ОСНОВЕ КОМБИНИРОВАННОГО ПРИМЕНЕНИЯ ДВОЙСТВЕННОГО БАЗИСА ПОЛЯ GF(2) И ВЫДЕЛЕНИЯ "СКОЛЬЗЯЩЕГО ОКНА" С ОШИБКАМИ | 2014 |

|

RU2580806C2 |

| Система для передачи и приема дискретной информации | 1980 |

|

SU886296A1 |

Итак, после появления сигнала на выходе счетчика 10 расхождение фаз по циклу автоматически устраняется, благодаря чему на входы схемы 1 начинают поступать синфазные рекуррентные последовательности, так что с выхода схемы 1 следует последовательность, состоящая из одних нулей. Вследствие этого, не более чем через пять (число ячеек регистра 4) тактов на оба входа схемы 6 будут поступать последовательности нулей, поэтому

с выхода схемы б будет также поступать последовательность нулей.

Чтобы от нулей, появляющихся на выходе схемы б в синфазном режиме работы, не срабатывал счетчик 10 и не фиксировался сбой фазы по циклу, используется дешифратор 19 нулевого состояния первых пяти ячеек регистра 5 сдвига. Как только эти пять ячеек регистра 5 будут находиться в нулевом состоянии, срабатывает дешифратор 19 и на его выходе

появляется сигнал, который поступает на вход II установки счетчика 10 в нулевое состояние.

Рассмотрим случай, когда испытательная и эталонная рекурретные последовательности, поступающие на входы схемы 1 сравнения, нахолятся в фазе, но в испытательном сигнале присутствуют ошибки.

Поток ошибок с выхода схемы 1 проходит через регистр 5 и поступает на выход 26. Если поток ошибок представляет собой пачку ошибок, то на выходе схемы 6 часто будут появляться сигналы, соответствуюш ие единицам. Эти сигналы, поступая на вход 11 счетчика 10, каждый раз зстанавливают его в нулевое состояние, благодаря чему счетчик 10 не успевает заполниться, и, следовательно, ложная коррекция фазы эталонной последовательности не производиться.

Еслп же поток ошибок представляет собой редкие независимые ошибки с длительными безошибочными интервалами, то единицы с выхода схемы 1 будут появляться редко, и вследствие этого ячейки регистра 5 сдвига будут, как правило, находиться в нулевом состоянии. При этом будет срабатывать дешифратор 19 нулевого состояния регистра 5 сдвига и устанавливать счетчик 10 в нулевое состояние, так что сигнал на выходе счетчика 10 появляться не будет.

В случае возникновения в канале связи кратковременного перерыва на вход 2 схемы 1 сравнения могут поступать либо единицы (...111111...), либо нули (...000000...). Если на вход 2 поступает последовательность единип, то работа устройства ничем не отличается от режима работы при пачках ошибок.

Рассмотрим случай, когда на вход 2 поступает последовательность нулей. В этом случае на выходе схемы 1 сравнения в течение всего времени перерыва будет формироваться рекуррентная последовательность. Вследствие этого с выхода схемы 6 сравнения будут следовать нули, что приведет к заполнению счетчика 10. Появляющийся при этом сигнал на выходе счетчика 10 откроет схемы совпадения 25. Однако на выходах всех схем совпадения 25 будут нули, так как в сумматорах 24 блока 15 сравниваются одинаковые, находящиеся в фазе, участки рекуррентных последовательностей. Появляющийся при этом нуль («О) на выходе схемы «ИЛИ 21 обрап-ается инвертором 22 в единицу. Сигналом с выхода инвертора 22 единица, записанная в ячейк 13 памяти, стирается. Таким образом, несмотря на то, что на выходе счетчика 10 появился сигнал, сигнал на выходе ячейки 13 памяти не будет, т. е. содержимое ячеек регистра 5 сдвига не стирается и ложного обнаружения сбоя фазы по циклу при перерывах не происходит.

В общем случае при расхождении фаз сравниваемых последовательностей и при наличии

ошибок в испытательной рекуррентной последовательности на выходе схемы 1 появится рекуррентная последовательность с ошибками. При этом маловероятно, что первые пять ячеек регистра 5 сдвига будут одновременно находиться в нулевом состоянии, поэтому дешифратор 19 нулевого состояния практически срабатывать не будет. В результате счетчик 10 через некоторое время заполнится, на его выходе появится сигнал, который фиксируется устройством, подключенным к выходу 27, как сбой фазы по циклу и который приведет к стирапию содержимого регистра 5 сдвига. Одновременно этим же сигналом будут открыты схемы совпадения 25, благодаря чему сигналами с сумматоров 24 блока 15 будет установлено состояние ячеек регистра 4 сдвига, синфазное с принимаемой испытательной рекуррентной последовательностью.

Предмет изобретения

Устройство для автоматического измерения характеристик дискретного канала, содержащее основную схему сравнения, к одному из входов которой одновременно подключены один из входов основного регистра и выход первого сумматора, к первому и второму входу которого подключены соответствующие выходы основного регистра, а выход основной схемы сравнения через последовательно соединенные дополнительную схему сравнения, один из инверторов и счетчик подключены к первому входу ячейки памяти, а к другому входу дополнительной схемы сравнения подключен выход второго сумматора, к первому и второму входу которого подключены соответствующие выходы дополнительного регистра, отличающееся тем, что, с целью повышения достоверности измерения, выход основной схемы сравнения подключен к одному из входов дополнительного регистра, соответствующие выходы которого подключены ко входам дешифратора и одновременно к первым входам сумматоров дополнительно введенного блока установки фазы эталонной последовательности, к другим входам сумматоров, соединенных со схемами совпадения этого же блока, подключены соответствующие выходы основного регистра, а первые выходы схем совпадения блока установки фазы эталонной последовательности подключены соответственно ко входам дополнительно введенной схемы «ИЛИ и ко входам основного рг-гистра, а к другиА входам схем совпадения блока установки фазы эталонной последовательности подключен выход счетчика ко второму входу которого одновременно подключены выход дещифратор и выход дополнительной схемы сравнения, при этом к другому входу ячейки памяти через второй инвертор подключен выход схемы «ИЛИ.

Даты

1974-05-25—Публикация

1972-01-07—Подача