Изобретение предназначено для использования в приборостроении управляющих и информационно-измерительных системах

Цель изобретения повышение быстродействия преобразователя

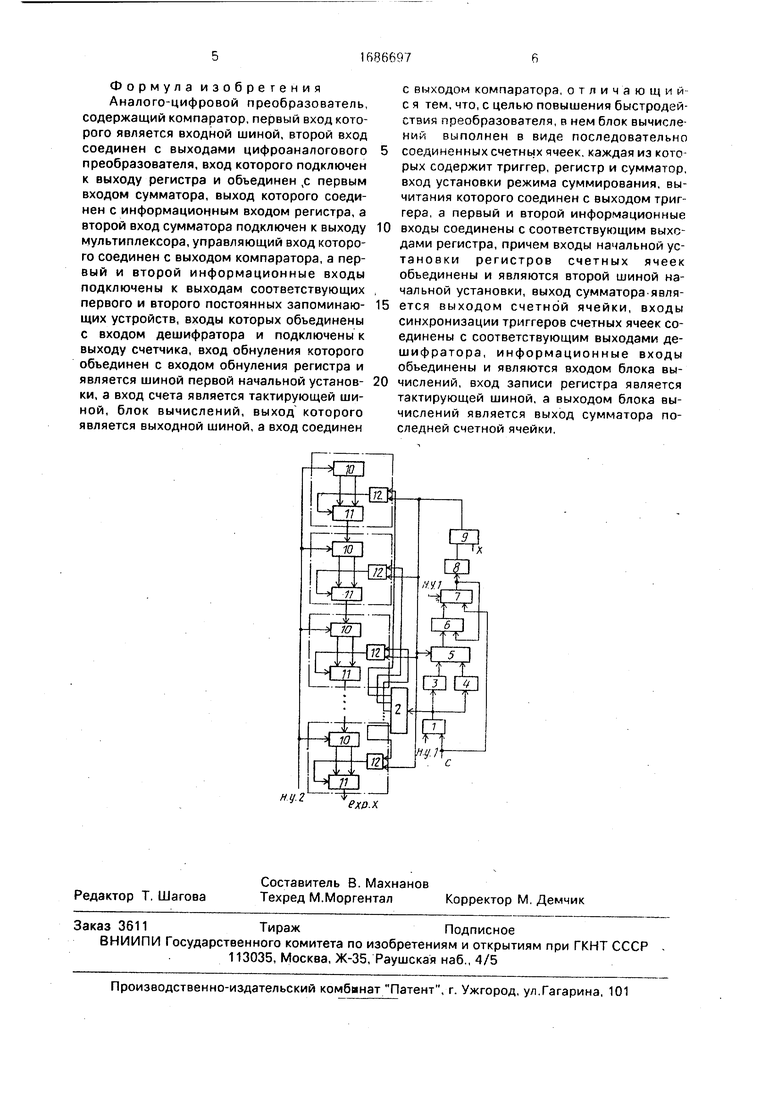

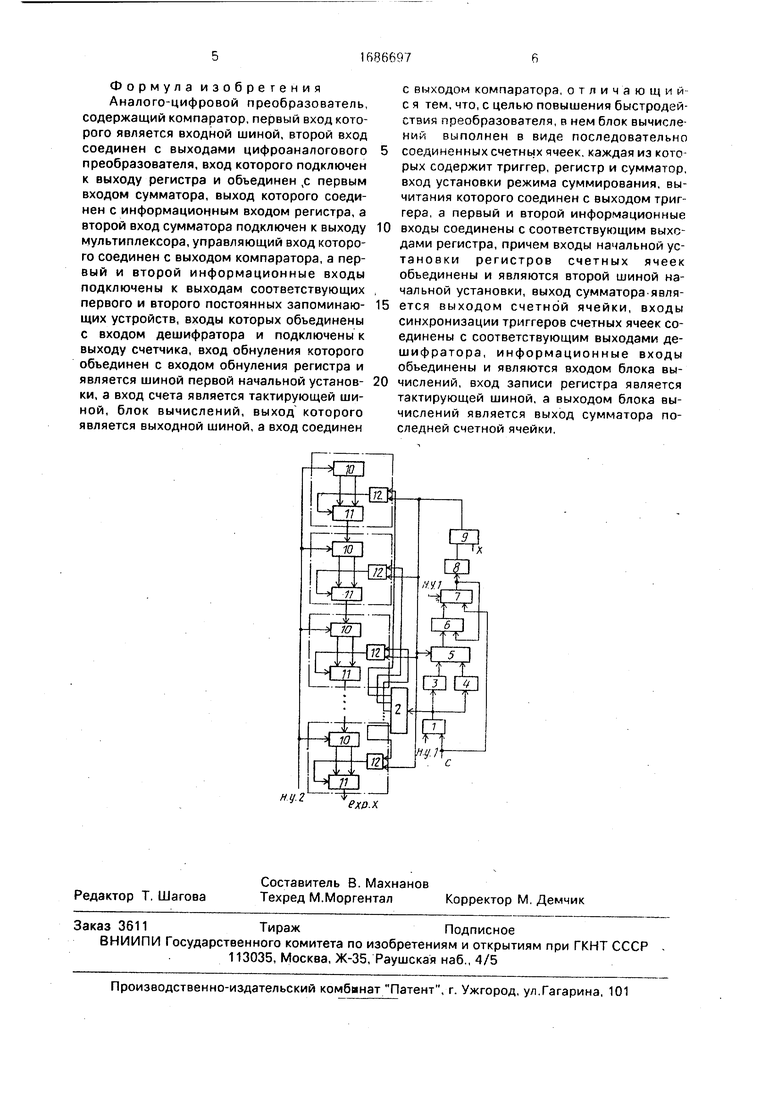

На чертеже представлена блок-схема предлагаемого преобразователя

Преобразователь содержит счетчик 1, дешифратор 2 постоянные запоминающие устройства 3 и 4 мультиплексор 5 сумматор

6, буферный регистр 7, цифроаналоговый преобразователь 8, компаратор 9, блок вычислений, выполненный на счетных ячейках, каждая из которых содержит регистр 10, сумматор 11. триггер 12

Преобразователь работает следующим образом

В основе вычислений по методу цифра за цифрой лежит поразрядная процедура, состоящая из первого и второго этапов преобразователей В результате выполнения

этапа первого производится серия сравнений выходного сигнала цифроанэлогового преобразователя 8 с входным сигналом X, выполняемых компаратором 9. Итерационные уравнения алгоритма Волдера при вычислении последовательности значений § имеют следующий вид

3+1 fl- In (1 + Ј 2Ч)

sign § sign $, где 1 1,1,2,2,3,3п - 1, п- 1,

$ €. (-1.+1) при начальном условии Q X.

В устройстве каноническая форма итерационных уравнений преобразуется к следующему эквивалентному виду i

fl+i х -, I, |п (1 + &0) х

Х2У°

где KQ) {l,1,2,2,3,3п-1. п-1}

Перенумерация в рекуррентных соотношениях и переход от индекса i к индексу J необходим для конвейерной организации второго этапа, так как в конвейере неудобно организовывать повторные итерации с каждой эталонной константой, предусматриваемые при использовании рекуррентных соотношений Волдера для вычисления функции экспоненты. Порядковый номер J - это код счетчика 1, а переменная K(J) - это значения I, используемые в рекуррентных соот- ноимениях Волдера. Переход от I к J реализуется дублированием констант In () и In (1-2 ) в двух соседних словах постоянных запоминающих устройств 3 и 4. Дублирование констант обеспечивает аппаратное выполнение повторных шагов. Реализация вычитания, предусматриваемая первым этапом, может быть реализована двумя эквивалентными способами - путем реализации сумматора 6 по схеме вычитате- ля и путем хранения в постоянных запоминающих устройствах 3 и 4 дополнительных кодов эталонных констант, взятых со знаком минус. Для определенности в устройстве предусматривается замена вычитания сложением с дополнительным кодом отрицательного-числа. Значения Јь представляющие собой результат выполнения первого этапа преобразования, снимаются с выхода компаратора 9 в закодированной форме, так как переменная § означает в устройстве режим сложение/вычитание сумматоров 11 блока вычислений. В связи с этим триггеры 12 настраивают сумматоры 11 на режимы, приводящие к введению во второй этап вычисления коэффициентов, принимающих значения {+,. При поступлении входного сигнала на вход компаратора 9 происходит сравнение этого сигнала с результатом декодирования на цифроаналоговом преобразователе кода регистра 7, представляющего собой результат суммирования сумматором 6 начального значения кода регистра 7 со

значением эталонной константы, подаваемой через мультиплексор 5. Эталонные константы размещаются в постоянных . запоминающих устройствах 3 и 4 и имеют вид In (i + Јi ). Результат сравнения с

первой эталонной константой фиксируется в триггере 12 первой ячейки блока вычислений, после чего инкрементируется код в счетчике 1 и производится подача в устройство следующей эталонной константы. Однако на втором такте преобразования используются те же самые эталонные константы в связи с тем. что в рекуррентных соотношениях необходимо делать повторные итерационные шаги, т.е. задавать значения I следующим образом:

1 1,1,2,2,3,3п-1, п-1.

что достигается дублированием констант в постоянных запоминающих устройствах 3 и 4. Результат второго такта сравнения фиксируется в триггере 12 следующей ячейки, выбор которого осуществляется по сигналу дешифратора 2 и т.д. Таким образом, за N тактов, синхронизируемых синхросерией С, формируется последовательность значений

§ в триггерах 12. Второй этап запускается по сигналу н.у. 2 и обеспечивается конвейером, в каждом ярусе которого вычисляется рекуррентное соотношение Х,-1 Х| + § Xi,

гдеХ1 1.

Вычисления в конвейере обеспечиваются соединением элементов блока вычислений между собой. Таким образом, первый

выход i-ro регистра 10 соединен с одноименными разрядами первого входа 1-го сумматора 11, а второй выход регистра 10 - это те же разряды, но соединяемые со сдвигом, т.е. сдвиг при означает, что первый

разряд выхода соединяется с вторым разрядом входа и т.д., сдвиг при означает, что первый разряд выхода соединяется с третьим разрядом входа и т.д., сдвиг при означает, что первый разряд выхода

0 соединяется с четвертым разрядом входа и т.д. Таким образом и обеспечивается аппаратный (монтажный, схемный) сдвиг, Режим сложение/вычитание в сумматоре 11 задается триггером 12. Работа конвейера не

5 нуждается в управлении и синхронизации и обеспечивает вычисление значения экспоненты по серии § за минимально возможное время - т.е. время срабатывания отдельных элементов конвейера.

Формула изобретения Аналого-цифровой преобразователь, содержащий компаратор, первый вход которого является входной шиной, второй вход соединен с выходами цифроаналогового преобразователя, вход которого подключен к выходу регистра и объединен ,с первым входом сумматора, выход которого соединен с информационным входом регистра, а второй вход сумматора подключен к выходу мультиплексора, управляющий вход которого соединен с выходом компаратора, а первый и второй информационные входы подключены к выходам соответствующих первого и второго постоянных запоминающих устройств, входы которых объединены с входом дешифратора и подключены к выходу счетчика, вход обнуления которого обьединен с входом обнуления регистра и является шиной первой начальной установки, а вход счета является тактирующей шиной, блок вычислений, выход которого является выходной шиной, а вход соединен

с выходом компаратора, отличают, и й- с я тем, что, с целью повышения быстродействия преобразователя, в нем блок вычислений выполнен в виде последовательно соединенных счетных ячеек, каждая из которых содержит триггер, регистр и сумматор, вход установки режима суммирования, вычитания которого соединен с выходом триггера, а первый и второй информационные

0 входы соединены с соответствующим выходами регистра, причем входы начальной ус- тановки регистров счетных ячеек объединены и являются второй шиной начальной установки, выход сумматора-явля5 ется выходом счетной ячейки, входы синхронизации триггеров счетных ячеек соединены с соответствующим выходами дешифратора, информационные входы объединены и являются входом блока вы0 числений, вход записи регистра является тактирующей шиной, а выходом блока вычислений является выход сумматора последней счетной ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1989 |

|

SU1690195A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Тригонометрический конвейерный преобразователь | 1989 |

|

SU1651300A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1785076A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1520659A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Функциональный аналого-цифровой преобразователь | 1990 |

|

SU1809531A1 |

Изобретение предназначено для осуществления экспоненциального ввода аналоговой информации в ЭВМ и может найти применение в приборостроении, управляющих и информационно-измерительных системах. Цель изобретения - повышение быстродействия преобразователя. Для этого в преобразователь содержащий компаратор 9, первый вход которого является входной шиной а второй вход соединен с выходом цифроаналогового преобразователя 8, введены дешифратор 2, счетчик 1. постоянные запоминающие устройства 3 и 4, мультиплексор 5, сумматор 6, буферный регистр 7, блок вычислений, выполненный в виде последовательно соединенных ячеек, каждая из которых имеет регистр, сумматор и триггер, причем выход счетчика 1 соединен с входом дешифратора 2 и входами постоянных запоминающих устройств 3,4, выходы постоянных запоминающих устройств 3,4 соединены с входами мультиплексора 5, выход мультиплексора 5 соединен с первым входом сумматора 6, с вторым входом которого соединен выход буферного регистра 7, выход сумматора 6 соединен с входом буферного регистра 7, вход цифроаналогового преобразователя 8 соединен с выходом буферного регистра 7 выходы дешифратора 2 соединены с входами синхронизации триггеров, входящих в блок вычислений, выход компаратора 9 соединен с входом управления мультиплексора 5 и входами данных триггеров, входящих в блок вычислений 1 ил О 00 о о ю

ехо.х.

| Анисимов А В и др Аналоговые и гибридные вычислительные машины, 1984 | |||

| с | |||

| Фальцовая черепица | 0 |

|

SU75A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-10-23—Публикация

1989-06-27—Подача