1

Изобретение относится к области цифровых вычислительных машин и дискретной автоматики.

Известно устройство для преобразования троичных чисел в десятичную систему счисления, принцип действия которого основан на превращении троичного кода в единичный, а затем в десятичный. Импульсы единицы или двойки каждого разряда превращаются в одну или несколько серий импульсов, причем количество этих серий равно количеству десятичных разрядов преобразуемого числа. Недостатком этого устройства является низкое быстродействие.

Цель изобретения - повыщение быстродействия устройства. Для этого десятичные вычитатели первой ступени соединены между собой шиной заема, входы уменьшаемого обоих вычитателей присоединены к соответствующим выходам двух старших девятиричных преобразователей, вход вычитаемого первого вычитателя и вход заема второго вычитателя присоединены к шине «нуль, а входы вычитаемого второго вычитателя присоединены к соответствующим выходам первого девятиричного преобразователя. На f-ой ступени i-f-1 Десятичных вычитателей последовательно соединены между собой цепями заемов, входы уменьшаемого старших t десятичных вычитателей присоединены к соответствующим выходам разности одноименных десятичных вычитателей предыдущей (t-1)-ой ступени, вход уменьшаемого младшего (г+1)-го вычитателя подключен к соответствующим выходам

(t+l)-ro девятиричного преобразователя, входы вычитаемого каждого десятичного вычитателя i-oii ступени, кроме первого, присоединены к соответствующим выходам разности соседних более старших десятичных вычитателей

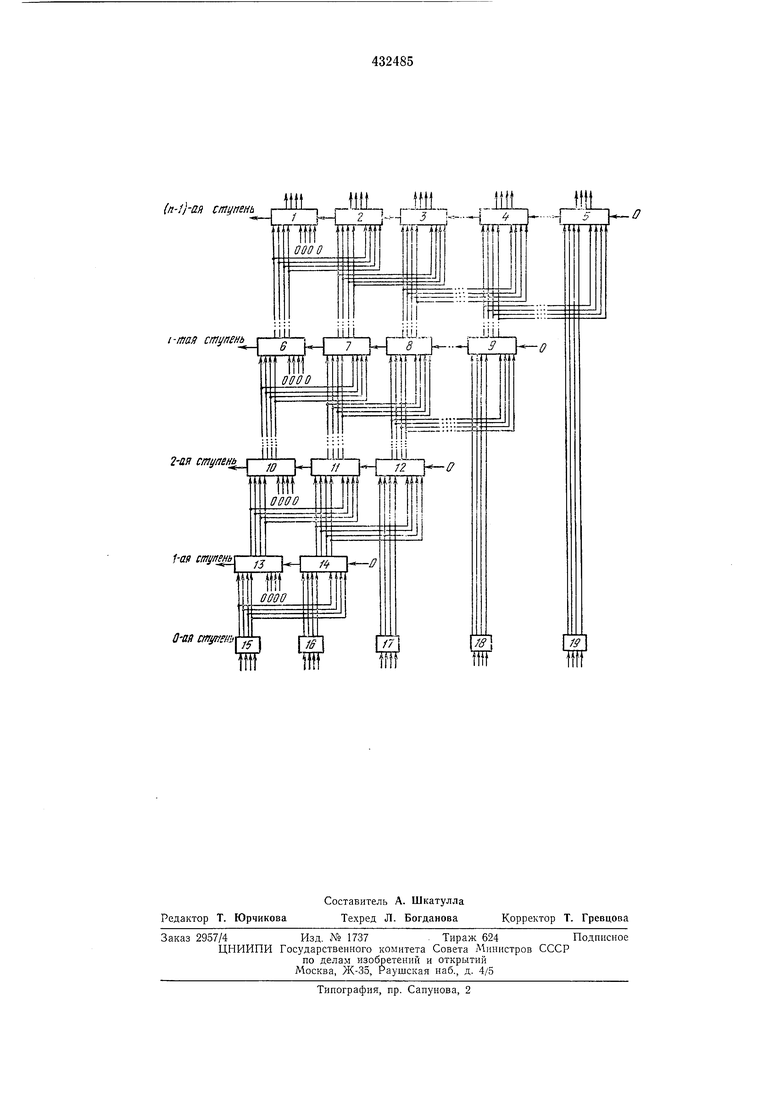

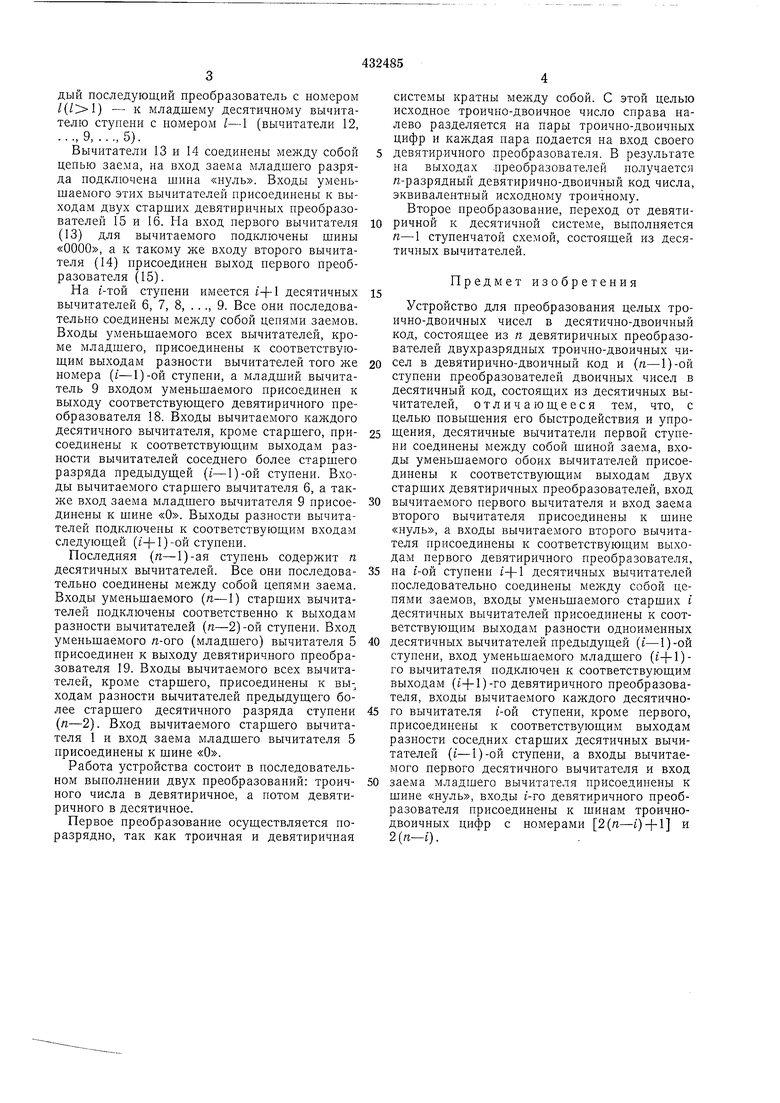

(i-1)-ой ступени, а входы вычитаемого первого десятичного вычитателя и вход заема младшего вычитателя присоединены к щине «нуль. Входы i-ro девятприч ого преобразователя присоединены к щинам троично-двоичных цифр с номерами 2(п-О + Ч и 2(п-i). Блок-схема предлагаемого устройства, показанная на чертеже, содержит вычитатели 1 - 14 и девятиричные преобразователи 15-19. Последние образуют нулевую ступень

на входе устройства. Выходы нулевой ступени подключены к (п-1)-ой последовательно соединенным ступеням составленным из десятичных вычитателей. Каждый девятмричный преобразователь нулевой ступени подключен

входами к соответствующим шинам троичнодвоичных цифр, а выходами к входам десятичных вычитателей для соответствующего уменьщаемого. При этом два старших преобразователя (15 и 16) присоединены к входам

вычитателей 13 и 14 первой ступени, а каждый последующий преобразователь с номером /(/) - к младшему десятичному вычитателю ступени с номером /-1 (вычитатели 12, ..., 9, .... 5).

Вычитатели 13 и 14 соединены между собой цепью заема, на вход заема младшего разряда подключена шина «нуль. Входы уменьшаемого этих вычитателей присоединены к выходам двух старших девятиричных преобразователей 15 и 16. На вход первого вычитателя (13) для вычитаемого подключены шины «0000, а к такому же входу второго вычитателя (14) присоединен выход первого преобразователя (15).

На t-той ступени имеется t+l десятичных вычитателей 6, 7, 8, .. ., 9. Все они последовательно соединены между собой цепями заемов. Входы уменьшаемого всех вычитателей, кроме младшего, присоединены к соответствуюш,им выходам разности вычитателей того же номера (i-1)-ой ступени, а младший вычитатель 9 входом уменьшаемого присоединен к выходу соответствующего девятиричного преобразователя 18. Входы вычитаемого каждого десятичного вычитателя, кроме старшего, присоединены к соответствующим выходам разности вычитателей соседнего более старшего разряда предыдущей (i-1)-ой ступени. Входы вычитаемого старшего вычнтателя 6, а также вход заема младшего вычитателя 9 присоединены к шине «О. Выходы разности вычитателей подключены к соответствующим входам следующей (г+1)-ой ступени.

Последняя (п-1)-ая ступень содержит п десятичных вычитателей. Все они последовательно соединены между собой цепями заема. Входы уменьщаемого (п-I) старших вычитателей подключены соответственно к выходам разности вычитателей (п-2)-ой ступени. Вход уменьшаемого п-ого (младшего) вычитателя 5 присоединен к выходу девятиричного преобразователя 19. Входы вычитаемого всех вычитателей, кроме старшего, присоединены к вы; ходам разности вычитателей предыдущего более старшего десятичного разряда ступени (п-2). Вход вычитаемого старщего вычитателя 1 и вход заема младшего вычитателя 5 присоединены к шине «О.

Работа устройства состоит в последовательном выполнении двух преобразований: троичного числа в девятиричное, а потом девятиричного в десятичное.

Первое преобразование осуществляется поразрядно, так как троичная и девятиричная

системы кратны между собой. С этой целью исходное троично-двоичное число справа налево разделяется на пары троично-двоичных цифр и каждая пара подается на вход своего

девятиричного преобразователя. В результате на выходах преобразователей получается я-разрядный девятирично-двоичный код числа, эквивалентный исходному троичному.

Второе преобразование, переход от девятиричной к десятичной системе, выполняется п-1 ступенчатой схемой, состоящей из десятичных вычитателей.

Предмет изобретения

Устройство для преобразования целых троично-двоичных чисел в десятично-двоичный код, состоящее из п девятиричных преобразователей двухразрядных троично-двоичных чисел в девятирично-двоичный код и (п-1)-ой ступени преобразователей двоичных чисел в десятичный код, состоящих из десятичных вычитателей, отличающееся тем, что, с целью повышения его быстродействия и упрощения, десятичные вычнтатели первой ступени соединены между собой шиной заема, входы уменьшаемого обоих вычитателей присоединены к соответствующим выходам двух старших девятиричных преобразователей, вход

0 вычитаемого первого вычитателя и вход заема второго вычитателя присоединены к шине «нуль, а входы вычитаемого второго вычитателя присоединены к соответствующим выходам первого девятиричного преобразователя,

5 на i-ой ступени i+1 десятичных вычитателей последовательно соединены между собой цепями заемов, входы уменьшаемого старших t десятичных вычитателей присоединены к соответствующим выходам разности одноименных

0 десятичных вычитателей предыдущей (i-1)-ой ступени, вход уменьшаемого младшего (t+l)го вычитателя подключен к соответствующим выходам (t+l)ГО девятиричного преобразователя, входы вычитаемого каждого десятичного вычитателя t-ой ступени, кроме первого, присоединены к соответствующим выходам разности соседних старших десятичных вычитателей (i-1)-ой ступени, а входы вычитаемого первого десятичного вычитателя и вход

0 заема младшего вычитателя присоединены к шине «нуль, входы i-ro девятиричного преобразователя присоединены к шинам троичнодвоичных цифр с номерами 2{п-1) + 4 и 2(n-i).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования двоичного кода в десятичный | 1976 |

|

SU633013A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДЕСЯТИЧНО- ДВОИЧНЫХ ЧИСЕЛ В ТРОИЧНО-ДВОИЧНЫЙ КОД | 1972 |

|

SU436343A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Разряд троичного комбинационного вычитателя | 1973 |

|

SU450165A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

| Преобразователь двоично-десятичного кода времени в двоичный код | 1988 |

|

SU1536510A1 |

Даты

1974-06-15—Публикация

1972-06-20—Подача