(54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ

ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Сумматор-вычитатель | 1981 |

|

SU993254A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Одноразрядный десятичный сумматор | 1975 |

|

SU690479A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство преобразования двоичного кода в десятичный | 1976 |

|

SU633013A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1974 |

|

SU526885A1 |

Изобретение относится к области вычислительной техники. Устройство может найти применение при выполнении операции вычитания одного числа (меньп1его) из другого (большего), представленных в двоично-десятичном прямом коде 8-4-2-1. Известно устройство для сложения вычитания десятичных чисел 1. В нем операция вычитания производится сложением уменьшаемого с отрицательным числом вычитаемого, предcтaвлeнны дополнительным кодом, с последую ii.ieft кг ррекиией результата для получения его в двоично-десятичном коде. Недостатком известного устройства является необходимость дополнительного преобразования чисел из прямого кода в обратный. Это с.чижает скорость обработки информации, ус.;и) схему. В тех случаях, когда уменьшае мое бо.1ьше вычитаемого (т.е. из большего числа необходимо вычесть меньшее) использование сумматоров-вычитателей нерационально. Известны различные модификаьйии двоичны.х сумматоров-вычитателей на логических эле ментах ИЛИ-НЕ или в общем случае ИЛИ-НЕ и ИЛИ 2. Однако это устройство не позволяет вычитать числа в двоично-десятичном коде. Наиболее близким по технической сущности к изобретению является устройство для вычитания десятичных чисел, содержащее тетра ду одноразрядных двоичных вычитателей, причем выход вычитателя первого.разряда тетрады соединен с выходом устройства, а выходы вычитателей второго, третьего и четвертого разрядов тетрады соединены с входами схемы коррекции 3. Недостатком такого устройства является сложность построения схемы коррекции, выполненной на двух одноразрядных полусумматорах и на одном сумматоре, на котором происходит сложение трех величин: выхода вычитателя четвертого разряда тетрады, выхода сигнала заема его и сигнала переноса от второго полусумматора схемы коррекции. Цель изобретения - повыщение быстродействия устройства. Это достигается тем, что схема коррекции выполнена на двух полусумматорах и элементе 2И-ИЛИ. Причем выходы инверсного к прямого значений сигналов заема вычитателя четвертого разряда тетрады подключены к первому и второму входам эдемента 2И-ИЛИ, выход прямого значения сигнала заема вычитателя четвертого разряда тетрады соединен. кроме того, с первым входом первого полусуммато;)а, второй вход которого подключен к выходу вычитателя второго разряда тетрады. Выход переноса первого полусумматора соединен с первым входом второго полусумматора, второй вход которого соединен с выходом вычитателя третьего разряда тетрады. Выход переноса второго полусумматора подключен к третьему входу элемента 2И-ИЛИ, четвертый и пятый входы которого соединены с выходом вычитателя четвертого разряда тетрады. Выходы сумм полусумматоров и выход элемента 2И-ИЛИ соединены с выходами устройства.

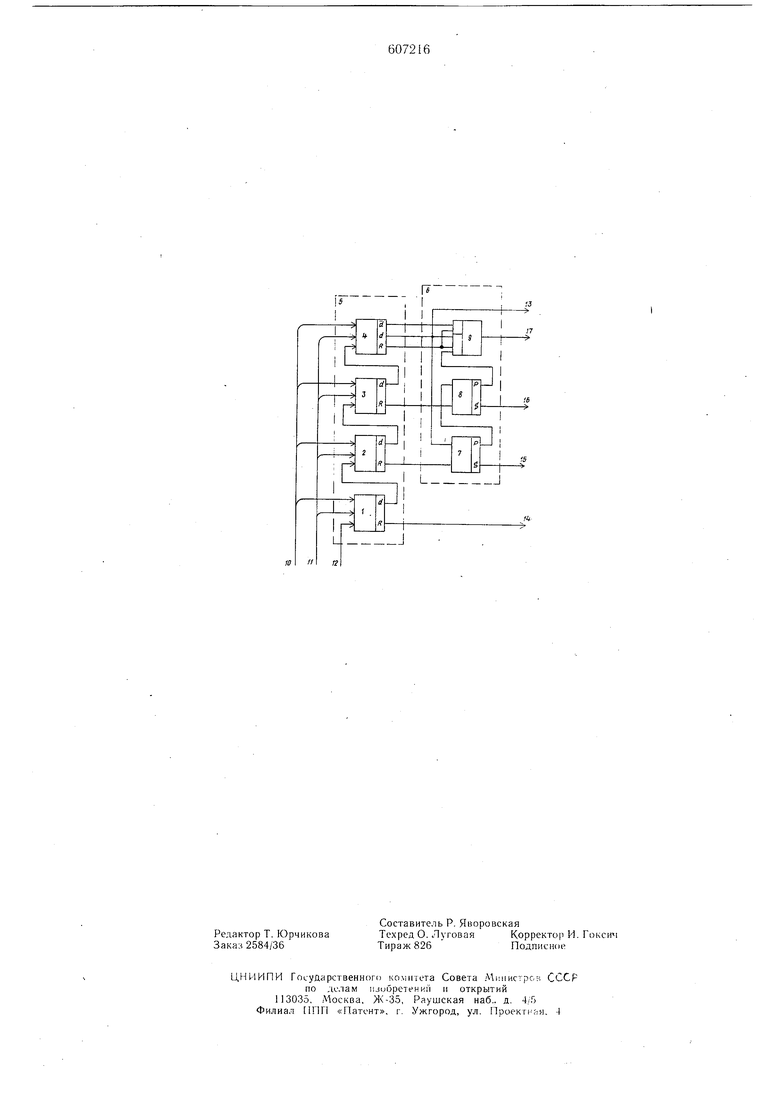

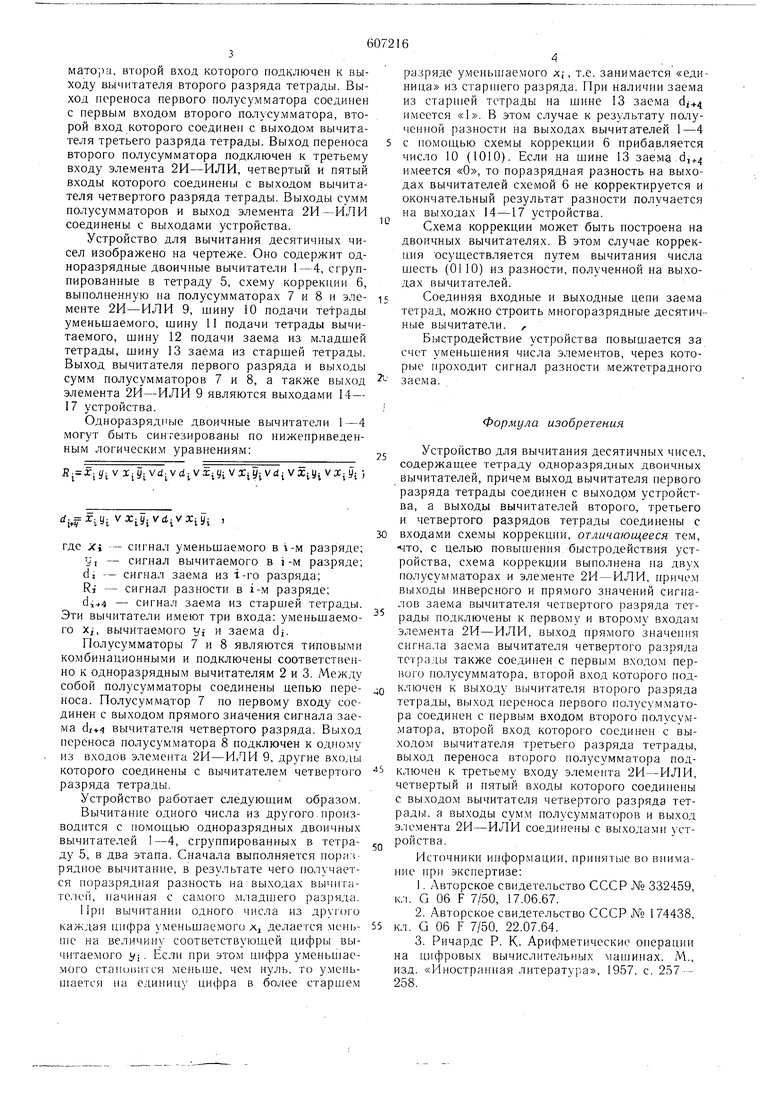

Устройство для вычитания десятичных чисел изображено на чертеже. Оно содержит одноразрядные двоичные вычитатели 1-4, сгруппированные в тетраду 5, схему коррекции 6, выполненную на полусумматорах 7 и 8 и элементе 2И-ИЛИ 9, шину 10 подачи тetpaды уменьшаемого, шину 11 подачи тетрады вычитаемого, шину 12 подачи заема из младшей тетрады, шину 13 заема из старшей тетрады. Выход вычитателя первого разряда и выходы сумм полусумматоров 7 и 8, а также выход элемента 2И-ИЛИ 9 являются выходами 14- 17 устройства.

Одноразрядные двоичные вычитатели 1-4 могут быть синтезированы по нижеприведенным логическим уравнениям:

..Vd- Vd;VX IJiVX y Vd VXi l /X li

i.

где х - сигнал уменьшаемого в i-м разряде;

у, - сигнал вычитаемого в i-м разряде;

di -- сигнал заема из i-ro разряда;

Rj - сигнал разности в i-м разряде;

- сигнал заема из старшей тетрады. Эти вычитатели и.меют три входа; уменьшаемого Xj, вычитаемого yi и заема di.

Полусумматоры 7 и 8 являются типовыми комбинационными и подключены соответственно к одноразрядным вычитателям 2 и 3. Между собой полусумматоры соединены цепью переноса. Полусумматор 7 по первому входу соединен с выходом прямого значения сигнала заема d/+4 вычитателя четвертого разряда. Выход переноса полусумматора 8 подключен к одному из входов элемента 2И-ИЛИ 9, другие входы которого соединены с вычитателем четвертого разряда тетрады.

Устройство работает следующим образо.м.

Вычитание одного числа из другого,производится с гюмошью одноразрядных двоичных вычитателей 1-4, сгруппированных в тетраду 5, в два этапа. Сначала выполняется поргкь рядное вычитание, в результате чего получается поразрядная разность на вы.ходах вычитатс.чей, начиная с самого младн:его разряда.

При вычитании одного числа из другого каждая uuppa уменьшаемого Лд делается меньше на величину соответствующей цифры вычитаемого 4i. Если при этом цифра уменьшаемого становится меньн.1е, чем нуль, то уменьшается на единицу цифра в более старшем

разряде уменьшаемого х;, т.е. занимается «единнца из стари1его разряда. При наличии заема из стари ей тетрады на шине 13 заема di+ имеется «1. В этом случае к результату полученной разности на выходах вычитателей 1-4 с помощью схемы коррекции 6 прибавляется число 10 (1010). Если на шине 13 заема,d,+4 и.меется «О, то поразрядная разность на выходах вычитателей схемой 6 не корректируется и окончательный результат разности получается

на выходах 14-17 устройства, ,,- Схема коррекции может быть ностроена на

двоичных вычнтателях. В этом случае коррекция осуществляется путем вычитания числа шесть (0110) из разности, полученной на выходах вычитателей.

Соединяя входные и выходные цепи заема тетрад, можно строить многоразрядные десятичные вычитатели. f

Быстродействие устройства повышается за счет уменьшения числа элементов, через которые проходит сигнал разности межтетрадного

заема.

Формула изобретения

Устройство для вычитания десятичных чисел, содержащее тетраду одноразрядных двоичных вычитателей, приче.м выход вычитателя первого разряда тетрады соединен с выходом устройства, а выходы вычитателей второго, третьего и четвертого разрядов тетрады соединены с

входами схемы коррекции, отличающееся тем, что, с целью повышения быстродействия устройства, схема коррекции выполнена на двух полусумматорах и элементе 2И - ИЛИ, приче.м выходы инверсного и прямого значений сигналов заема вычитателя четвертого разряда тетрады подключены к первому и второму входам элемента 2И-ИЛИ, выход прямого значения сигнала заема вычитателя четвертого разряда тетрады также соединен с первым входом первого полусумматора, второй вход которого подключен к В1 1читателя второго разряда тетрады, выход переноса первого полусумматора соединен с первым входом второго полусумматора, второй вход которого соединен с выходом вычитателя третьего разряда тетрады, выход переноса второго полусумматора подключен к третьему входу элемента 2И-ИЛИ, четвертый и пятый входы которого соединены с выходом вычитателя четвертого разряда тетрады, а выходы сум.м полусумматоров и выход элемента 2И - ИЛИ соединены с выходами устройства.

Источники информации, принятые во внимание при экспертизе;

Авторы

Даты

1978-05-15—Публикация

1975-04-15—Подача