1

Изобретение может быть использовано в устройствах автоматики и вычислительной техники для преобразования целых двоичных чисел в десятичные.

Известны устройства l преобразования целых двоичных чисел в десятичные, использующие комбинационные схемы, осуществляющие сложение весов двоичных разрядов преобразуемого числа в двоичнодесятичной системе счисления.

Наиболее близкое техническое решение к предложенному 2 содержит П ступеней преобразования и h дешифраторов.

Однако, в связи с тем, что каждый 1 -ный разряд двоичного числа в своем двоично-десятичном эквиваленте представляется числом с разрядностью 4(CiEg 2 + l), и сам процесс двои«ьно-десятичного суммирования требует наличия схем определения десятичного переноса, то для реализации преобразовате- лей двоичных чисел большой разрядности приходится использовать большое коянчество логических элементов.

Целью изобретения является упрошение устройства.

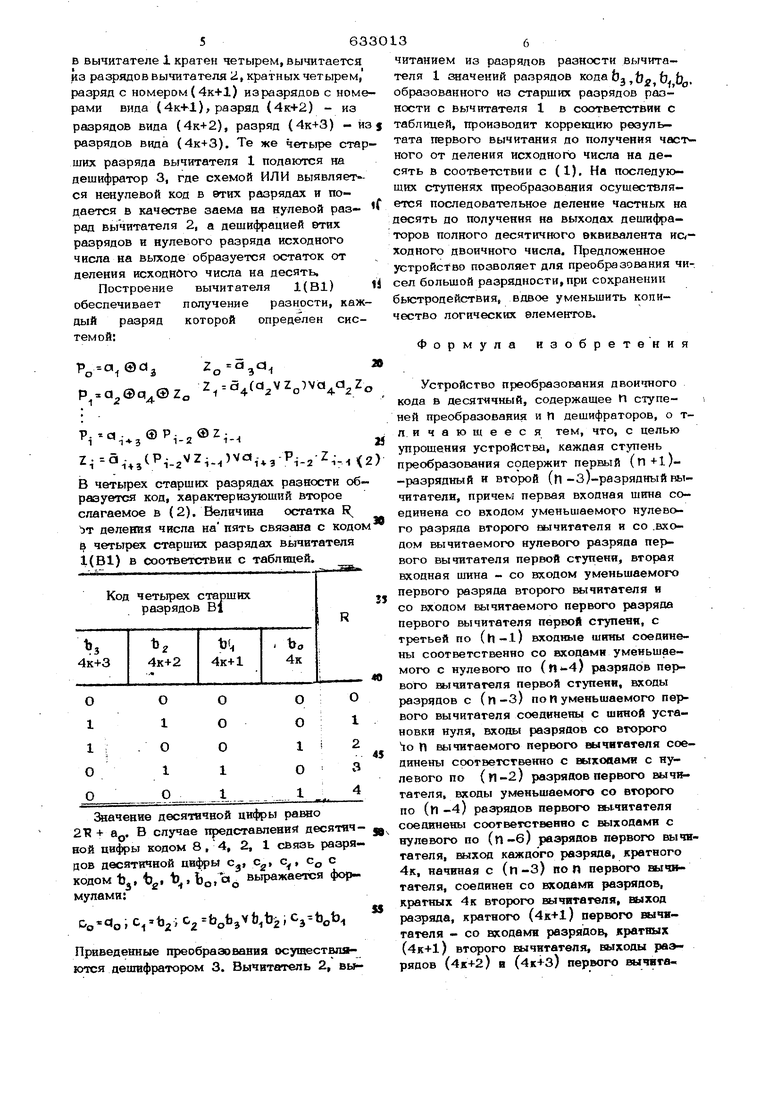

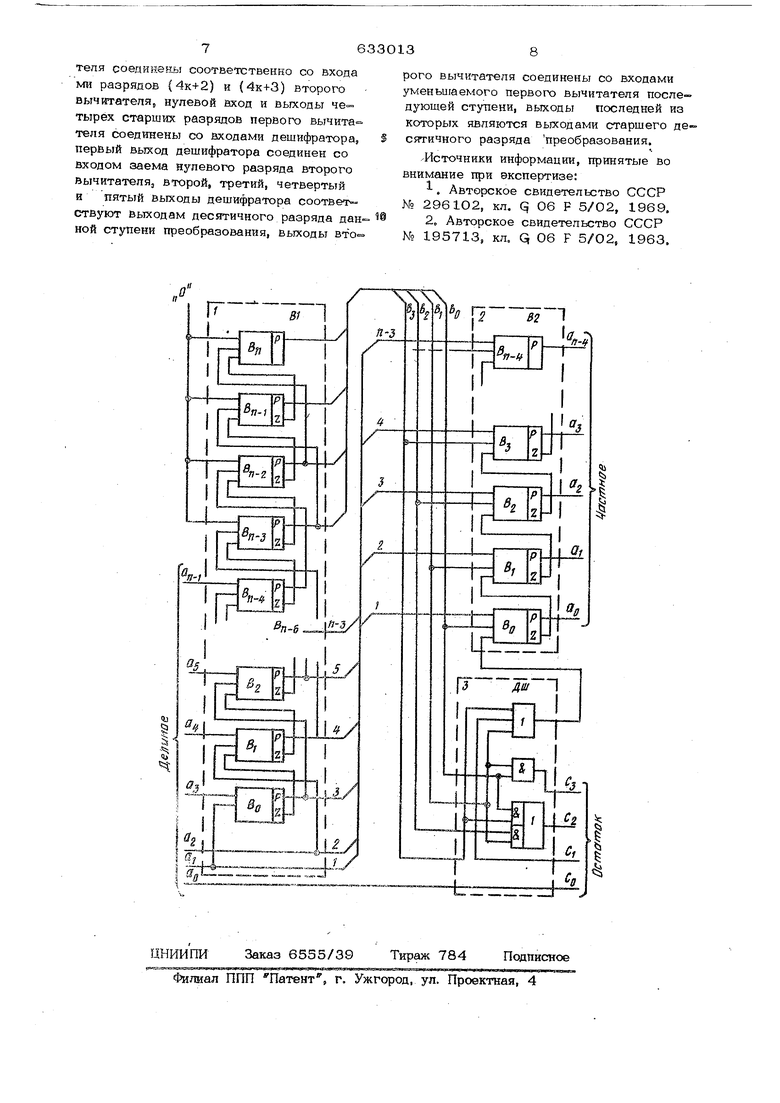

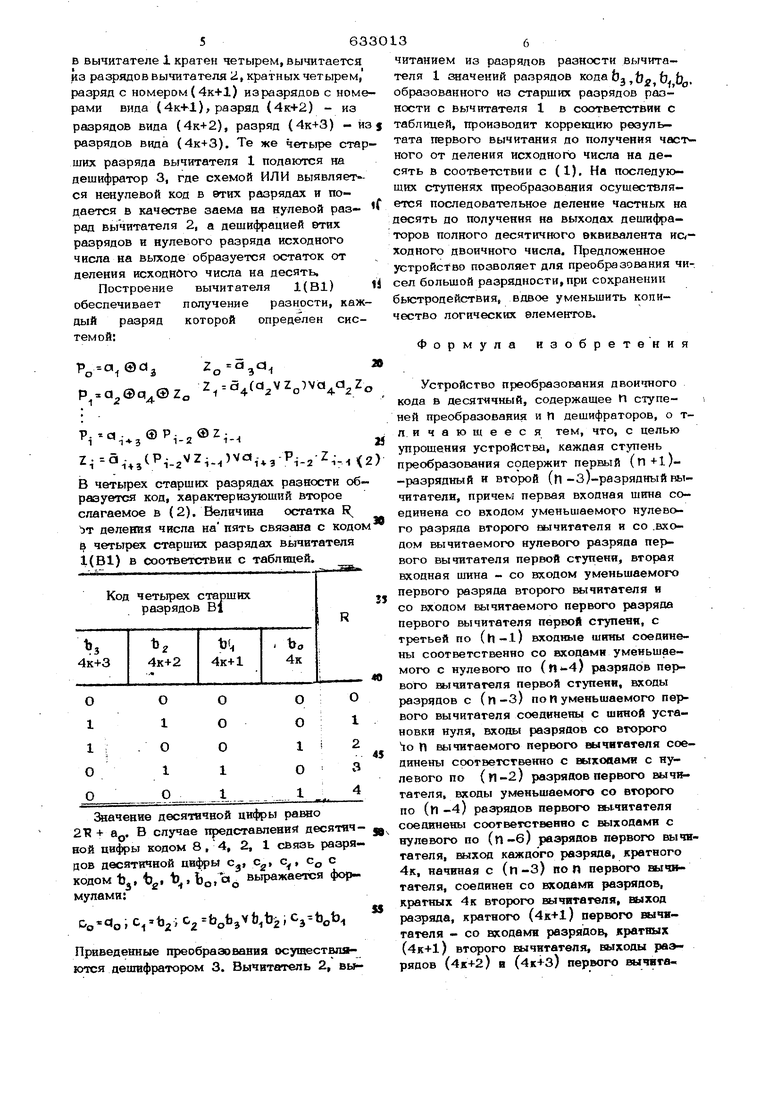

Указанная цель достигается тем, что каждая ступень преобразования содержит первый (я+1)-разрядный и второй (П-З) -разрядный вычитатели, причем первая входная шина соединена со входом уменьшаемого нулевого разряда второго вычятателя и со входом вычитаемого нулево го разряда первого вы читателя первой ступени, вторая входная шина - со вхооом уменьшаемого первого разряда второго вычитателя и со входом вычитаемого первого разряда первого вы читателя пербой втупени, с третьей no(n-l) входные шины соединены соответственно со входами уменьшаемого с нулевого по (h-4) разрядов первого клчитателя первой ступени, вхош 1 разряаовс(п -З) по П уменьшаемого первого вычитателя соединены с шиной устано. ки иуня, входы разрядов со второго по П вычитаемого первого вычитателя соединены соответственно с выходами с нулевого по in-2) разрядов первого вычитателя, вхо6ды уменьшаемого со второго по (п-4) разрядов первого вычитателя соединены соотэетственно с выходами с нулевого по (п-6) разрядов первого вычитателя выход каждого разряда, кратного 4к, начиная с (П-З) по п первого вычитателя соединен со входами разрядов, кратных 4к второго вычитателя, выход разряда, кратного (4к+1) первого вычитателя входами разрядов, кратных (4к+1) второго вычитателя, выходы разрядов (4к+2) и (4к+3) первого вычитателя соединены соответственно со входами .разрядов {4К+2) и (4к+3) второго вычитателя, нулевой вход и вьгходы четырех старших разрядов первого вычитателя соединены со входами дешифратора, первый выход деши(| атора соединен со входом заема нулевого разряда второго вычитателя, второй, третий, четвертый и пятый выходы дешифратора соответствуют выходам десятичного разряда данной ступени пре образователя, вьгходы второго вычитате- ля соединены со входами уменылаемого первого вычитателя последующей ступени, выходы последней из которых являются выходами старшего десятичного разряда преобразования. На чертеже представлена функциональная схема одной ступени преобразования, содержащая: первый ()-рЁЮрядный вычитатель 1{В1),, второй (п-З)-разрядный вычктатель 2(В2), дешифратор 3(ДШ). На чертеже приняты обозначения: -одноразрядный вы читатель, 0 . -соответствующие разряды делимого и частного, t)- -разряды корректирующего кода. С,- -разряды двоично-десятичного кода ос- татка. Преобразование осуществляется последовательным делением на десять: на первой ступени - исходного числа, на следующей - полученного частотного и т.д. до получения в виде частного значения старшего разряда десятичного числа. При ВТОМ, количество логических элементов в каждой ступени деления определяется раз рядностью образованного рааее частного, количество ступеней деления на единицу меньше разрядности десятичного числа. Определена резулг/гата.деления в каждой ступени- происходит в два этапа. На первом этапе пооизводится вычисление двоич ного числа, которое,будучи умноженным н пять, совпадает в своих млвдших рварядах со значениями разрядов с первого по (n-l) делимого, а, во всех, более стар 34 их разрядах, имеет нулевые значения. то достигается вычитанием из каждого азряда делимого, начиная с третьего, начения полученного на д разряда ранее результата вычитания, при этом из ретьего и четвертого разрядов делимого вычитаются соответственно первый и второй разряды делимого. Результатом вычитания будет число, имеющее вид .А ,((-R) по nis где частное от деления исходного числа на десять; - остаток от деления уменьшенного вдвое исходного числа на пять; k со . Второе слагаемое представляет собой периодическую двоичную последовательность, поэтому результат вычитания в своих старших разрядах однозначно определяет остаток и код, позволяющий скорректировать результат до получения частного. На втором этапе jBHHHTaHHeM корректирующего кода из результата вычислений первого этапа формируется двоичное число, являющееся Ч€ютным от деления исходного числа на десять. Устройство работает следующим образом. На вход первой ступени подается исходное двоичное число; на одном выходе первой ступени образуется младшая цифра десятичного эквивалента, на другом - частное от деления исходного числа на десять в двоичном представлении, которое подаётся va вход следующей ступени деления и т.д., выходы последней ступени преобразования - две старшие ци(ы десятичного эквивалента. Каждая ступень преобразования (деления) состоит из двух двоичных вычитателей и дешифратора. (Н-З) старших разряда П -разрядного двоичногчэ числа подаются в качестве уменьшаемого на ( П-З) младших разряда вычитателя 1, на четыре старших разрада подаются нули, в качестве вычитаемого на нулевой подается с , на первый -е исходного числа, а на каждый из последующих образовавшийся на два разряда ранее -результат вычитания. На вычитатель 2 в качестве уменьшаемого подается число, два младших которого -О и исходного числа, а остальные (п-5) разрядов-(h-5j младших разрада разности вычитателя 1 Вычитаемое 2 формвруетея вз ч&тщзек старших раерЛаов разности ,ro разряд, номер которого 5 в вычитателе 1 кратен четырем, вычитаетс из разрядов вычитателя 2, кратных четыре разряд с номером (4к+1) изразрядов с но рами вида {4к-Ы), разряд (4к+2) - из разрядов вида (4к+2), разряд (4к+3) разрядов вида (4к+3). Те же четыре ст ших разряда вычитателя 1 подаются на дешифратор 3, где схемой ИЛИ выявпяет ся ненулевой код в этих разрядах и подается в качестве заема на нулевой раз рад вычитателя 2, а дешифрацией втих разрядов и нулевого разряда исходного числа на выходе образуется остаток от деления исходного числа на десять. Построение вычитателя 1(В1) обеспечивает получение разности, ка дый разряд которой определен сис темой; 4(a.,(ci2 Р a,. а-,,®Р. { Р V Z ) V О - - Р Z Zi-«.4, 1 З четырех старших разрядах разности об разуется код, характеризуюший второе слагаемое в (2). Величина остатка R Ът деления числа на пять связана с кодо в четырех старших разрядах вычитателя 1(В1) в соответствии с таблицей. Код четырех старших разрядов в НОЙ цифры кодом 8 , 4, 2, I связь разрядов десятичной цифры с, Cg, с, Сд с J ot выражается фор- кодом Ъ, bgi ti,, Ь мулами: .b,;c rb bjVb b iS-tobi ««oiS Приведенные преобразования осушествлян ются дешифратором 3. Вычнтатель 2, вы136читанием из рааряпов разности вычитателя 1 значений разрядов кода &, Ь Ь Ь образованного из старших разрядов рвзности с вычитателя I в соответствии с таблицей, производит коррекцию реоультата первого вычитания до получения част ного от деления исходного числа на десять в соответствии с (I), На последующих ступенях преобразования осушествляет ся последовательное деление частных на десять до получения на выходах дешифраторов полного десятичного эквивалента ис ходного двоичного числа. Предложенное устройство позволяет для преобразования чи-. сел большой разрядности, при сохранении быстродействия, вдвое уменьшить количество логических элементов. Формула изобретения Устройство преобразования двоичного кода в десятичный, содержащее Ч ступе- ней преобразования и h дешифраторов, о тличающееся тем, что, с целью упрощения устройства, каждая ступень преобразования содержит первый (n+l)-разрядный и второй (м-3)-разрядный вычитателн, причем первая входная шина соединена со входом уменьшаемого нулевого разряда вгорого вычитателя и со .входом вычитаемого нулевого разряда nej вого вычитателя первой ступени, вторая входная шина - со входом уменьшаемого первого разряда второго вычнтателя и со входом вычитаемого первого разряда первого вычитателя первой ступени, с третьей по (h-.l) входные шины соединены соответственно со входами уменьшаемого с нулевого по () разрядов nei вого вы читателя первой ступени, входы разрядов с (п-з) по и уменьшаемого первого вычитателя соединены с шиной установки нуля, входы разрядов со второго 10 П вычитаемого первого вычигателя соединены соответственно с выходами с нулевого по (я-2) разрядов первого выч тателя, входы уменьшаемого со второго по (м -4) разрядов первого вычитатепя соединены соответственно с выходами с нулевого по (п-б) разрядов первого вычитателя, кяход каждого разряда, кратного 4к, начиная с (п-З) по П первого вычитателя, соединен со входами раэряпов, кратных 4к второго вычитатепя, выход разряда, кратного (4к+1) первого вычнтателя - со вэсодамн разрядов, кратных (4к+1) второго вычнтателя, выходы разрядов (4к+2) в () первого вычета

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЦЕЛЫХ ТРОИЧНО-ДВОИЧНЫХ ЧИСЕЛ В ДЕСЯТИЧНО-ДВОИЧНЫЙКОД | 1972 |

|

SU432485A1 |

| Устройство для деления | 1979 |

|

SU773618A1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления десятичных чисел | 1989 |

|

SU1688239A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

Авторы

Даты

1978-11-15—Публикация

1976-05-21—Подача