ниэации ввода комбинированной коррекции, вторые входы которых соединены соответственно с выходом второго элемента ИЛИ и выходом третьего

элемента ИЛИ, а выходы - с соответствующими входами шестого элемента ИЛИ , выход которого является выходом блока синхронного ввода комбинирован ной коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания кодов времени | 1983 |

|

SU1124287A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Устройство для вычитания двоичнодесятичных кодов времени | 1976 |

|

SU595730A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1974 |

|

SU526885A1 |

| Одноразрядный десятичный сумматор- ВычиТАТЕль | 1977 |

|

SU807275A1 |

| Устройство для вычитания десятичных чисел | 1975 |

|

SU607216A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

УСТРОЙСТВО ДЛЯ ВЬИИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ, содержащее первый и второй одноразрядные двоичные вычитатели, регистр промежуточной разности, триггер, элементы И и элементы задержки, первый и второй входы первого одноразрядного двоичного вычитателя соединены с шинами первого и второго операндов устрой-: ства соответственно, выход разности, первого одноразрядного двоичного вычитателя соединен с входом регистра промежуточной разности, выход которого подключен к первому входу второго одноразрядного двоичного вычитателя, выход заема первого одноразрядного двоичного вычитателя через первый элемент задержки подключен к третьему входу того же одноразрядного двоичного вычитателя и первому входу первого элемента И, второй вход которого соединен с первой шиной синхронизации устройства, а выход подключен к единичному входу триггера, нулевой вход которого соединен с второй шиной синхронизации устройства, единичный выход триггера подключен к первому входу второго элемента И, выход которого соединен с вторым входом второго одноразрядного двоичного вычитателя, выход разности которого соединен с выходной шиной устройства, а выход заема через второй элемент задержки соединен с третьим входом того же одноразрядного двоичного вьмитателя, о тличающееся тем, что, с целью расширения функциональных возможностей путем осуществления вычитания кодов времени, оно содержит блок синхронного ввода комбинированной коррекции, вход которого соединен с третьей шиной синхронизации устройства, а выход подключен к второму входу второго элемента И, причем блок синхронного ввода комбинированной коррекции содержит четырехразрядный регистр сдвига, четырехразрядный двоичный счетчикj преобразователь двоичного кода в десятичный, элементы И и ИЛИ, причем первый вход первого элемента ИЛИ соединен с входом блока синхронного ввода ком- § бинированной коррекции, второй вход (Л первого элемента ИЛИ соединен с выходом старшего разряда четырехразрядного регистра сдвига, первым входом второго элемента ИЛИ и входом четырехразрядного двоичного счетчика, выход первого элемента ИЛИ соединен с входом четырехразрядного регистра сдвига, выход второго разряда которого соединен с вторым входом второго 4 элемента ИЛИ и первым входом третьего элемента ИЛИ, выход третьего четырех:о at) р азрядного регистра сдвига соединен с вторым входом третьего элемента 4 ИЛИ, ВЫХОДЫ:разрядов четырехразрядного д воичИого счетчика соединены с .соответствующими входами преобразователя двоичного кода в десятичный, выход ста ршего разряда которого соединен с шинами сброса четырехразрядного регистра сдвига и четырехразрядного двоичного счетчика, входы четвертого и пятого элементов ИЛИ соединены с выходами соответствующих раз- рядов преобразователя двоичного кода в десятичный, выходы четвертого и пятого элементов ИЛИ подключены к первым входам соответственно первого и второго элементов И блока синхро

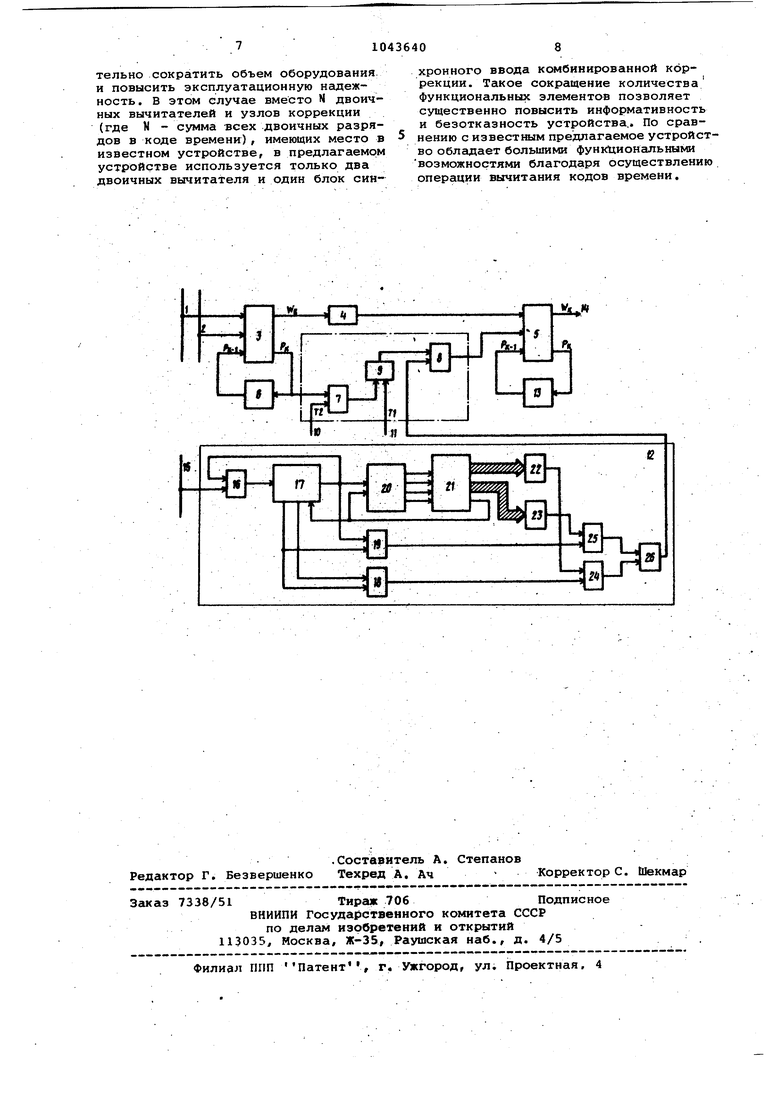

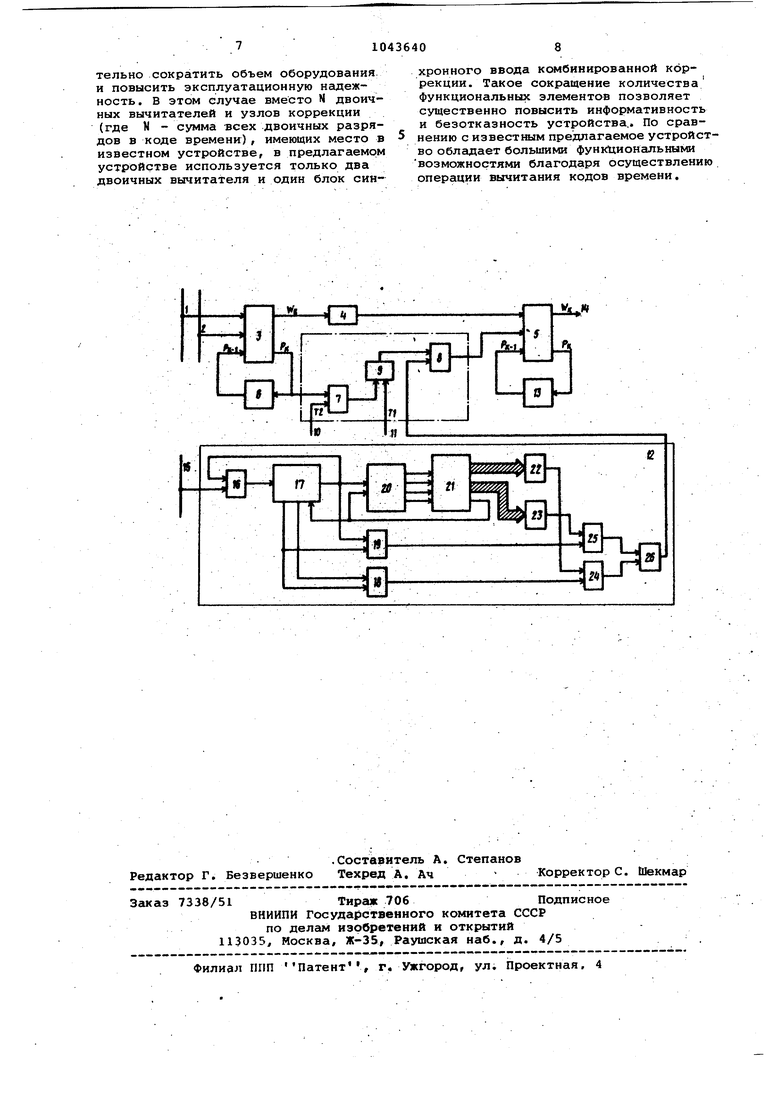

Изобретение относится к вычислительной технике и может- быть исполь зовано в специализированных вычислительных устройствах, работающих в реальном масштабе времени. Известно устройство для вычитани двоично-десятичных кодов времени, которое содержит блоки вычитания ко дов десятых долей секунд, единиц секунд, десятков секунд, единиц минут, десятков , единиц часрв и десятков часов, причем выход заема каждого из этих блоков вычитания подключен к входу заема последующего блока. Это устройство осуществля . ет операцию вычитания кодов заданно и текущего времени, представленных в двоичнотдесятичном коде. В устрой стве. использован параллельный спосо обработки информации, когда операция вычитания каждого двоично-десятичного разряда кодов осуществляется с помощью отдельного блока вычитания Недостатком этого устройства является сложность конструкций. Наиболее близким к изобретению является устройство для вычитания довично-десятичных кодов, которое содержит первый и второй одноразряд ные .сумматоры, входной формировател инверсного кода, блок анализа резуль тата сложения, блок коррекции и выходной формирователь инверсного код с соответствующими .связями. Блок . коррекции содержит элементы И и ИЛИ и регистр сдвига, обеспечивающие формирование корректирующего кода для правильного выполнения операций вычитания (или сложения) при переполнении кода в тетрадах. Устройств может испольоваться для выполнения операций вычитания и сложения над .числами, представленными двоично-десятичными кодами 2J . . Однако известное устройство не позволяет производить операцию вычитания двоично-десятичных кодов времени, так как этот код являетрй комбинированным, где наряду с кодом тетрад (разряды единиц, десятков, сотен мил11исекунд и разряды единиц секунд,минут и часов)имеет место код трисщ (разряды десятков секунд и минут) , для правильного выполнения операций вычитания которых требусгтся корректирующий код,- отличный от кода коррекции тетрад. Кромеч того, для выполне-ния только операций вычитания известное устройство обло1дае.т некоторой избыточностью функциональных-элементов, так как использование, одноразрядных двоичных вычитат.елей, которые по структуре аналогичны одноразряднЕлм- двоичным . сумматорам, позволяет исключить блоки формирования инверсии на входе и выходе устройства. . Цель изобретения - расширение функциональных возможностей устройства для вычитания двоично-десятичных кодов путем вычитгшия кодов времени. Указанная цель достигаетсятем, что устр.ойство .для вычитания двоично-десятичных кодов,содержащее первый и второй одноразрядные двоичные вычитатели, регистр промежуточной разности, триггер, элементы И и элементы задержки, первый и .второй, входы Первого о/1НоразрядногО двоичного вычитателя соединены с шинами перЬого и второго операндов устройства соответственно, выход разности первого одноразрядного двоичного вычитателя соединен с входом регистра промежуточной разности, выход которого под-, ключен к первому входу второго одноразрядного двоичного вычитателя,выход заема первого одноразрядного .двоичного вычитателя через первый злеАент задержки подключен к третьему входу того же одноразрядного двоичного вычитателя и первому входу первого элемента И,, второй вход которо- . го соединен.с первой шиной синхронизации устройства, а выход п.одключен к единичному входу триггера, нулевой вход KOTOpojo соединен с второй шиной синхронизации устройства, единичный выход триггера подключен к первому входу второго элемента И, выход которого соединен с вторым .входом второго одноразрядного двоичного вычитателя, выход разности которого соединен с выходной шиной устройства, а выход заема через второй элемент задержки соединен с третьим входом того же одноразрядного двоичного вычитателя, содержит блок синхронного ввода комбинированной коррекции. вход которого соединен с третьей синхронизации устройства, а выход подключен к второму входу ВТОрого элемента И, причем блок синхрон ного ввода комбинированной коррекций содержит четырехразрядный регистр сдвига, четырехразрядн ый двоичный счетчик, преобразователь двоичного .кода в десятичный, элементы И и ИЛИ, причем первый вход первого элементаИЛИ соединен с входом блока синхрон- ного.ввода комбинированной коррекции - второй вход первого элемента ИЛИ сое динен с выходом старшего разряда четырехразрядного регистра сдвига, пер вым входом второго элемента ИЛИ и входом четырехразрядного двоичного счетчика, выход первого элемента ИЛИ соединен с входом четырехразрядного регистра сдвига, выход, второго разряда которого соединен с вторьил входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, выход третьего разряда четырехразрядного регистра сдвига соединен с вторым / входом третьего элемента ИЛИ, выходы разрядов четырехразрядного двоичного счетчика соединены с соответствую щими входами преобразовате.ля двоичного кода в десятичный, выход старшего разряда которого соединен с шинами сброса четырехразрядного регист ра сдвига и четырехразрядного двои 1ного счетчика, входы четвертого и пи того элементов ИЛИ соединены с выходами соответствующих разрядов преобразователя двоичного кода в десятичный, выходы четвертого и пятого элементов ИЛИ подключены к первым входам соответственно первого и второго элементов И блока синхронного ввода комбинированнрй коррекции, BIO рые входы которых соединены соответственно с выходом второго элемента ИЛИ и выходом третьего элемента ИЛИ, а выходы - с соответствующими входами шестого элемента ИЛИ,выход ко- : торого является выходом блока синхронного . ввода комбинированной коррекции. Код времени не является чисто ДВО .ично-десятичным кодом, так как ду с разрядами тетрад (разряды ниц) в нем имеют место разряды триаД (разряды десятков секунд и минут) и разряд диады (разряд десятков .часов) Устройство для вычитания таких кодов должно обеспечивать наряду с корреКг цией кодов тетрад коррекцию кодов триад. Коррекция кода дигшы не требуется, так как переполйения в разряде дееяткоц часов происходить«не может. . Так как при заеме .из старшего десятичного разряда в действительности вместо переносится число промежуточный результат вычитания триад до.лжен быть скорректирован (исправлен) путем вычитания из него числа (в двоичном коде 1010). На чертеже представлена функциональная схема предлагаемого- устройства. . .- . Устройство для вычитания двоичнодесятичных кодов содержит шину 1 уменьшаемого и шину 2 вычитаемого, которые подключены к соответствующим входам первого одноразрядного двоичного вычитателя 3. Выход разности вычитателя 3 через четырехразрядный регистр 4 сдвига соединен с входом уменьшаемого второго одноразрядного вычитателя- 5, а выход заема РК соединен G входом РК- того же вычитателя через элемент 6 задержки. Блок анализа результата включает элементы И 7 8 и триггер 9. Первый и второй входы элемента И 7 соединены соответственно с выходом заема Р, вычитателя 3 и шиной 10 синхронизации, а выход - с единичным входом тригге;ра 9. Нулевой вход триггера 9 соединен с шиной 11 синхронизации. Единичный выход триггера 9 соединен с первым входом элемента И 8, второй вход которой соединен с выходом блока 12 синхронного ввода комбинированной коррекции. Выход элемента И 8 соединен с входом вычитаемого вычитателя 5, выход Рц заема которого через элемент 13 .соединен с входом РК, того же вычитателя, а выход 14 разности W|( является выходом устройства. Вход блока .12 соединен с шиной 15 синхронизации. Блок 12 синхронного ввода комбинированной коррекции- содержит элемент ИЛИ 16, первый вход которого соединен с шиной 15 синхронизации. Выход элемента ИЛИ 16 подключен к входу четырехразрядного регистра 17 сдвига. Выход второго разряда регистра 17 сдвига соединен с первыми входами элементов ИЛИ 18 и 19. Выход третьего разряда регистра 17 соединен с вторым входом элемента 18 ИЛИ. Выход последнего четвертого разряда регистра 17 соединен с вторыми входами элементов ИЛИ 15 и 19 .и счетным входом четырехразрядного двоичного счетчика 20. Выходы первого, второго, третьего и четвертого разрядов счетчика 20 подключены к. соответствующим входам преобразователя 21 двоичнот о кода в десятичный, выход старшего разряда которого соединен с входами Сброс регистра 17 и счетчика 20. Входы элемента ИЛИ 22 формирования сигнала ввода коррекции тетрад и входы элемента ИЛИ 23 формирования сигнала ввода коррекции триад соединены с соответствующими выходами преобразователя 21. Выходы элементов ИЛИ 18 и 22 соединены соответственно с первым и вторым входами элемента И 24. Выходы элементов ИЛИ .19 и 23 сое динены соответственно с первым и вт рым входами элемента И 25. Первый и второй входы элемента ИЛИ 26 подклю чены соответственно с выходам элеме тов И 24 и 25, а выход элемента ИЛИ 26 соединен с вторым входом элемента И 8 блока анализа результата. Устройство работает следующим об разом. С началом операции вычитания по шинам 1 и 2 на вход вычитателя 3 на чинают поступать коды младших тетрад уменьшаемого и вычитаемого младшими разрядами вперед. На выходе вычитате ля формируется промежуточная разнос заем Р по правилу двоичного вы читания. Операция последовательного вычитания одного десятичного разряда кодов осуществляется в течение четырех тактовых импульсов, по окончании которых промежуточная разность оказывается записанной в регистре 4 (поступление тактовых импульсов на регистр 4 не показано). Промежуточная разность задерживается-в регистре 4 с целью определения необходимости её коррекции. Необходимость проведения коррекции выявляется элементами 7-9 Через каждые четыре тактовых импульс по шинам 10 и 11 соответственно поступают синхросигналы Т и Т, приче первым поступает сигнал Т(, который устанавливает триггер 9 в исходное состояние, а затем поступает сигнал Т2, с помощью которого выявляется заем из следующего десятичного разря да (в дальнейшем такой заем мы будем называть межразрядным). При наличии межразрядного заема сигнал Т через элемент.И 7 устанавливает триггер 9 в состояние . Таким образом, к моме.нту поступления следующих четырех тактовых импульсов элемент И 8 оказывается открытым, что обеспечивает в дальнейшем одновременное поступление на входы уменьшаемого вычитателя 5 кода промежуточной разнос ти из регистра 4 и кода.коррекции из блока 12 соответственно. Вычитатель 5 выполняет операцию вычитания этих кодов и на его выходе W формируется правильная разность. Если в мрмент поступления сигна.ла Tj межразрядный заем отсутствует, код коррекции на вход вычитаемого не поступает и код из регистра 4 проходит на выход 14 вычитателя 5 без изменения. Блок 12 синхронного ввода комбинированной коррекции отслеживает поступление десятичных разрядов на первый вычитатель 3 и вырабатывает соответствующие коды коррекции. Работа блока 13 начинается с момента поступления на его вход по шине 15 синхроимпульса, время прихода которого совпадает с началом операции вычитания. Синхроимпульс, пройдя элемент ИЛИ 15, записывает i в четырехразрядный регистр 16 сдвига, который работает от тех же тактовых импульсов, что и регистр 4. Регистр 17 закольцован через второй вход элемента ИЛИ 15, что обеспечивает одно обращение в регистре за четыре тактовых импульса, т.е. за время вычитания одного десятичного разряда кодов. Счетчик 20 считает количество обращений i в регистре 17, а преобразователь 21 преобра- зовывает его показания в позиционный десятичньгй код. Таким образом, момент появления сигнала на выходных шинах преобразователя 21 совпадает с моментом окончания операции- вычитания определенных десятичных разрядов кодов времени в вычитателе 3. Например, при вычитании кодов времени, состоящих из- шести десятичных разрядов (единицы и десятки секунд, единицы и десятки минут, единицы и десятки часов), появление сигнала на первом выходе преобразователя 21 соответствует моменту окончания операции вычитания разрядов единиц секунд, появление сигнала на втором выходе - моменту окончания операции вычитания разрядов десятков секунд и т.д. Появление сигнала на шестом выходе преобразователя 21 соответствует окончанию операции вычитания разрядов десятков часов. Выходы преобразователя, соответствующие десятичным разрядам тетрад, подключены к соответствующим входам элемента ИЛИ 22, а выходы, соответствующие десятичным разрядам триад, к соответствующим входам элемента ИЛИ 23. Для приведенного примера к элементу ИЛИ 22. подключается первый, третий и пятый выходь преобразователя 21,а к элементу ИЛИ 23 - второй и четвертый выходы преобразователя 21. Коды коррекции тетрад - ОНО - и коды коррекции триад - 1010 - формируются в каждом цикле обращения i в регистре 17 и соответственно на выходах элементов ИЛИ 18 и 19. Для подготовки блока 12 к новому циклу вычитания сигнал с последнего выхода преобразователя 21 (для рассмотренного примера это сигнал с шестого выхода) осуществляет установку в исходное положение (в О) регистра 17 и счетчика 20. Предлагаемое устройство может быть использовано для вычитания кодов времени, имеющих большую разрядность. В этом случае могут быть изменены только связи между выходами преобразователя 21 и элементов ИЛИ 22 и 23. По сравнению с известным предлагаемое устройство позволяет значительно сократить объем оборудования, и повысить эксплуатационную надежность . В этом случае вместо N двоичных вычитателей и узлов коррекции (где N - сумма всех двоичных разрядов в коде времени), имеющих место в известном устройстве, в предлагаемом устройстве используется только два двоичных вычитателя и один блок синхронного ввода комбинированной коррекции. Такое сокращение количества функциональных элементов позволяет существенно повысить информативность и безотказность устройства,. По сравнению с известным предлагаемое устройство обладает большими функциональными возможностями благодаря осуществлению операции вычитания кодов времени.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР, № 595730, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1982-04-26—Подача