ды вычитаемого соединены с выходами старших разрядов второго регистра ос татка, вьЬсоды первого и второго узлов деления блока деления усеченных чисел соединены с .информационными входами первой и второй групп коммутатора блока деления усеченных чисел соответственно, выходы которого, за исключением старшего разряда, соИзобретение относится к вычислительной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел,

Цель изобретения - повьшение быстродействия.

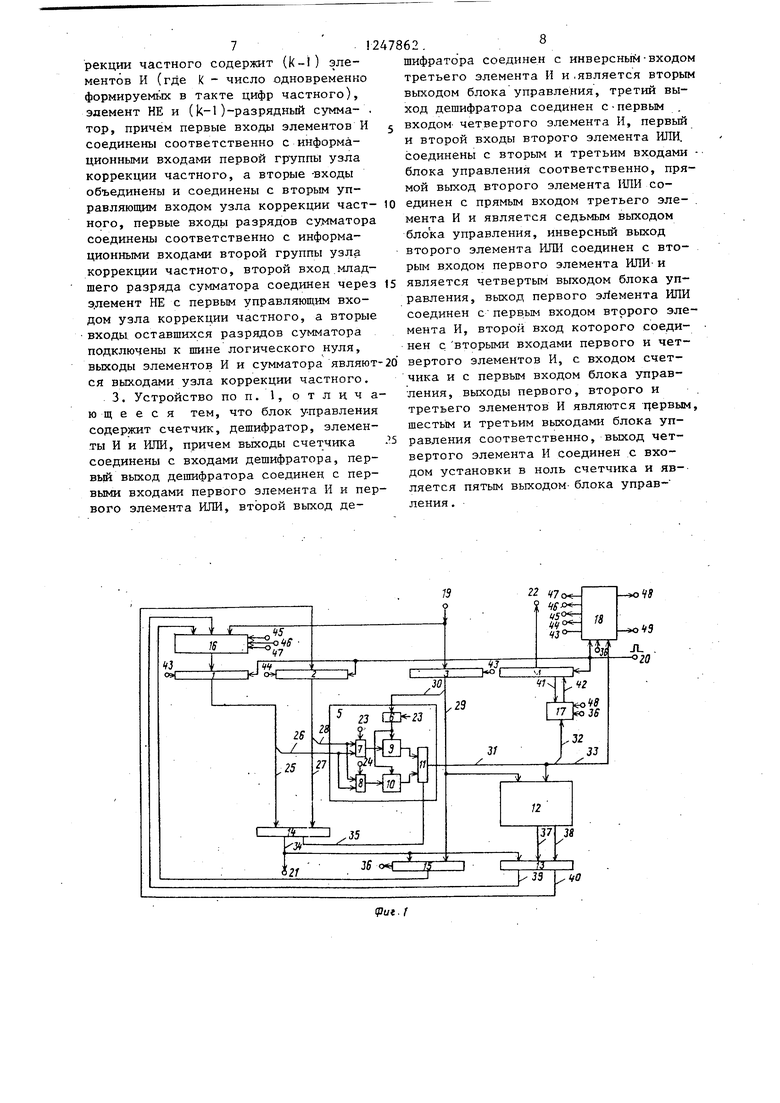

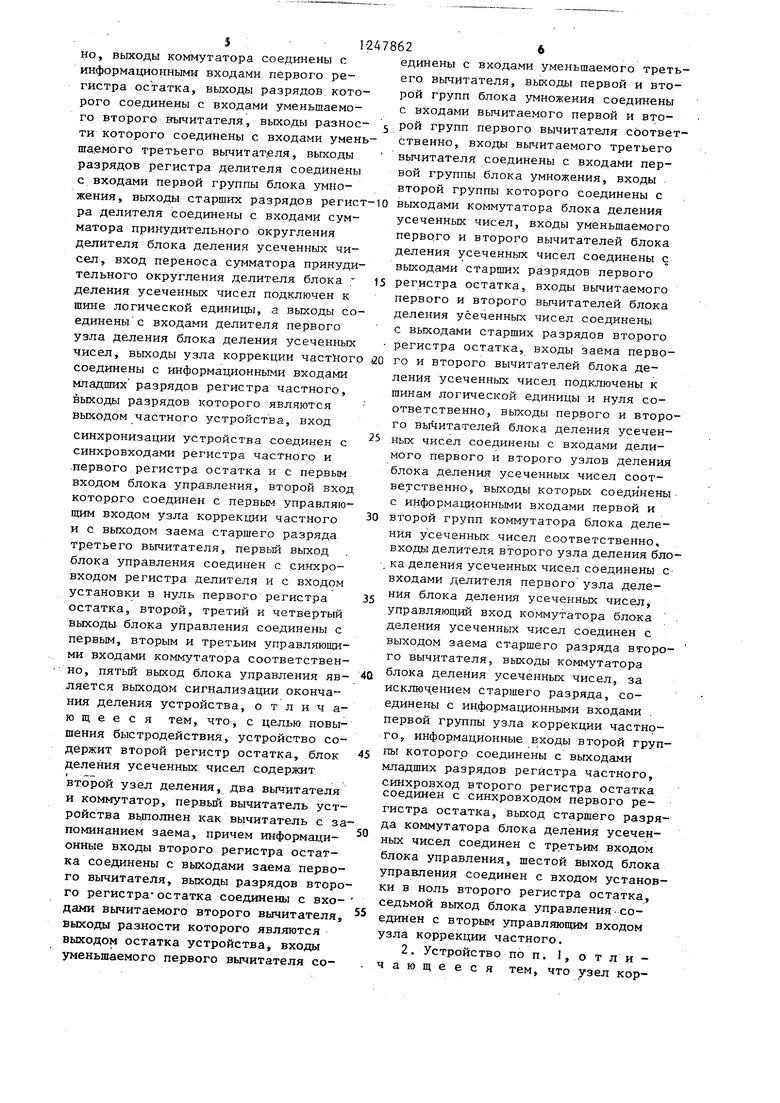

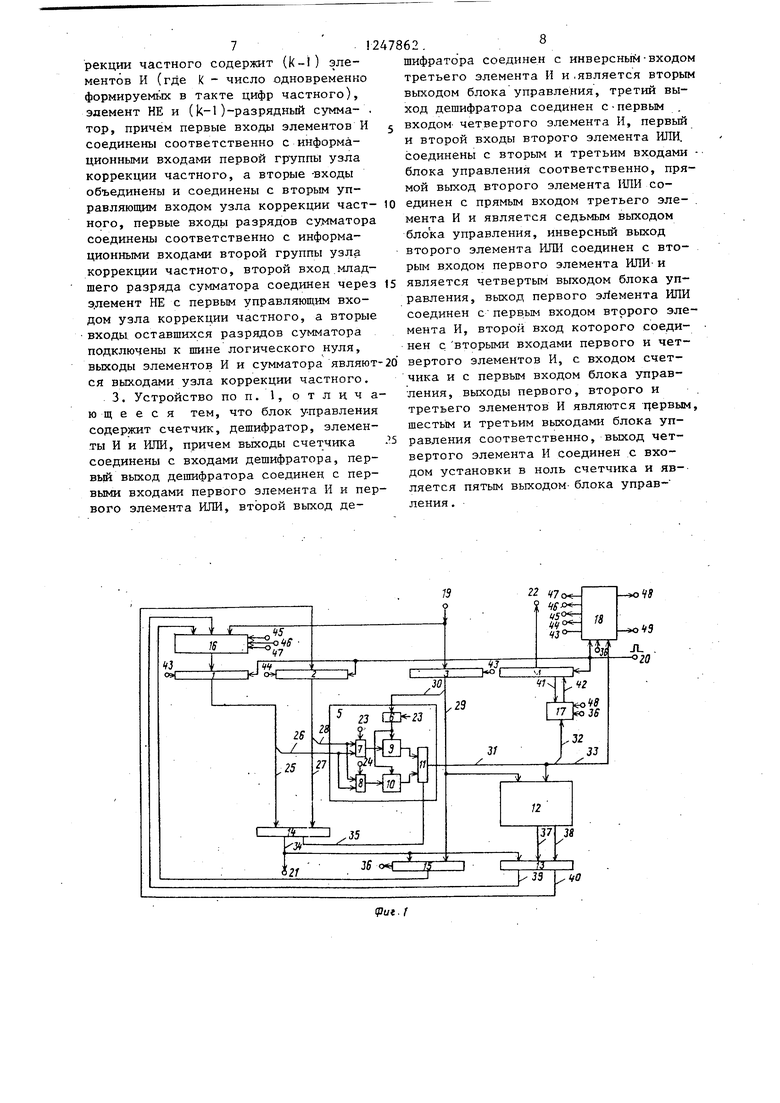

На фиг. 1 приведена структурная схема устройства для деления чисел; на фиг. 2 - функциональная схема пер вого вьгчитателя; на фиг. 3 - функциональная схема узла коррекции частного при К 5; на фиг. 4 - функциональная схема блока управления.

Устройство содержит первьй ре- .гистр 1 остатка, второй регистр 2 остатка, регистр 3 делителя, регистр 4 частного, блок 5 деления усеченньк чисел, сумматор 6 принудительного округления делителя бло- ка 5 деления усеченньк чисел, первый вычитатель 7 блока 5 деления усеченных чис ел, второй вычитатель 8 блока 5 деления усеченных чисел, первьй узел 9 деления блока 5 деления усеченных чисел, второй узел Ш деления блока 5 деления усеченных чисел, коммутатор 11 блока 5 деления усеченных чисел,блок 12 умножения,первый вычитатель 13, второй вычитатель 14, третий вычитатель 15,, коммутатор 16, узел 17 коррекции Частного, блок 18 управления, вход 19 данных устройства, вход 20 синхронизации устройства выход 21 остатка устройства, вы- ход 22 частного устройства, шину 2.3 логической единицы, шину 24 логического нуля, выходы 25 разрядов первого регистра 1 остатка, выходы 26 ст.арпшх разрядов первого регистра 11 остатка, выходы 27 разрядов второго

47862

единены с информационными входами первой группы узла коррекции частного, информационные входы второй группы которого соединены с выходами младших разрядов регистра частного, выходы узла коррекции частного соединены с информационными входами младших разрядов регистра частного. 2 з.п. ф-лы, 4 Щ1.

регистра 2 остатка, выходы 28 старших разрядов второго регистра 2 остатка, выходы 29 разрядов регистра 3 делителя, выходы 30 старших разрядов регистра 3 делителя, выходы 31 коммутатора I1 блока 5 деления усеченных чисел, выходы 32 коммутатора 11 блока 5 деления усеченных чисел за исключением его старшего разряда, выход 33 старшего разряда коммутатора- 11, выходы 34 разности второго вы- читателя 14, выход 35 заема старшего третьего вьиитателя 15, выходы 37 первой группы блока 12 жения, выходы 38 второй группы блока 12 умножения, выходы 39 разности первого вьгчитателя 3, выходы 40 заема первого вьгчитателя 13, выходы 41 младших разрядов регистра 4 частного, выходы 42 узла 17 коррекций частного, выходы 43-49 блока 18 управления. Вычитатель 13 содержит одноразрядные двоичные вычитатели 50. Узел 17 содержит элемент НЕ 51, элементы И 52 и четырехразрядный двоичный сзгмма- тор 53. Блок 18 управления содержит счетчик 54, дешифратор 55, эле - менты И 56 и элементы ИЛИ 57.

Устройство для деления чисел работает следующим образом.

Лусть в исходном состоянии счетчик 54 блока 18 обнулен, а.на входе 19 присутствует п-разрядный дво - ичный код делителя У. Тогда по первому синхроимпу 1ьсу на входе 20, на выходах 43 и 44 блока 18 формируются сигналы, по которым осуществляется запись делителя в регистр 3 и обнуляются регистры 1 и 2. По истечении действия первого импульса на входе 20 счетчик 54 блока 18 переключается в

состояние 1, что, в свою очередь, приводит к црявлению сигнала логической 1 на выходе 45 блока 18. Так как в регистрах 1 и 2 хранятся нулевые коды, то на выходах 31 бло- ка 5 формируется нулевой код k-разрядного частного, на выходе 36 вы- читатЁля 15 образуется сигнал логической 1, на выходах 39 и 40 вычи- тателя 13 формируются нулевые коды. С .приходом второго импульса на вход 20 осуществляется запись с входа 19 п- разрядного кода делимого в регистр 1 нулевого кода заема вычитателя 13 - в регистр 2, и нулевого кода частного в младшие разряды регистра 4. По истечении действия второго импульса на входе 20, счетчик 54 блока 18 переключается в состояние 2. На этом подготовительный этап, включающий два такта, заканчивается и далее вы- полня-ется собственно деление, в процессе которого за m тактов формируется m(k.-l ) + 1 двоичных цифр частного

Рассмотрим работу устройства в течение однрго 1-го такта (Uitm) формирования t цифр частного. По значению старших разрядо в текущего остатка, хранимого в регистрах 1 и 2 в двухрядном коде, и делителя, храни- мого в регистре 3, на выходах узла 9 блока 5 формируется k двоичных цифр iacTHoro, в предположении, что при приведении двухрядного кода текущего остатка в однорядньй код образуется сигнал заема из младших разрядов остатка в старшие, а на выходах узла 10 блока 5 формируется 1. двоичных цифр частного, в предположении, что при приведении двухрядного кода текущего остатка в однорядный код не образуется сигнал заема из младших разрядов остатка в старшие. Параллельно с работой блока 5 работает вычитатель 14 который преобразует двухрядный код текущего остатка в однорядный код.

По значению сигнала заема этого вычитателя 14 осуществляется окончательное формирование К цифв частного на выходах блока 5. Если этот сигнал заема соответствует сигналу логической I, то в качестве k-разрядного частного в устройстве используется значение k цифр частного, образован- нь1х на выходах узла 9 блока 5, а ее- ли сигнал заема соответствует сигналу логического О, то в качестве k- разрядного частного в устройстве используется значение k цифр частного, сформированных на выходах узла 10 блока 5. Сформированное на выходах блока 5k -разрядное частное Z,-. поступает в узел 17 и одновременно подается на входы второй группы бло- . ка 12, на выходах 37 и 38 которого образуется произведение У-Z- в двухрядном коде. На выходах 39 и 40 вычитателя 13 формируется в двухрядном коде разность Y- 2,;, а на выходах вычитателя 15 образуется разность rj Y значение те- кущего остатка, сформированное на выходах разности вычитателя 14 в однорядном коде). Если разность, сформированная на выходах вычитателя 15, положительна, а старший разряд k-pas рядного частного, сформированного в блоке 5, равен нулю, то в i-м такте в качестве очередного остатка г

коммутатором 16 выбирается разность

It

т , Значение этой разности записывается в регистр I со сдвигом влево на (к-) разрядов, в та время, как регистр 2 обнуляется. При этом в узле 17 образуется Скорректированное k-разрядное-частное s виде 1000 ...0 Во всех же других случаях в качестве очередного остатка выбирается разность Г , знач-ение которой в виде двух чисел записьшается соответствующим образом со сдвигом влево на (k-1) разрядов в регистры I и 2. При этом в узле 17 сформированное на выходах блока 5 k -разрядное частное не корректируется. Аналогичным образом работает устройство вовсех других тактах формирования k -д воичных цифр частного.

Формула изобретения1. Устройство для деления чисел, содерзкащее первый регистр остатка, регистр делителя, регистр частного, блок деления усеченных чисел, содержащий сумматор принудительного округления делителя и первый узел деления блок умножения, три вычитателя, коммутатор, узел коррекции частного и блок управления, причем вход данных устройства соединен с информационными входами регистра делителя и с информационными входами первой группы коммутатора, информационные з-коца второй и третьей группы которого соединены с выходами разности первого и третьего вычитателей соответствен

НО, ВЫХОДЫ коммутатора соединены с информационными входами первого регистра остатка, выходы разрядов, которого соединены с входами уменьшаемого второго нычитателя, вькоды разнос ти которого соединены с входами уменшаемого третьего вычитат.еля, выходы разрядов регистра делителя соединены с входами первой группы блока умножения, выходы старших разрядов регис ра делителя соединены с входами сумматора принудительного округления делителя блока деления усеченных чисел, вход переноса сумматора принудительного округления делителя блока деления усеченных чисел подключен к шине логической единицы, а выходы соединены с входами делителя первого узла деления блока деления усеченных чисел, выходы узла коррекции частног соединены с информационными входами младших разрядов регистра частного, выходы разрядов которого являются выходом частного устройства, вход

синхронизации устройства соединен с синхровходами регистра частного и .первого регистра остатка и с первым входом блока управления, второй вход которого соединен с первым управляющим входом узла коррекции частного и с выходом заема старшего разряда третьего вьгчитателя, первый выход блока управления соединен с синхро- входом регистра делителя и с входом установки в нуль первого регистра остатка, второй, третий и четвертый выходы, блока управления соединены с первым, вторым и третьим управляющими входами коммутатора соответственно, пятьй выход блока управления является выходом сигнализации окончания деления устройства, отличающееся тем, что, с целью повышения быстродействия, устройство содержит второй регистр остатка, блок деления усечённых чисел содержит

второй узел деления, два вычитателя и коммутатор, первый вычитатель устройства вьлтолнен как вычитатель с запоминанием заема, причем информационные входы второго регистра остатка соединены с выходами заема первого вьгчитателя, выходы разрядов второго регистра-остатка соединены с входами вычитаемого второго вычитателя, выходы разности которого являются выходом остатка устройства, входы уменьшаемого первого вычитателя со

5

О

5

0

5

Q

5

0

5

единены с входами уменьшаемого третьего вычитателя, выходы первой и второй групп блока умножения соединены с входами вычитаемого первой и второй групп первого вьгчитателя соответственно, входы вычитаемого третьего вьгчитателя соединены с входами первой группы блока умножения, входы второй группы которого соединены с выходами коммутатора блока деления усеченных чисел, входы уменьшаемого первого и второго вычитателей блока деления усеченных чисел соединены с выходами старщих разрядов первого регистра остатка, входы вычитаемого первого и второго вычитателей блока деления усеченных чисел соединены С выходами старших разрядов второго регистра остатка, входы заема первого и второго вычитателей блока деления усеченных чисел подключены к шинам логической единицы и нуля соответственно, выходы первого и второго вычитателей блока деления усеченных чисел соединены с входами делимого первого и второго узлов деления блока деления усеченных чисел соответственно, выходы которых соеди нены . с информационными входами первой и второй групп коммутатора блока деления усеченных чисел соответственно, входы делителя второго узла деления бло- , ка деления усеченных чисел соединены .с входами делителя первого узла деления блока деления усеченных чисел, управляющий вход коммутатора блока . деления усеченных чисел соединен с выходом заема старшего разряда второго вычитателя, выходы коммутатора блока деления усеченных чисел, за исключением старшего разряда, соединены с информационными входами первой группы узла коррекции частного, информационные входы второй группы которого соединены с выходами младших разрядов регистра частного,

синхровход второго регистра остатка соединен с синхровходом первого регистра остатка, выход старшего разряда коммутатора блока деления усеченных чисел соединен с третьим входом блока управления, шестой выход блока управления соединен с входом установки в ноль второго регистра остатка, седьмой выход блока управления-соединен с вторым управляющим входом узла коррекции частного.

2, Устройство по п, 1, о т ли - чающееся тем, что узел коррекции частного содержит (k-l) элементов И (где К - число одновременно формируемьк в такте цифр частного), элемент НЕ и (k-1)-разрядный сумма- . тор, причем первые входы элементов И соединены соответственно с информационными входами первой группы узла коррекции частного, а вторые -входы объединены и соединены с вторым управляющим входом узла коррекции част- ного, первые входы разрядов сумматора соединены соответственно с информационными входами второй группы узла коррекции частного, второй вход младшего разряда сумматора соединен через э.лемент НЕ с первым управляющим входом узла коррекции частного, а вторые входы оставшихся разрядов сумматора подключены к шине логического нуля, выходы элементов И и сумматора являют ся выходами узла коррекции частного,

3. Устройство по п. 1, о т л н ч а ю щ е е с я тем, что блок управления содержит счетчик, дешифратор, элементы И и ИЛИ, причем выходы счетчика соединены с входами дешифратора, пер- вьй выход дешифратора соединен с первыми входами первого элемента И и первого элемента ИЛИ, второй выход дешифратора соединен с инверсньп -входо третьего элемента И и .является вторы выходом блока управления, третий выход дешифратора соединен с - первым входом- четвертого элемента И, первый и второй входы второго элемента ИЛИ. соединены с вторым и третьим входами блока управления соответственно, прямой выход второго элемента 1ШИ соединен с прямым входом третьего эле- мента И и является седьмым выходом блока управления, инверсный выход второго элемента ИШ1 соединен с вторым входом первого элемента ИЛИ- и является четвертым выходом блока управления, выход первого элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого соединен с вторыми входами первого и четвертого элементов И, с входом счетчика и с первым входом блока управления, выходы первого, второго и третьего элементов И являются цервым шестым и третьим выходами блока управления соответственно, выход четвертого элемента И соединен с входом установки в ноль счетчика и является пятым выходом- блока управ- ления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления чисел | 1990 |

|

SU1735844A1 |

Изобретени е относится к области вычислительной техники и может быть приме.нено в быстродействующих арифметических устройствах для выполнения операции деления чисел. Целью изобретения является повышение быстродействия устройства за-счет сокращения длительности такта формирования К цифр частного. Устройство для деления чисел содержит первый и второй регистры остатка, регистры делителя и,частного, блок деления усеченньпс чисел, содержащий сумматор принудительного округления делителя, первый и второй вычитатели, цервый и второй узлы деления и коммутатор, блок умножения, первый, второй и третий вычитатели , коммутатор, узел коррекции частного и блок управления, причем выходы разрядов первого регистра остатка соединены с входами уменьшаемого второго вычитателя, входы вычитаемого которого соединены с выходами разрядов второго регистра остатка, выходы разности второго вычитателя соединены с входами уменьшаемого первого и третьего вычитателей, выходы разрядов регистра делителя соединены .с входами вычитаемого третьго вычитателя и с входами первой группы блока умножения, входы второй группы которого соединены с выходами комйута- тора блока деления усеченных чисел, выходы первой и второй групп блока умножения соединены с входами вычитаемого первой и второй групп первого вычитателя соответственно, вход данных устройства соединен с информационными входами регистра делителя и с информационными входами первой группы ком гутатора, информационные входы второй и третьей групп которого соединены с выходами разности первого и третьего вычитателей соответственно, выходы коммутатора соединены с информационными входами первого регистра остатка, информационные входы второго.регистра остатка соединены с выходами займа первого вычитателя, выходы старших разрядов регистра делителя соединены с входами сумматора принудительного округления делителя блока деления усеченных чисел, выходы сумматора принудительного округления делителя блока деления усеченных чисел соединены с входами делителя первого и второго узлов деления блока деления усеченных чисел, входы делимого которых соединены с вьгходами первого и второго вы читателей блока деления усеченньк чисел соответственно, входы уменьшаемого первого и второго вычитателей блока деления усеченных чисел соединены с выходами старших разрядов первого регистра остатка, а их вхо Ю сл to 4; | 00 |а 1C

м

ВразрядЬ1 реги t ocmHoso

n-SiM-f/kf -i/

П-7

J

Цжж

1

П-7

77

Фиг.З

47 i

4}

о«

Составитель А. Клюев Редактор И. Сегляник Техред М.Ходанич

Заказ 4126/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Л.- Пилипенко

| Патент США № 3234367, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Патент США К 3293418, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Устройство для деления п-раздельных чисел | 1977 |

|

SU732868A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-30—Публикация

1985-01-07—Подача