1

Изобретение относится к области вычислительной техники и предназначено для использования в ЦВМ, оперирующих с командами различных форматов, в которых характер необходимых действий указывается либо обычными полпоразрядными. либо пеполноразрядными относительными (с постоянной или переменной базой), либо неполноразрядными «усеченными кодами операций, либо, наконец, кодами конкретных цепочек последовательно выполняемых операций - обобщенными кодами операций.

Известны устройства, в которых в состав устройства для формирования сигналов операций помимо регистра команд, регистра кода операции с дешифратором и коммутатора включают блок памяти кодов операций (микроопераций). Это позволяет 01 ерироват.ь с командами, в которых указывается один начальный код операции, а коды последующих операций генерируются с помощью блока памяти кодов операций. Однако такие устройства не могут генерировать коды операций с использованием иеполноразрядпых относительных или «усеченных кодов операций, а также кодов обобщенных цепочек операций. Использование форматов команд, содержащих несколько относительных или «усечгн1 ых кодов операций или обобщенных кодов операций увеличивает быстродействие и расп1иряет

функциональные возможности ЦВМ за счет сокращения суммарного времени обращения за программной информацией нри одновременном новыщении информационной емкости последней.

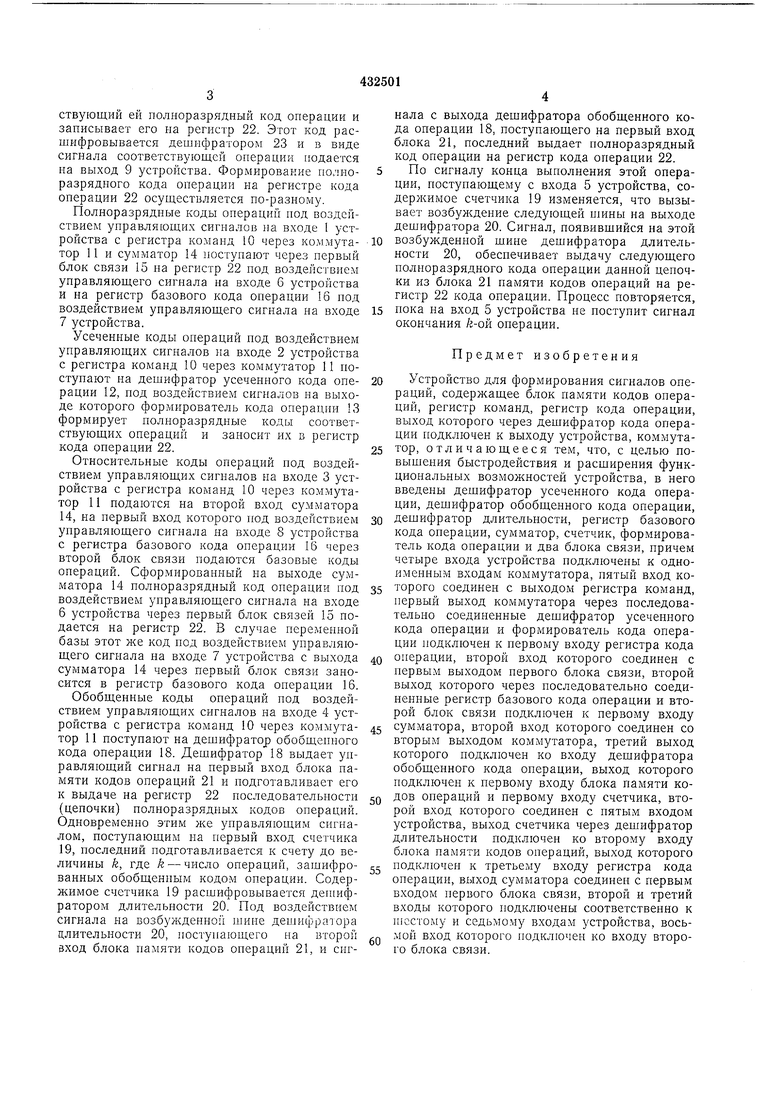

С целью повыщения быстродействия и расп ирения функциональных возможностей в устройство для формирования сигналов операций введены дещифратор усеченного кода операции; дещифратор обобщенного кода операции; дешифратор длительности; регистр базового кода операции; сумматор; счетчик; формирователь кода операции и два блока связи. Схема устройства представлена на чертел е.

В ее состав входят: входы 1-8 и один выход 9; регистр команд 10, коммутатор 11, дешифратор усеченного кода операции 12, формирователь кода операции 13, сумматор 14, первый блок связи 15, регистр базового кода операции

16, второй блок связи 17, депшфратор обобщ,енного кода операции 18, счетчик 19, дешифратор длительности 20, блок памяти кодов операций 21, регистр кода операции 22, дешифратор кода операции 23.

На входы 1-8 подаются управляющие сигналы, на выходе 9 устройством вырабатывается сигнал соответствующей операции.

Код очередной команды записан в регистре команд 10. Для выполнения каждой конкретной операции устройство формирует соответствующий ей полноразрядный код онерации и записывает его на регистр 22. Этот код расшифровывается дешифратором 23 и в виде сигнала соответствующей операции подается па выход 9 устройства. Формирование полиоразрядного кода операции на регистре кода операции 22 осуществляется по-разному.

Полноразрядные коды операций под воздействием управляющих сигналов на входе 1 устройства с регистра комаид 10 через коммутатор 11 и сумматор 14 поступают через первый блок связи 15 па регистр 22 под воздействием управляющего сигнала на входе 6 устройства и на регистр базового кода операции 16 под воздействием управляющего сигнала на входе 7 устройства.

Усеченные коды операций под воздействием управляющих сигналов па входе 2 устройства с регистра команд 10 через коммутатор 11 поступают на дешифратор усеченного кода операции 12, нод воздействием сигналов на выходе которого формирователь кода операции 13 формирует полноразрядные коды соответствующих операций и заносит их в регистр кода операции 22.

Относительные коды операций под воздействием управляющих сигналов на входе 3 устройства с регистра команд 10 через коммутатор 11 подаются на второй вход сумматора 14, на первый вход которого под воздействием управляющего сигнала на входе 8 устройства с регистра базового кода операции 16 через второй блок связи подаются базовые коды операций. Сформированный на выходе сумматора 14 полноразрядный код операции под воздействием управляющего сигнала на входе 6 устройства через первый блок связей 15 подается на регистр 22. В случае переменной базы этот же код под воздействием управляющего сигнала на входе 7 устройства с выхода сумматора 14 через первый блок связи заносится в регистр базового кода операции 16.

Обобщенные коды операций под воздействием управляющих сигналов на входе 4 устройства с регистра команд 10 через коммутатор 11 поступают на дещифратор обобщепного кода операции 18. Дешифратор 18 выдает управляющий сигнал на первый вход блока памяти кодов операций 21 и подготавливает его к выдаче на регистр 22 последовательности (цепочки) полноразрядных кодов операций. Одновременно этим унравляющим сигналом, постунающим на первый вход счетчика 19, последний подготавливается к счету до величины k, где k - число операций, зашифрованных обобщенным кодом операции. Содержимое счетчика 19 расшифровывается дешифратором длительности 20. Под воздействием сигнала на возбужденной шине дешифратора п,лительности 20, поступающего на второй вход блока памяти кодов операций 21, и сигнала с выхода дешифратора обобщенного кода операции 18, поступающего на первый вход блока 21, последний выдает полноразрядный код операции на регистр кода операции 22.

По сигналу конца выполнения этой операции, постунающему с входа 5 устройства, содержимое счетчика 19 изменяется, что вызывает возбуждение следующей шины на выходе дешифратора 20. Сигнал, появившийся на этой

возбужденной шине дешифратора длительности 20, обеспечивает выдачу следующего полноразрядного кода операции данной цепочки из блока 21 памяти кодов операций на регистр 22 кода операции. Процесс повторяется,

пока на вход 5 устройства не поступит сигнал окончания А-ой операции.

Предмет изобретения

Устройство для формирования сигналов операций, содержащее блок цамяти кодов операций, регистр команд, регистр кода операции, выход которого через дешифратор кода операции подключен к выходу устройства, коммутатор, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей устройства, в него введены дешифратор усеченного кода операции, дешифратор обобщенного кода операции,

дешифратор длительности, регистр базового кода онерации, сумматор, счетчик, формирователь кода операции и два блока связи, причем четыре входа устройства подключены к одноименным входам коммутатора, пятый вход которого соединен с выходом регистра команд, первый выход коммутатора через последовательно соединенные дещифратор усеченного кода операции и формирователь кода операции подключен к нервому входу регистра кода

онерации, второй вход которого соединен с нервым выходом нервого блока связи, второй выход которого через последовательно соединенные регистр базового кода операции и второй блок связи подключен к первому входу

сумматора, второй вход которого соединен со вторым выходом коммутатора, третий выход которого подключен ко входу дешифратора обобщенного кода операции, выход которого подключен к первому входу блока памяти кодов операций и первому входу счетчика, второй вход которого соединен с пятым входом устройства, выход счетчика через дешифратор длительности подключен ко второму входу блока памяти кодов операций, выход которого

подключен к третьему входу регистра кода операции, выход сумматора соединен с первым входом первого блока связи, второй и третий входы которого подключены соответственно к шестому и седьмому входам устройства, восьмой вход которого подключен ко входу второго блока связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

| Устройство для отображения информации | 1983 |

|

SU1193722A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для динамической индикацииВРЕМЕНи СуТОК и КАлЕНдАРя | 1978 |

|

SU805244A2 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

Авторы

Даты

1974-06-15—Публикация

1972-03-07—Подача