1

Известно логическое заюо.мииающее устройство, содержащее накопитель иа тороидальных сердечниках с .прямоугольной летлей гистерезиса, .арошитых адресньгми обмотками залиси и считьшавия и разрядными обмотками записи, считывнЕия и чтения, разрядные и адресные форл1и;ро(ватели записи и считывания, усил,ители считывания, реги-стр слава, регистр рагенерации, адресные схемы «И, разря|Д1ные схемы «И и «ИЛИ и управляющие cxsMbi «ИЛИ.

Кедостатко.м известного устройства является то, что iB нем невозможно реализовать многоместные и групповые дзухместные логические остер а|ЦИИ.

ОписьшаеМое устройство отличается от известного тем, что оно содержит схемы «ИЛИ по количеству выходсв .регистра адреса, однн входы которых подключены к выходам регистра адреса, а выходы - ко (входам дещифратора адреса, дополнительный регистр, входы .которого подсоединены ко вхадньгм щиHaiM устройства, а выходы - к другим IBXOдаш схем «ИЛИ.

У|казаН1ные отличия позволяют расширить функциональные возможнасти устройства.

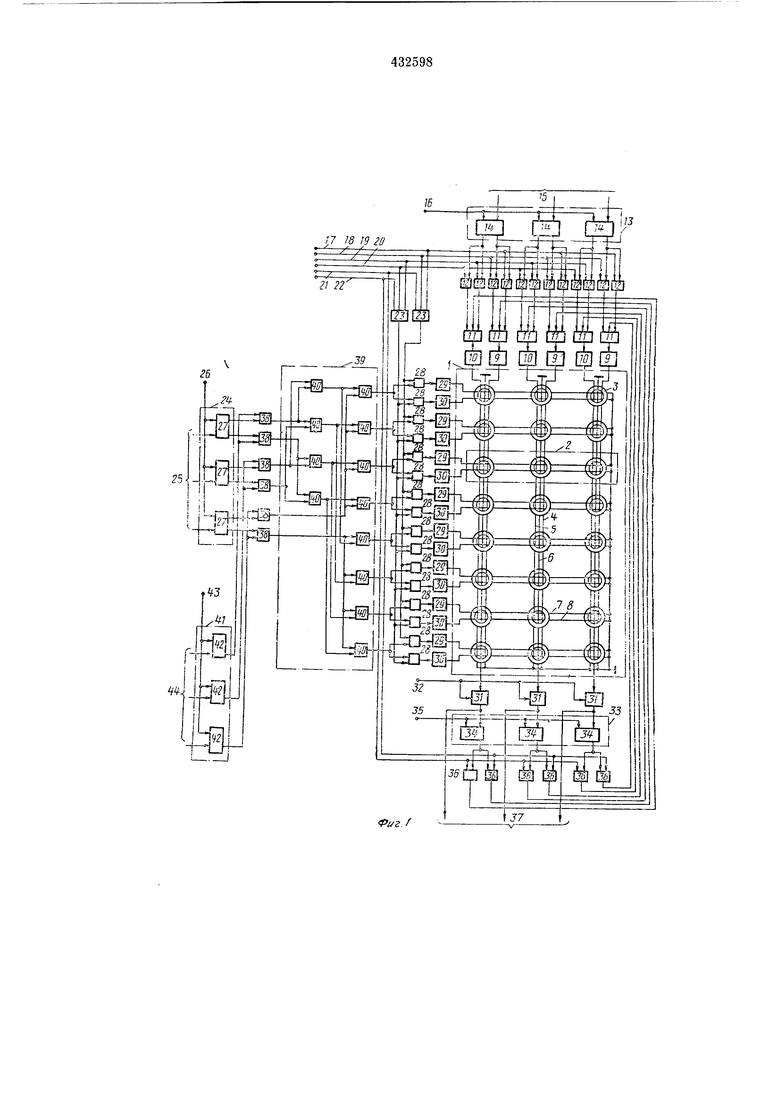

На чертеже представлена схема описываемого устройства.

Устройство содержит накопитель 1 с чргсловыМ.и линейками 2 на тороидальных сердечниках 3 с прямоугольной петлей гистерезиса, 1прош1 тых разрядныМи обмотками 4 запис, разрядными об:мотками 5 считывания, разрядными обмоткамп 6 чтения, адресными Обмотка:ми 7 зап;:с:1 л Едреспьсмп облютка ми 8 считывания. В устройство входят также разрядные форМИрсватели 9 зашиси, зарядные формирователи 10 считывания, схемы 11 «ИЛИ, разрядные cxeiibi 12 регистр 13 слова,

состоящий из триггеров 14, имеющий входы 15 и щину 16 сброса; щины 17-22 управления; управляющие схемы 23 регистр 24 адреса со входами 25 и шиной сброса 26, состоящий из триггеров 27; адресные схемы

28 «И, адресные формирователи 29 записи, адресные формирователи 30 считывания, усилители 31 считывания, щина 32 строб;1рования, регистр ЗЗ регенерации, состоящий из триггеров 34, щииа 35 сброса, схемы 36 «И,

выходные щ.ины 37, схемы 38 «ИЛИ, по количеству выходов регистра адреса, дешифратор 39 адреса (например, двухступенчатый), состоящий из схем 40 «И, дапол.мительпьп регистр 41, состоящий из триггеров 42, одии

входы которого подключены к шине 43 сброса, а другие - ко входным щинам 44. Одни входы схем «ИЛИ подсое(динены к выходам регистра 24 адреса, другие - к выходам регистра 41, а выходы - ко входа м дешифратора

39 адреса.

ycTipoffCPBo работает следующим образом.

В исходном СОСТОЯНИИ 13 регистре 13 хранится вхсщное слово Х(х , . . Xf,. . А„), а в каждой ч.и.словой линейке 2 накопителя / хранится некоторое слово Y(yi ,.../,-,.. у„), где А , - г-й разряд входнапо слова, хранящийся в i-M триггере 14 регистра 13; г/; - г-й .разряд слава, хра.нящийся в /-м сердечнике 3 дайной ЧИСЛОВОЙ линейки 2; п - число разрядов.

Вьшолнение логических Операций (конъюнюции, дизъюнкции, импликации, запрета и др|у1пих) над ВХОД1НЫ1М ;сло13ом и словом избранной число вой линейки 2 (или линеек) 1пр о изводится .при пода1че си пнала на одну «з щин 17-20 уиравле-н.ия. Принцип их реализации тол двст1венеи иапользуемо.мл в известнОМ логическом за1ПО|Минающем устройстве.

:При вьйполненки оиерацли между входиьш славо1м и словом числовой линейки 2 на регистре 24 адреса устана1вли)вается код адреса, соответствующий даниой числовой линейке, а все триггеры 42 даполнительного регистра 41 устанавливаются в .нулевое состоя} ие.

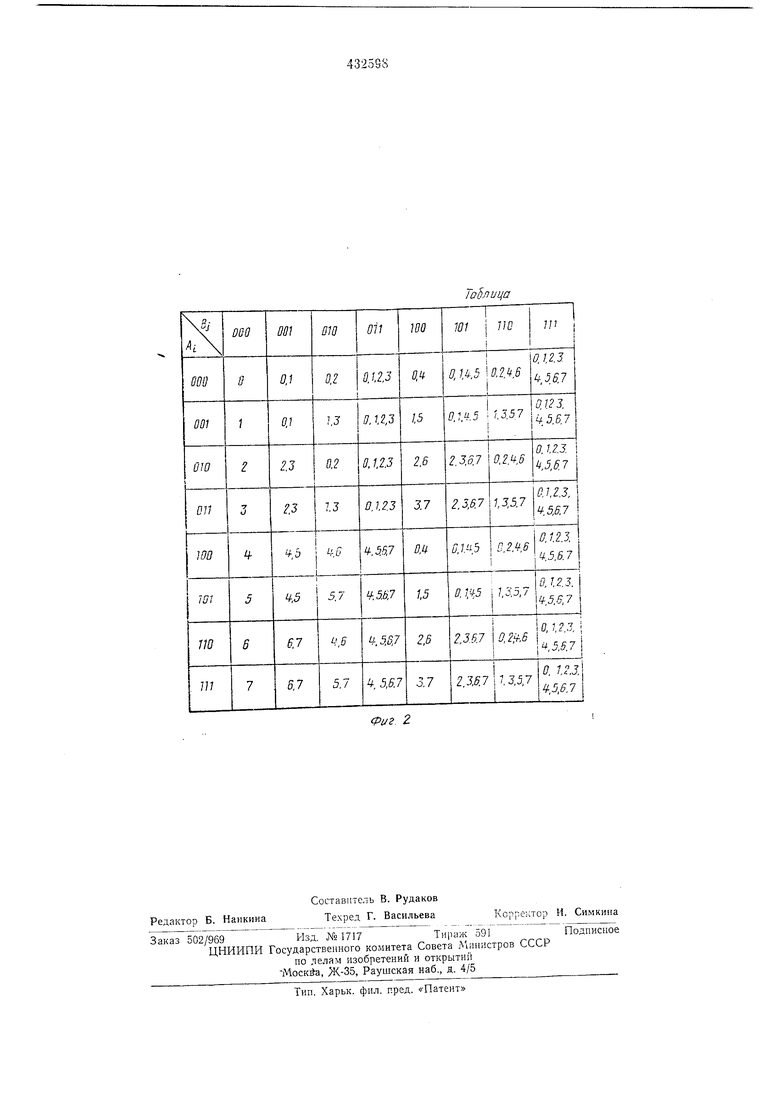

Лри выполнении логичеоких операций между входным словом и груплой слов, хранящихся .в числовых линейках 2 накопителя -/, ца регистре 24 адреса устанавливается адрес Ai(ai, . . . ail,, . .. aim), соответствующий любой числовой линейке из избираемой груипы, а на дотолиительном регистре 4 устанавл.ивается ЖОД избираемой с ав окуй и ост и адресов Bj(b-i,.. . bjh ,... й/ш).

Здесь .приияты следующие обоз.начения: aik - k-tt разряд кода адреса, хранящийся в k-M триггере 27 регистра 24 адреса; b/i,-k-ii разряд кода, хранящийся в й-м триггере 42 дополнительного регистра 4/; т-число разрядов в коде адреса. При этом обращение осуществляется к совокупнссти из 2,. числовых линеек 2, хранящ ;х операнды К/, где s оиределяется числам единиц в коде Bj, «причем

5 2 bji,. В таб.пще (см. фиг. 2), например,

h-l

указаиы возбуждаемые выходы дещифратора 39 адреса (или, что то же, соответствующ-ие им избираемые числовые линейки 2) для различных сочетаннй трехразрядных кодов Ai и Bj. В клетках, находящихся на пересечении соответствующих определеииым кодам AiuBj строки и столбца таблицы, указаиы номера выходов дешифратора 39 адреса, на которых по1явля отся вы.х.одные сигналы при устано1вке этих кодов на регистре 24 адреса и на дополнительном реги.стре 41 соответственно.

Предмет и з о б р е т е н и я

Логическое запоминающее устройство, содержащее яакопитель лт тороидальных сердвчниа ах с иря.моугольиой тетлей гистерезиса, .ирощитых адресньгми обмотками, .иодключеииы1ми к адресным формцрователям, и разрядны1ми об,МОТ1ками, подсоединенными К разрядным формирователям и усилителя,м считывания, а.дресные схемы «И, инфар.ма.ционцые входы которых подключены к выходал дещифратора адреса, а вы.ходы- к адресным формирователял, регистр адрйса, отличающееся тем, что, с целью расщиреиия функциональиых возможностей устройства, оно содержит схемы «ИЛИ по количеству вы.х.о;дсю регистра адреса, одии вХОды 1которых цодключены к выхода м регистра адреса, а 1Бы.хоаы - ко B.XCwaiM дешифратора адреса, дополнительный регистр, в.хады .которого тодсоединены ко входным щлиал устройства, а выходы - к

друг111М вх.одам .схем «ИЛИ.

Риг f

ТоЬлица

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО3 :1 Т ВФОН]] Я-И;ф'РТГЩ <" t- J J^^ '^ • i .• f S .„ J i, is i* | 1972 |

|

SU433541A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

Авторы

Даты

1974-06-15—Публикация

1972-07-03—Подача