1

Изобретение относится к вычислительной тезшике и может быть использовано при созданжи устройств сопряжения вычислительных машин с каналами связи, напршлер, в автоматизированных системах управления (ACYJ.

Известны тщйе устройства, построенные с применением долговременной памяти. Есмлутатора каналов связи, блока преобразования принимаемой информации, распределителя и блока управления. В этих устройствах о 3служивание каналов связи осуществляется по жесткой программе, которая задает определенную последовательность и продолжительность обслуживания.

Цель изобретения - расширение функциональных возможностей устрой ства путем обеспечения оперативной смены порядка соединения вычислительной машины с каналагли связи и оперативной смены длительности связи машины с ка:кдым каналом.

В предлагаемом ycTpoiiCTBe

1первый выход олока долговременной памяти через блок управления подключен к второму входу коЖ,1утатора. Выход этого коглмутатора соединен с входом блока преобразования, второй выход которого через первук схему И (вход схемы И соединен с первш выходом триггера) ПОДЕ ЛЮчен к второьгу входу распределителя. Второй выход распределителя соединен с вторым выходом устройства, первыгл входом счетчика и первым входом второй схемы И выход которой соединен с первым вхо

5 дом схемы РШИ и первы1л входом триггера. Второй выход этого триггера через линию задерлски подключен ко второму входу триггера, второй вход второй схемы И соединен с выходом счетчАжа, второй вход которого соединен с вторым выходом блока долговременной памяти. Вход последнего подключен к BHxojiy схеьш ИЖ, второй вход которой соединен с выходом блока пуска, выход схемы Ж подключен

к третьеглу входу комг.утатора, а вход регистра адреса через шифратор соединен с клазишным пультом

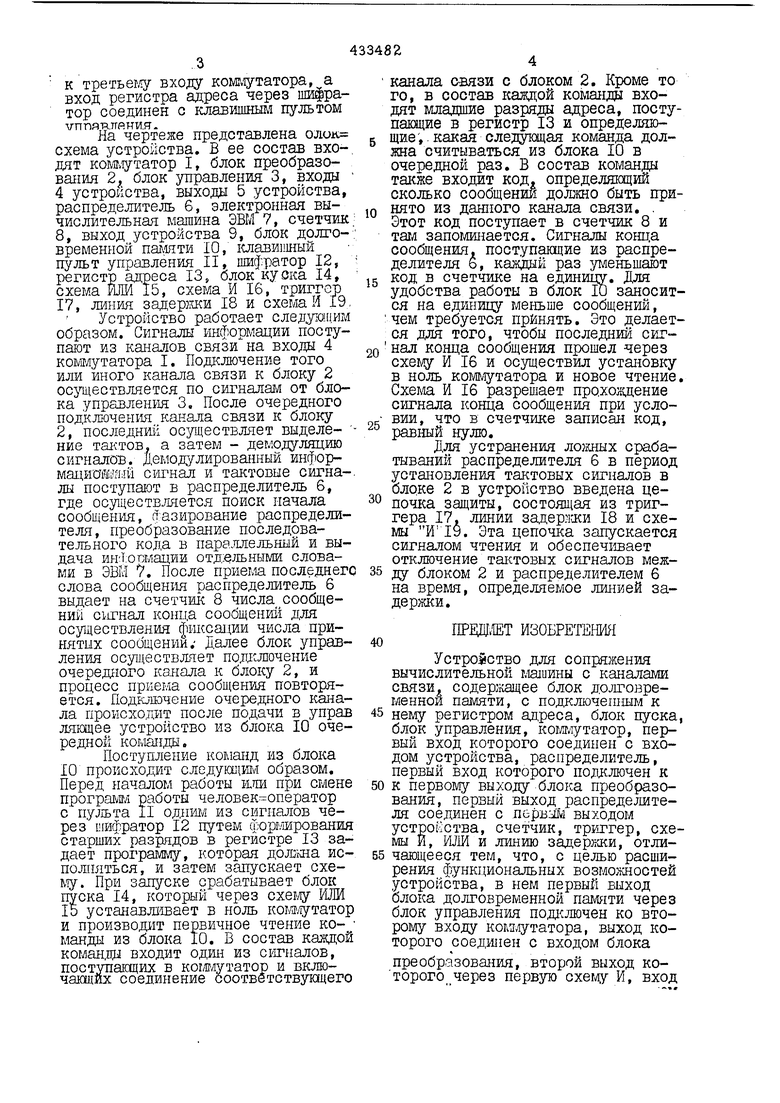

VnnflR7TfiHW.7На чертеже представлена олой. схема устройства. В ее состав входят колттутатор I, блок преобразования 2, блок управления 3, входы 4 устройства, выходы 5 устройства, распределитель 6, электронная вычислительная машина ЭВМ 7, счетчик 8, выход устройства 9, блок долговременной палшти 10, югазиишый пульт управления II, шифратор 12, регистр адреса 13, блок куска 14, схема ЙЖ 15, схема И 16, триггер 17, линия задерзжи 18 и схема И 19

Устройство работает следующим образом. Сигналы i/шформации поступают из каналов связи на входы 4 комглутатора I. Подключение того или много канала связи к блоку 2 ос тцествляется но сигналам от блока управления 3. После очередного подключения канала связи к блоку 2, последни осуществляет выделение тактов, а затем - демодуляцию сигналов. Демодулированный информацишаяш сигнал и тактовые сигналы поступают в распределитель 6, где осутцествляется поиск начала сообщен11я, фазирование распределителя, преобразование последовательного кода в пара.ялельный и выдача ин;1оталации отд:ельными словами в ЭВМ 7. После приема последнег слова сообщения распределитель 6 выдает на счетчик 8 числа сообщеHHii С11гнал когп.1,а сообщение- для осу1дествл ния ф1шса дии числа принятых сообщений; далее блок управления осуществляет подхшочение очередного канала к блоку 2, и процесс приема сообщения повторяется. Подкл эчение очередного канала происходит после подачи в управ лящее устройство из блока 10 очередной когу1анды.

Поступление команд из блока 10 происходит слсд:укк 1М образом. Перед началом работы или при смене програмгл работы человек::::оператог) с пульта II ОД1ПМ из сигналов через 1;шфратор 12 путем (юргжрования старших разрядов в регистре 13 задает програмьту, которая дол:ша исполняться, и затем запускает схему. При запуске срабатывает блок пуска 14, который через cxetiy ИЖ 15 устанаБЛ11вает в ноль KOM.-iyTaTOp и производит первичное чтение команды из блока 10. В состав каждой команда входит од1ш из сигналов, поступащих в коглглутатор и включащих соединение соответствукщего

канала связи с блоком 2, Кроме то го, в состав каждой команду входят младшие разряды адреса, поступащие в регистр 13 и определязощие,. какая следущая команда должна считываться из блока 10 в очередной раз. В состав команды также входит код. определяющий сколько сообщении должно быть принято из данного канала связи. . Этот код поступает в счетчик 8 и тахл запоглинается. Сигналы конца сообщения, поступающие из распределителя 6, каждый раз у1,1еньшают код в счетчике на единицу. Для удобства работы в блок 10 заносится на ед1шицу меньше сообщений, чем требуется принять. Это делается для того, чтобы последний сигнал конца сообщения прошел через cxej/y И 16 и осуществил установку в ноль коглмутатора и новое чтение. Схема И 16 разрешает прохождение конца сообщения при условии, что в счетчике записан код, равный нулю.

Для устранения логшых срабатываний распределителя 6 в период уста11овления тактовых сигналов в блоке 2 в устройство введена цепочка защиты, состоящая из триггера 17, линии зацерласи 18 и схемы И19. Эта цепочка запускается сигналом чтения и обеспечивает отключение тактовых сигналов между блоком 2 и распределителем 6 на время, определяемое линией задержки.

ПРЩЖТ ИЗОБРЕТЕНИЯ

Устройство для сопряжения вычислительной машины с каналами связи, содер;кащее блок долговременной памяти, с подключетшм к

5 нему регистром адреса, блок пуска, блок управления, кометутатор, первый вход которого соединен с входом устройства, распределитель, первый вход которого подключен к

0 к первому выходу блока преобразования, первый выход распределителя соединен с выходом устройства, счетчик, триггер, схемы И, Ш1И и линию задержки, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в нем первый выход блока долговременной памяти через блок управления под1:лючен ко второму входу коиз.тутатора, выход которого соединен с входом блока

преобразования, второй выход которого через первую cxefi y И, вход которой соединен с первым выходит триггера, подключен к второ.му входу распределителя, второй выход которого соединен с вторым выходом устройства, первым входом счетчика и первш- входом второй схерлы И, выход которой соединен с первыгл входом схедш PUffl и первым входом триггера, второй выход которого через линию задершш подключен ко второтиу входу триггера, второй вход второй схемы И соеди43345 10 г6 нен с выходом счетчика, второй вход которого соединен с вторым выходом блока долговременной памяти, вход которого подключен к к выходу схет,ш ИЛИ, второй вход которой Соединен с выходом блока пуска, выход схеглы ИЛИ подшхючен к третье г/ входу коштутатора, а вход регистра адреса через шифратор соединен с штавишным пультом управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИСКРЕТНАЯ МИКРОКОНТРОЛЛЕРНАЯ СЕТЬ | 1997 |

|

RU2110827C1 |

| Система телемеханики для циклического опроса рассредоточенных объектов | 1977 |

|

SU691912A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Система для обмена информацией | 1985 |

|

SU1298760A1 |

| Устройство для синхронизации обменаМЕжду КОММуНиКАциОННыМ пРОцЕССОРОМи КАНАлАМи СВязи | 1979 |

|

SU809142A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Устройство для контроля электрических цепей | 1982 |

|

SU1051466A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Распределенная система для программного управления технологическими процессами | 1988 |

|

SU1605212A1 |

Даты

1974-06-25—Публикация

1972-02-28—Подача