1

Изобретение относится к электронной цифровой вычислительной технике и может быть использовано в измерительных приборах дискретного типа, в регламентной аппаратуре дискретных систем различного назначения, в системах телекодовой связи и в других случаях для деления чисел с представлением результата в двоичном коде. В частности, оно может быть использовано во всех случаях, когда требуется преобразовать простую дробь в двоичный код.

Известно устройство для деления чисел, содержащее счетчики числителя, знаменателя и результата, схемы ввода числителя и знаменателя, схему выделения нуля, входы которой подключены к выходам всех разрядов счетчика числителя, а выход соединен с нулевым входом управляющего триггера, единичный выход которого подключен к первому входу схемы совпадения, ко второму входу которой подключен выход генератора, а выход соединен со входом счетчика знаменателя.

Известное устройство дает результат с округлением до единицы, т. е. не позволяет получить в результате дробную часть. Кроме того, результат деления в известном устройстве не повторяется при повторных вычислениях из-за ошибки дискретности.

Цель изобретения - повыщение точности работы устройства.

Это достигается тем, что устройство содержит дополнительный счетчик, вход которого соединен с выходом схемы совпадения, а выход - со входом счетчика числителя.

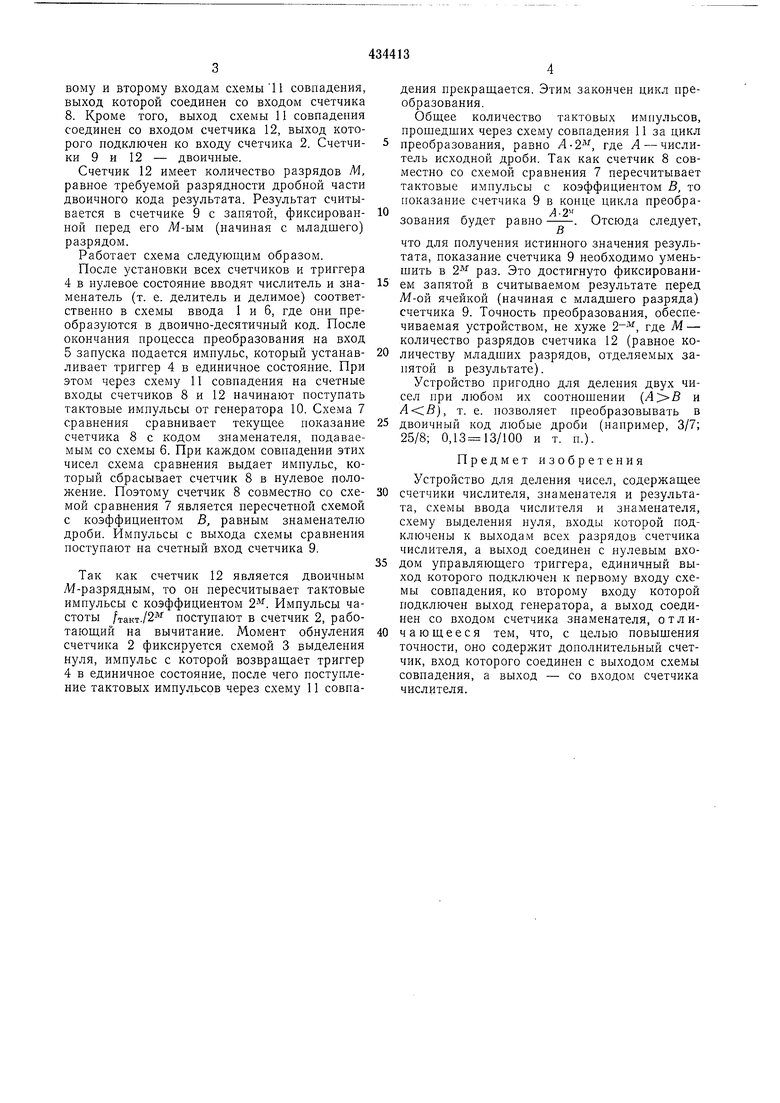

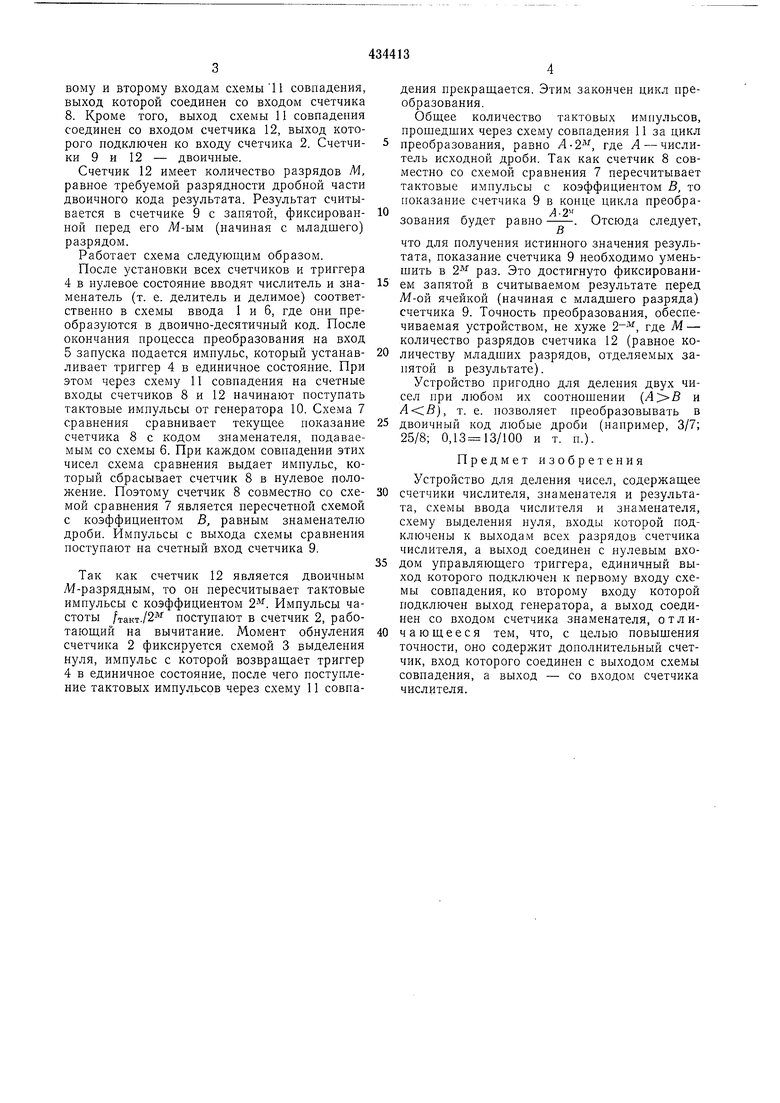

На чертеже изображена блок-схема устройства.

Оно содержи схему 1 ввода числителя, счетчик 2 числителя, схему 3 выделения нуля, триггер 4, вход 5 запуска устройства, схему 6

ввода знаменателя, схему 7 сравнения, счетчик 8 знаменателя, счетчик 9 результата, генератор 10 тактовых импульсов, схему 11 совпадения и счетчик 12. Схема 1 ввода числителя соединена со входами разрядов двоично-десятичного счетчика 2 числителя, работающего на вычитание. Выходы всех разрядов этого счетчика подключены к схеме 3 выделения нуля, соединенной с единичным входом триггера 4. Нулевой вход

этого триггера соединен со входом 5 запуска устройства.

Охема 6 ввода знаменателя подключена ко входам схемы 7 сравнения, вторыми входами соединенной с выходами всех разрядов двоично-десятичного счетчика 8 знаменателя, а выходом - со входом установки нуля этого же счетчика и счетным входом счетчика 9 результата. Единичный выход триггера 4 и выход генератора 10 подключены соответственно к первому и второму входам схемы11 совпадения, выход которой соединен со входом счетчика 8. Кроме того, выход схемы 11 совпадения соединен со входом счетчика 12, выход которого подключен ко входу счетчика 2. Счетчики 9 и 12 - двоичные.

Счетчик 12 имеет количество разрядов М, равное требуемой разрядности дробной части двоичного кода результата. Результат считывается в счетчике 9 с запятой, фиксированной перед его Л1-ым (начиная с младшего) разрядом.

Работает схема следуюгцим образом.

После установки всех счетчиков и триггера

4в нулевое состояние вводят числитель и знаменатель (т. е. делитель и делимое) соответственно в схемы ввода 1 и 6, где они преобразуются в двоично-десятичный код. После окончания процесса преобразования на вход

5запуска подается импульс, который устанавливает триггер 4 в единичное состояние. При этом через схему 11 совпадения на счетные входы счетчиков 8 и 12 начинают поступать тактовые импульсы от генератора 10. Схема 7 сравнения сравнивает текущее показание счетчика 8 с кодом знаменателя, подаваемым со схемы 6. При каждом совпадении этих чисел схема сравнения выдает импульс, который сбрасывает счетчик 8 в нулевое положение. Поэтому счетчик 8 совместно со схемой сравнения 7 является нересчетной схемой

с коэффициентом В, равным знаменателю дроби. Импульсы с выхода схемы сравнения поступают на счетный вход счетчика 9.

Так как счетчик 12 является двоичным М-разрядным, то он пересчитывает тактовые импульсы с коэффициентом 2. Импульсы частоты /такт./2 поступают в счетчик 2, работающий на вычитание. Момент обнуления счетчика 2 фиксируется схемой 3 выделения нуля, импульс с которой возвращает триггер 4 в единичное состояние, после чего поступление тактовых импульсов через схему 11 совпадения прекращается. Этим закончен цикл преобразования.

Общее количество тактовых импульсов, прощеди1их через схему совпадения 11 за цикл преобразования, равно Л-2, где Л-числитель исходной дроби. Так как счетчик 8 совместно со схемой сравнения 7 пересчитывает тактовые импульсы с коэффициентом В, то показание счетчика 9 в конце цикла преобраА-2

зовапия будет равно. Отсюда следует,

В

что для получения истинного значения результата, показание счетчика 9 необходимо уменьшить в 2 раз. Это достигнуто фиксированием запятой в считываемом результате перед М-ой ячейкой (начиная с младшего разряда) счетчика 9. Точность преобразования, обеспечиваемая устройством, не хуже 2, где М - количество разрядов счетчика 12 (равное количеству младщих разрядов, отделяемых запятой в результате).

Устройство пригодно для деления двух чисел при любом их соотношении ( и ), т. е. позволяет преобразовывать в двоичный код любые дроби (например, 3/7; 25/8; 0,13 13/100 и т. п.).

Предмет изобретения

Устройство для деления чисел, содержащее счетчики числителя, знаменателя и результата, схемы ввода числителя и знаменателя, схему выделения нуля, входы которой подключены к выходам всех разрядов счетчика числителя, а выход соединен с нулевым входом управляющего триггера, единичный выход которого подключен к первому входу схемы совпадения, ко второму входу которой подключен выход генератора, а выход соединен со входом счетчика знаменателя, отличающееся тем, что, с целью повышения точности, оно содержит дополнительный счетчик, вход которого соединен с выходом схемы совпадения, а выход - со входом счетчика числителя.

ГТТ

u 11

11 V

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для импульсного регулирования мощности переменного тока | 1984 |

|

SU1244763A1 |

| Программируемый делитель частоты следования импульсов | 1980 |

|

SU945998A1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Делитель частоты следования импульсов | 1976 |

|

SU587628A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ УМНОЖЕНИЕМ И ДЕЛЕНИЕМ | 1973 |

|

SU368601A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1973 |

|

SU396834A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для измерения частоты повторения импульсов | 1977 |

|

SU660266A1 |

Даты

1974-06-30—Публикация

1972-05-03—Подача