1

ИзОбретение относится -к вычислительной технике.

Устройство для управления умножением и делением двоично-десятичных чисел в электронных вычислительных клавишных машинах, в которых числа представляются в регистрах динамического типа в форме с фиксированной запятой, причем положение запятой выбирается оператором с помощью специального переключателя.

Р1звестны устройства управления умножением и делением двоичпо-десятичпых чисел, представленных в форме с переменно-фиксированной запятой, в арифметическом устройстве на динамических регистрах, включающие тактирующий блОК с выходами им-пульсов тактирования разрядов, связанными со входом счетчика местного управ тения, переключатель положения запятой, триггер управления сдвигом информации и счетчик местного управления.

Предлагаемое устройство отличается тем, что содержит схему «И записи метки, схему выделения метки и генератор кода метки; шина сигнала первого состояния счетчика местного управления, выход генератора кода метки, единичный выход триггера управления сдвигом присоединены через схему «И записи метки ко входу первого разряда регистра

множителя - делимого арифметического устройства; выход схемы выделения метки через схему совпадения присоединен ко входу установки в нуль триггера управления сдвигом и

связан со входом счетчика через схему «И, к которой также присоединен выход переключателя положения запятой, причем при положении переключателя, соответствующем фиксации запятой после О, 1, 2,...,л-1 разрядов чисел, выход переключателя подключен к шинам импульсов тактирования, соответственно, 1, 2, ...,л+1-го разрядов при делении, а при умножении выход переключателя подключен, соответственно, к цепям n-fl,

п-,..., разрядов.

Это позволяет уменьшить оборудование блока для управления умножением и делением электронных клавишных машин на динамических регистрах.

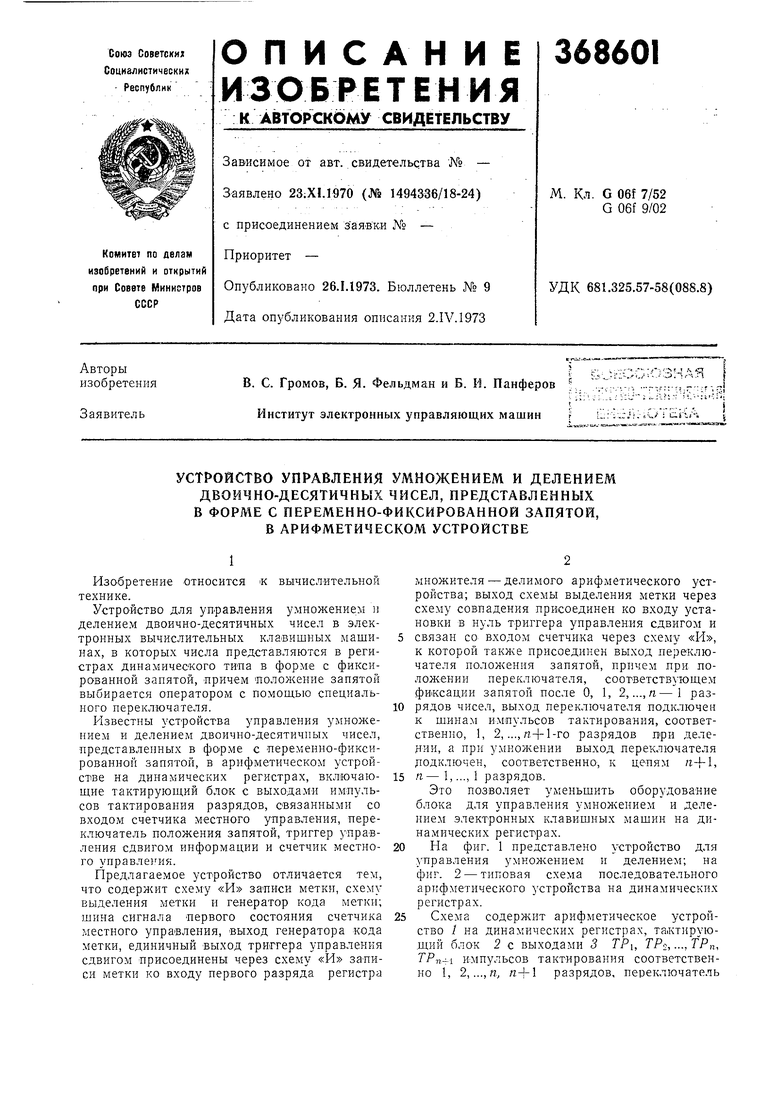

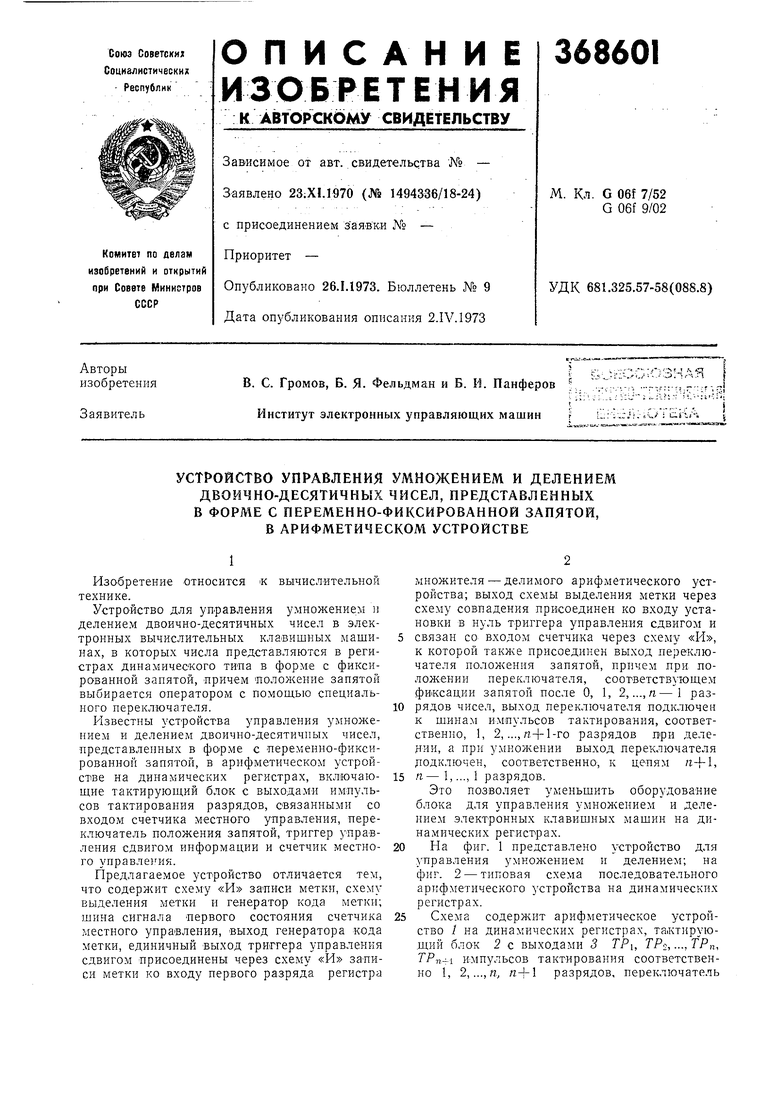

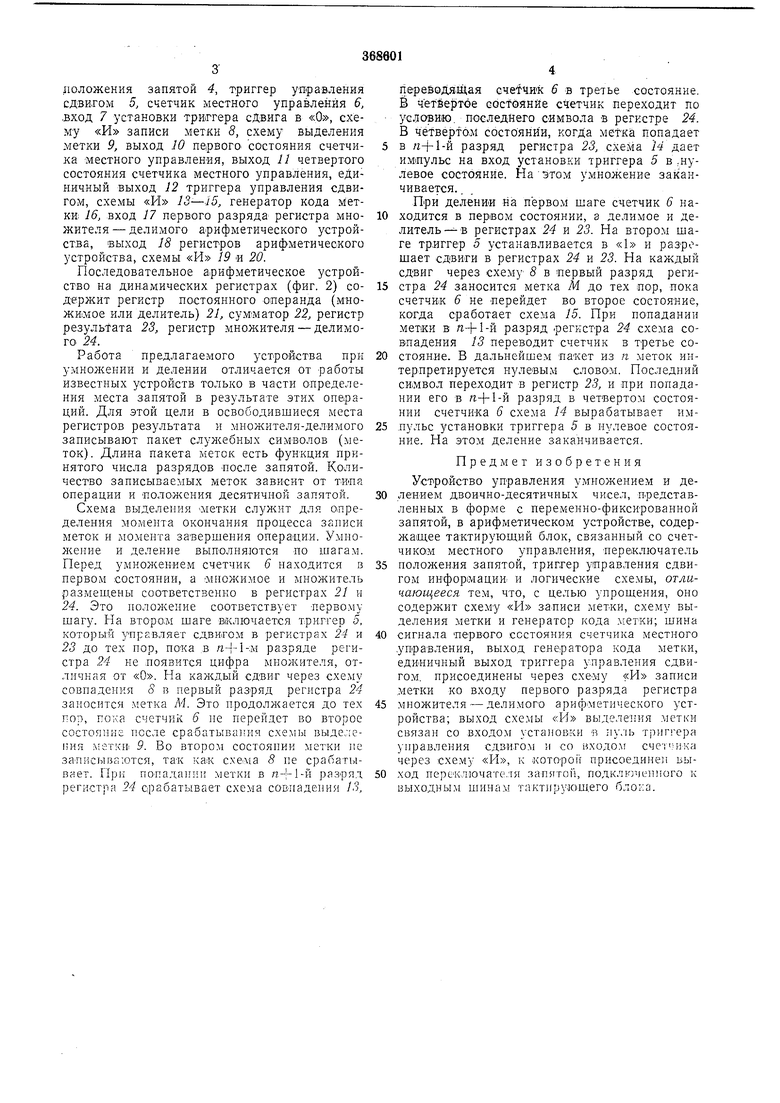

На фиг. 1 представлено устройство для управления умнол енпем и делением; на фиг. 2 - типовая схема последовательного арифметического устройства на динамических регистрах.

Схема содержит арифметическое устройство / на динамических регистрах, та.ктирую.щий блок 2 с выходами 3 TPi, ТРо,...,ТРп, и мпульсов тактирования соответственно 1, 2,...,«., л+1 разрядов, переключатель

положения запятой 4, триггер управления сдвигом 5, счетчик местного управления 6, .вход 7 установки триггера сДвига в «О, схему «И записи метки 8, схему выделения метки 9, выход 10 первого состояния счетчика местного управления, выход П четвертого состояния счетчика местного управления, единичный выход 12 триггера управления сдвигом, схемы «И 13-15, генератор кода метки 16, вход 17 первого разряда регистра множителя - делимого арифметического устройства, выход 18 регистров арифМетического устройства, схемы «И 19 « 20.

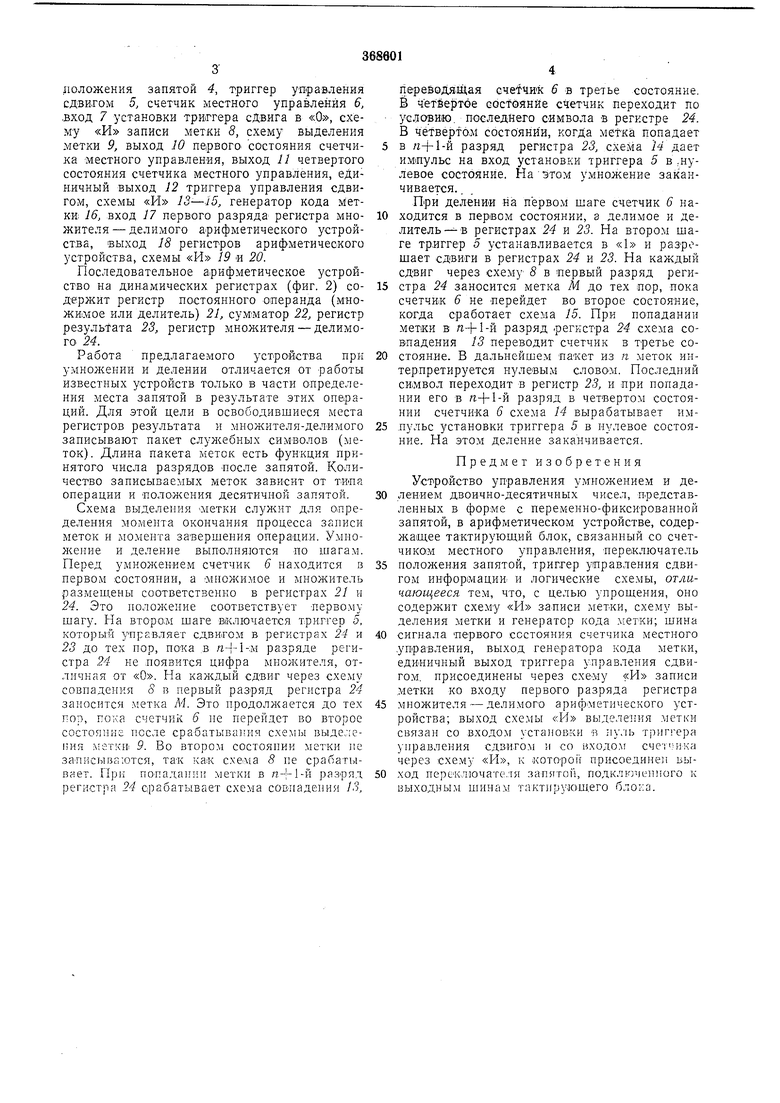

Последовательное арифметическое устройство на динамических регистрах (фиг. 2) содержит регистр постоянного операнда (множимое или делитель) 21, сумматор 22, регистр результата 23, регистр множителя - делимого 24.

Работа предлагаемого устройства при умно;кении и делении отличается от работы известных устройств только в части определения места запятой в результате этих операций. Для этой цели в освободившиеся места регистров результата и множителя-делимого записывают пакет служебных символов (меток). Длина пакета меток есть функция принятого числа разрядов после запятой. Количество записываемых меток зависит от типа операции и положения десятичной запятой.

Схема выделения -метки служит для определения момента окончания процесса записи меток и момента завершения операции. Умножение и деление выполняются по шагам. Перед умножением счетчик 6 находится в первом состоянии, а множимое и множитель размеш,ены соответственно в регистрах 21 и 24. Это положение соответствует первому шагу. Ffa втором шаге включается триггер 5, который управляет сдвигом в регистрах 24 и 23 до тех пор, пока в п+1-;м разряде регистра 24 не появится цифра множителя, отличная от «О. На каждый сдвиг через схе.му совпадения 5 в первый разряд регистра 24 заносится метка М. Это продолжается до тех пор, пока счетчик 6 не перейдет во второе состояние после срабатыБа)ия выделения метки 5. Во втором состоянии метки пе заПисыгзаются, так как 8 пе срабатывяет. При попадапнн метки в л+1-й разряд регистра 24 срабатывает схема совпадения 13,

пере&оДящая 6 в третье состояние. В четёертое состояние счетчик переходит по УСЛОВИЮ, последнего символа в регистре 24. В четвертое состоянии, когда метка попадает

в Я+1-Й разряд регистра 23, схема l дает импульс на вход установки триггера 5 в ,нулевое состояние. На этом умножение заканчивается. . При делении на первом шаге счетчик 6 находится в первом состоянии, а делимое и делитель- в регистрах 24 и 23. На втором шаге тр-иггер 5 устанавливается в «1 и разрешает сдвиги в регистрах 24 и 23. На каждый сдвиг через схему 8 в первый разряд регистра 24 заносится метка М до тех пор, пока счетчик 6 не перейдет во второе состояние, когда сработает схема 15. При попадании метки в п-|-1-й разряд .регистра 24 схема совпадения 13 переводит счетчик в третье состояние. В дальнейшем пакет из п меток интерпретируется нулевым словом. Последний символ переходит в регистр 23, и при попадании его в tt-f-1-й разряд в четвертом состоянии счетчика 6 схема 14 вырабатывает импульс установки триггера 5 в нулевое состояние. На этом деление заканчивается.

Предмет изобретения

Устройство управления умножением и делением двоично-десятичных чисел, представленных в форме с переменно-фиксированной запятой, в арифметическом устройстве, содержащее тактируюший блок, связанный со счетчиком местного управления, переключатель

положения запятой, триггер управления сдвигом информации и логические схемы, отличающееся тем, что, с целью упрош;ения, оно содержит схему «И записи метки, схему выделения метки и генератор кода метки; шина

сигнала первого состояния счетчика местного управления, выход генератора кода метки, единичный выход триггера управления сдвигом, присоединены через схему «И записи метки ко входу первого разряда регистра

множителя - делимого арифметического устройства; выход схемы «И выделения метки связан со входом установки в триггера управления сдвигом и со входом счетмака через схему «И, к которо1г присоединен ьыход переключателя запятой, подключенного к выходным шинам тактирующего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Множительно-делительное устройство | 1978 |

|

SU746511A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

| Устройство для деления | 1991 |

|

SU1783523A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

Фиг. 2

Авторы

Даты

1973-01-01—Публикация