1

Изобретение относится к автоматике и телемеханике.

Известен фазовый компаратор, содержащий триггер, в цепи запуска которого включены две импульсно-потенциальные схемы совпадения.

Недостаток этого фазового компаратора состоит в его низкой точности.

Цель изобретения - повышение точности в работе фазового компаратора.

Эта цель достигается тем, что он содержит второй триггер с двумя импульсно-потенциальными схемами совпадения в цепи запуска, причем потенциальные входы обеих схем совпадения подключены параллельно и соответственно к источникам прямого и инверсного сигнала прямоугольной формы одной из сравниваемых частот, их объединенные импульсные входы подключены соответственно к источникам прямого и инверсного сигнала прямоугольной формы другой сравниваемой частоты, а выходы триггеров подключены к двум последовательно соединенным основной и дополнительной логическим схемам.

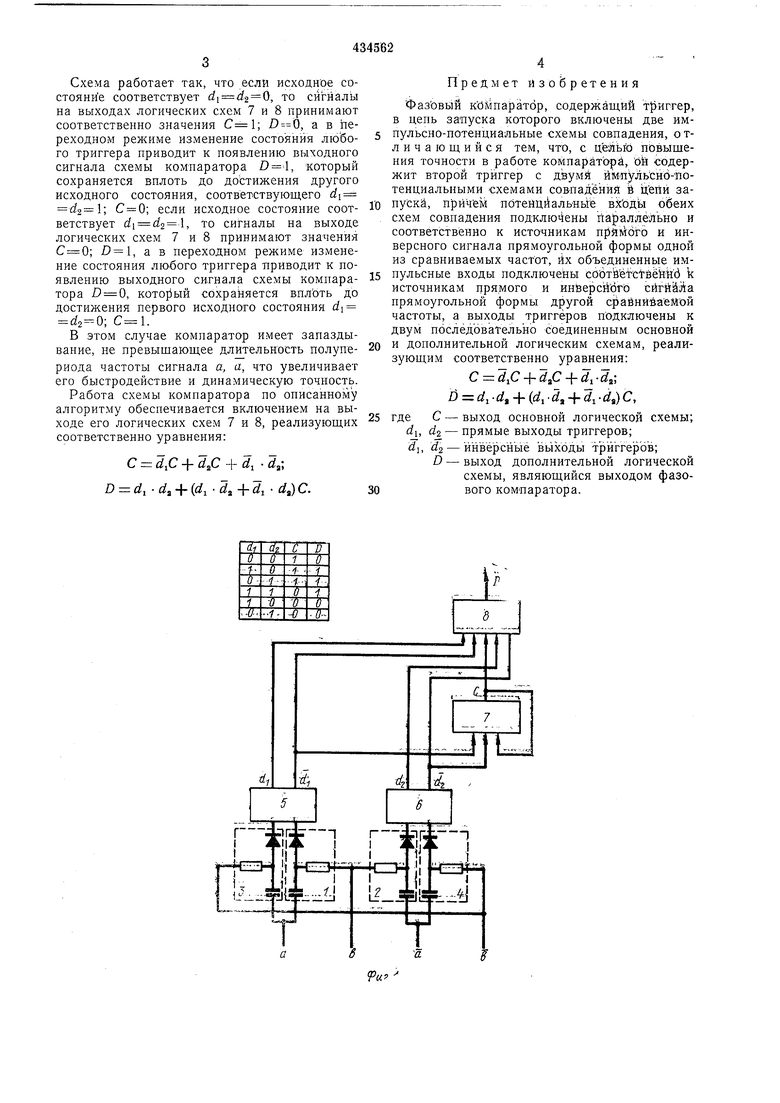

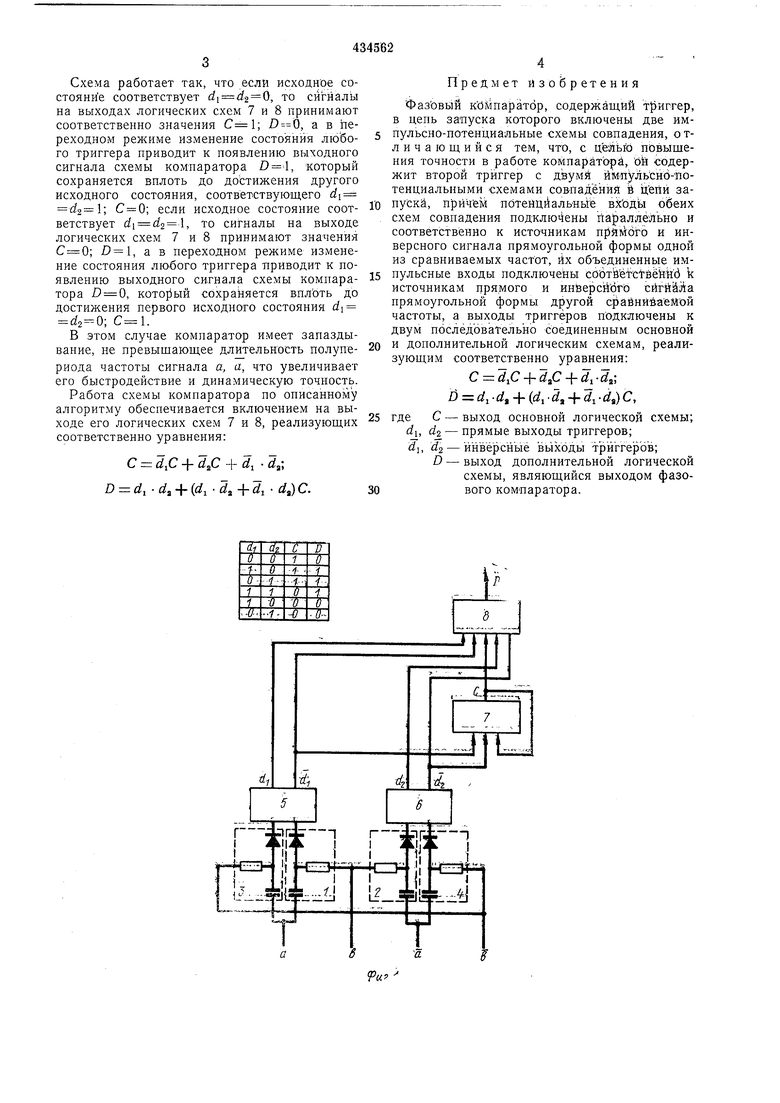

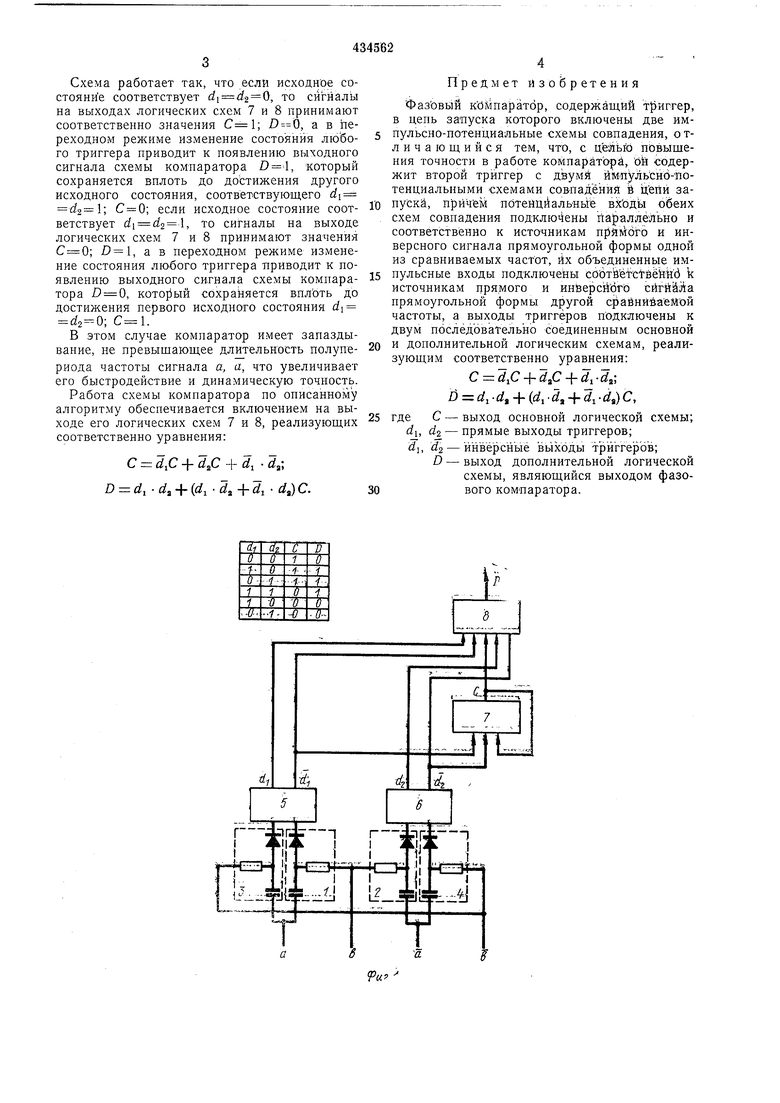

На фиг. 1 изображена блок-схема предлагаемого фазового компаратора; на фиг. 2 - принципиальная схема фазовогокомпаратора.

Схема компаратора работает следующим образом.

На схеме Ь, b - прямой и инверсный частотные сигналы, подаваемые параллельно и соответственно на потенциальные входы схем 1, 2 и 3, 4 совпадения; а, а - прямой и инверсный сигналы, подаваемые соответственно на объединенные импульсные входы этих схем; cfi, dz - выходные сигналы триггеров 5 и 6; С - выходной сигнал логической схемы 7; D - выходной сигнал логической схемы 8, т. е. общий выход схемы компаратора.

Результирующий сигнал D, характеризующий знак рассогласования по фазе между сигналами а, а к Ь, b на входе, вырабатывается на основании сравнения сигналов di, d и d,

dz триггеров, с учетом предыдущего исходного состояния схемы компаратора, при котором эти сигналы совпали, т. е. или di

.

Исходные состояния схемы характеризуют устанавливающийся режим на входе компаратора (частоты сигналов на входе равны) и различаются знаком рассогласования по фазе между Сигналами на входе а, а и &, Ь; состояние имеет место, когда сигналы а, а опережают сигналы Ь, Ь; состояние di - d2 имеет место, когда сигналы Ь, Ь опережают сигналы а, а. Схема работает так, что если исходное состояние соответствует 0, то сигналы на выходах логических схем 7 и 8 принимают соответственно значения , а в переходном изменение состояния любого триггера приводит к появлению выходного сигнала схемы компаратора , который сохраняется вплоть до доЬтижения другого исходного состояния, соответствующего di ...-. ,. d, - CjO; если исходное состояние соответствует 1 , то ситналы на выходе логических схем 7 и 8 принимают значения , а в переходном режиме изменение состояния любого триггера приводит к поа.пР«„ рмупднпго сигнала схемы компараявлению выходного сигнала схемы компара тора D 0, который сохраняется вплОть до достижения первого исходного состояния di . В этом случае компаратор имеет запаздывание, не превышающее длительность полупериода частоты сигнала а, а, что увеличивает его быстродействие и динамическую точност ь. Работа схемы компаратора по описанному алгоритму обеспечивается включением на выходе его логических схем 7 и 8, реализующих соответственно уравнения: С : d,C + df + d, а,; D + (d,,- d,)C. Предмет изобретения Фазовый кОЙпаратбр, содержащий триггер, в цепь запуска которого включены две импульспо-потенциальные схемы совпадения, о тличающийся тем, что, с цейью повышения точности в работе компараторй, ой содержит второй триггер с двумй йм.пульйнб-потенциальными схемами совладения и цепи запуЬка, причём пбтенцйальньгё вХодь обеих J, совпадения подклю4ены параллельно и соответственно к источникам прямого и инвербного сигнала прямоугольной формы одной из сравниваемых частот, их объединенные им„ульсные входы подключены cobTBetctfieftM k источникам прямого и инВерсйогЬ прямоугольной формы другой срайнйваемой частоты, а выходы триггеров подключены к двум последовательно -соединенным основной дополнительной логическим схемам, реалидующим соответственно уравнения: ,C + d.f:-i-d -dt; D d,(d,-d, + d,-d,)C, С - выход основной логической схемы; rfi, - прямые выходы триггеров; й, Й2 - йн1вёрсныё вь1ходы триггеров; D - выход дополнительной логической схемы, являющийся выходом фазового компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый компаратор | 1983 |

|

SU1115204A1 |

| Устройство для автоматической синхронизации с постоянным временем опережения | 1979 |

|

SU855855A1 |

| Фазовый компаратор | 1981 |

|

SU1109871A1 |

| Устройство для автоматической синхронизации с постоянным временем опережения | 1982 |

|

SU1046842A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1203685A1 |

| ФАЗОВЫЙ КОМПАРАТОР | 2005 |

|

RU2282935C1 |

| Устройство для измерения угла сдвига фаз | 1990 |

|

SU1789939A1 |

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| УСТРОЙСТВО АНАЛОГОВОГО ДАТЧИКА УГЛА ФАЗОВОГО СДВИГА МЕЖДУ НАПРЯЖЕНИЕМ И ТОКОМ | 2011 |

|

RU2492572C2 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

J

а

Даты

1974-06-30—Публикация

1972-03-29—Подача