«

Изобретение относится к радиотехнике и может быть использовано в устройствах автоподстройки частоты и фазы, синтезаторах частоТд в устройствах цифровой обработки сигнало синхронных демодуляторах фазовой и частотной манипуляции, для индикации синфазного состояния сигналов.

Цель изобретения - расширение функциональных возможностей путем формирования дополнительных потен- сигналов рассогласования в режиме частотного детектирования,

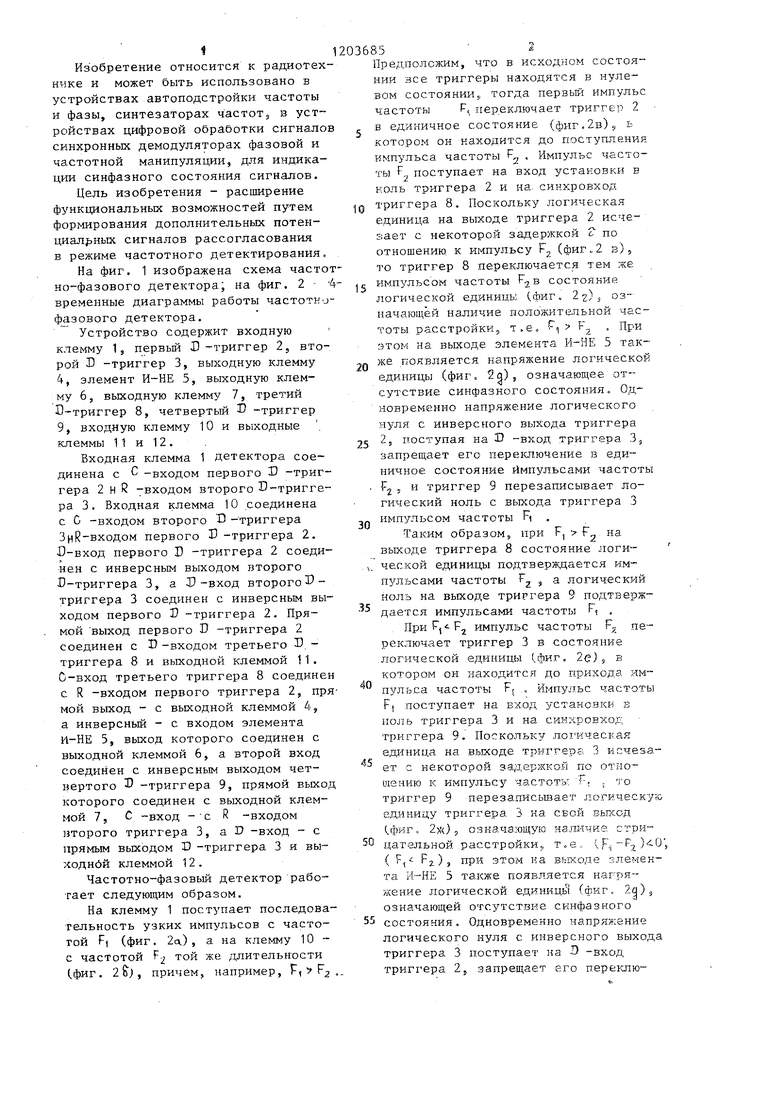

На фиг. 1 изображена схема частоно-фазового детектора; на фиг, 2 - временные диаграммы работы частотыj ф 1зового детектора.

Устройство содержит входную клемму 1, первьй Л -триггер 2, второй Л -триггер 3, выходную клемму 4, элемент И-НЕ 5, выходную клемму 6, выходную клемму 7, третий D-триггер 8, четвертый -триггер 9, входную клемму 10 и выходные клеммы 11 и 12.

Входная клемма 1 детектора соединена с С -входом первого I) -триггера 2 Н R -входом второго D-триггера 3, Входная клемма 10 соединена с С -входом второго D - триггера SnR-BxoAOM первого Л -триггера 2, 0-вход первого D -триггера 2 соединен с инверсным выходом второго С-триггера 3, а -вход второго триггера 3 соединен с инверсным выходом первого 1 -триггера 2, Прямой выход первого D -триггера 2 соединен с D -входом третьего триггера 8 и выходной клеммой 11, С-вход третьего триггера 8 соединен с R -входом первого триггера 2, прямой выход - с выходной клеммой 4, а инверсный - с входом элемента И-НЕ 5, выход которого соединен с выходной клеммой 6, а второй вход соединен с инверсным выходом четвертого -О -триггера 9, прямой выход которого соединен с выходной клеммой 7, С -вход - С R -входом второго триггера 3, а D -вход - с прямым выходом D -триггера 3 и вы- ходнбй клеммой 12.

Частотно-фазовьш детектор работает следующим образом.

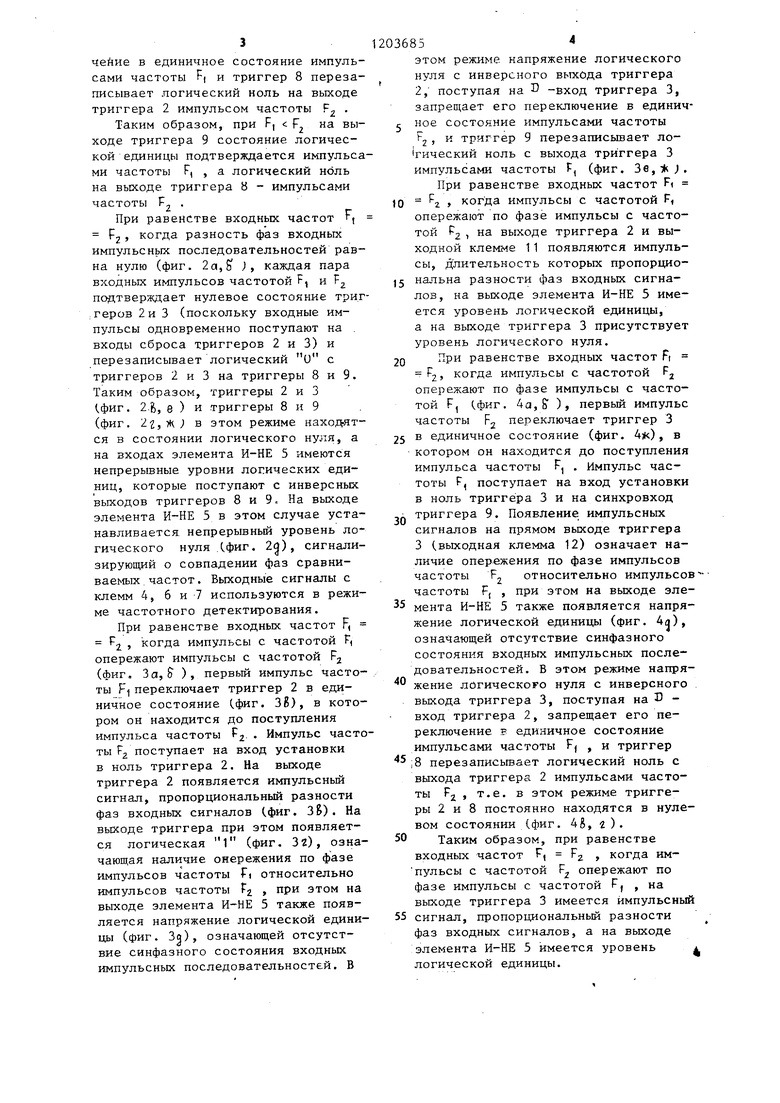

На клемму 1 поступает последовательность узких импульсов с частотой f (фиг. 2а,) , а на клемму 10 - с частотой 2 той же длительности (.фиг, 2 &;, причем, например, Г,р203685

Предположим, что в исходном состоянии все триггеры находятся в нулевом СОСТОЯНИИ;, тогда первый импульс частоты F( переключает триггер 2 в ед иничное состояние (фиг,2в),, ь котором он находится до поступления импульса частоты F,, . Импульс частоты f,j, поступает на вход установки Е коль триггера 2 и на синхровход д триггера 8. Поскольку логическая единица на выходе триггера 2 исчезает с некоторой задержкой по отношению, к импульсу Г (фиг.,2 в), то триггер 8 переключается тем же

,е импульсом частоты 2 состояние

логической единицы; (ф иг. 27)5 означающей, наличие положительной частоты расстройки, т,е, FI f, . При этом на выходе элемента И-НЕ 5 также появляется напряжение логической единицы (фиг, 2q)s означающее отсутствие синфазного состояния. Одновременно напряжение логического нуля с инверсного выхода тр иггера 25 2, поступая на О -вход триггера 3, запрещает его переключение в единичное состояние импульсами частоты . 2 3 и триггер 9 перезаписывает логический ноль с выхода триггера 3 импульсом частоты FI .

Таким образом, при F, f, на выходе триггера 8 состояние логической единицы подтверждается импульсами частоты F , а логический

20

30

ноль на выходе триггера

подтверж

дается импульсами частоты FI ,

ПриГ, Fj импульс частоты у переключает триггер 3 в состояние логической единицы (фиг. 2(}, в котором он находится до прихода гдмг- .,

пульса частоты Г( , импульс частоты FI поступает на вход установки в ПОЛЬ тригге ра 3 и на сикхровход триггера 9, Посколькз лот И чаская единица на выходе триггера 3 исчезает с некоторой за,це ржкой по отношению к импульсу частоты ;-, , т-о триггер 9 перезаписьтает логическую единицу триггера 3 на СБОЙ вькод (,фиг „ 2)() 5 означающую наличие стридательной расстройки, Тов,, ( р., - F -, ) с О , ( F, - F,) , гфи этом ка выходе злемек- та И-НЕ 5 также появляется напряжение логической единицы (фр1г, Zg), означающей отсутствие синфазного

состояния. Одновременно напряжение логического нуля с инверсного выхода триггера 3 поступает на Э -вход триггера 2. запрещает его переключейие в единичное состояние импульсами частоты FI и триггер 8 перезаписывает логический ноль на выходе триггера 2 импульсом частоты F

Таким образом, при F, F на выходе триггера 9 состояние логической единицы подтверждается импульсами частоты

9

а логический ноль

на выходе триггера Ь - импульсами

частоты F, .

гг При равенстве входных частот г,

2 когда разность фаз входных импульсньгх последовательностей равна нулю (фиг. 2а,8 ), каждая пара входных импульсов частотой Fj и F подтверждает нулевое состояние триг ;Геров 2и 3 (поскольку входные импульсы одновременно поступают на . входы сброса триггеров 2 и 3) и перезаписывает логический U с триггеров 2 и 3 на триггеры 8 и 9. Таким образом, триггеры 2 и 3 (,фиг. 2.g, е ) и триггеры 8 и 9 (фиг. 2, Ж j в этом режиме находятся в состоянии логического нуля, а на входах элемента И-НЕ 5 имеются непрерывные уровни логических единиц, которые поступают с инверсных выходов триггеров 8 и 9, На выходе элемента И-НЕ 5 в этом случае устанавливается непрерывньй уровень логического нуля ЛФиг. 2), сигнализирующий о совпадении фаз сравниваемых частот. Выходные сигналы с клемм 4, 6 и 7 используются в режиме частотного детектирования.

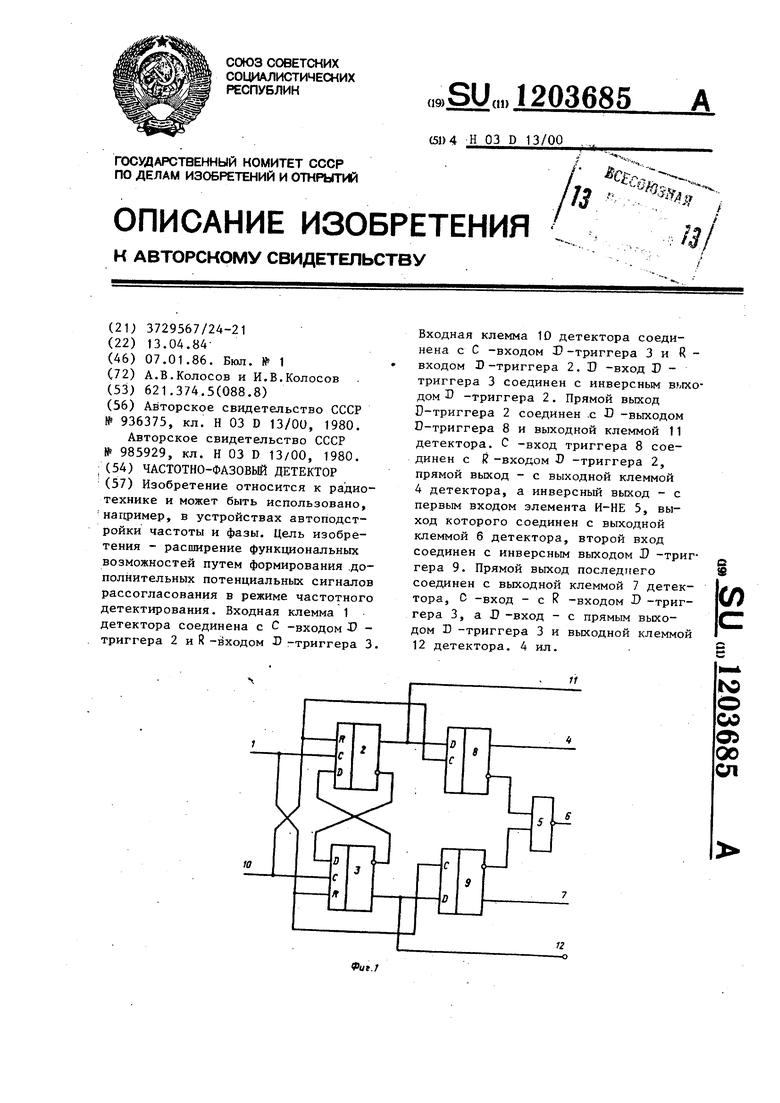

При равенстве входных частот F, Pj , когда импульсы с частотой FI опережают импульсы с частотой Fj (фиг. За, ), первый импульс частоты f) переключает триггер 2 в единичное состояние (фиг. ЗВ), в котором он находится до поступления импульса частоты 2 Импульс частоты 2 поступает на вход установки в ноль триггера 2. На выходе триггера 2 появляется импульсньш сигнал, пропорциональный разности фаз входных сигналов (фиг. Зб). На выходе триггера при этом появляется логическая 1 (фиг. Зг), означающая наличие опережения по фазе импульсов частоты FI относительно импульсов частоты Г , при этом на выходе элемента И-НЕ 5 также появляется напряжение логической единицы (фиг. Зо), означающей отсутствие синфазного состояния входных импульсных последовательностей. В

2036854

этом режиме напряжение логического нуля с инверсного выхода триггера 2, поступая на D -вход триггера 3, 3anpeDtaeT его переключение в единич- 5 ное состояние импульсами частоты 2 , и триггер 9 перезаписьшает ло- 1гический ноль с выхода триггера 3 импульсами частоты F, (фиг. 3e,J. При равенстве входных частот Ft 10 2 когда импульсы с частотой FI опережают по фазе импульсы с частотой 2 1 на выходе триггера 2 и выходной клемме 11 появляются импульсы, длительность которых пропорцио- )5 напьна разности фаз входных сигналов, на выходе элемента И-НЕ 5 имеется уровень логической единицы, а на выходе триггера 3 присутствует уровень логического нуля. 20 При равенстве входных частот FI 2 когда импульсы с частотой Fj опережают по фазе импульсы с частотой F, (,фиг. 4а, ), первый импульс частоты f, переключает триггер 3 25 в единичное состояние (фиг. 4)К), в котором он находится до поступления импульса частоты F, . Импульс частоты F, поступает на вход установки в ноль триггера 3 и на синхровход -- триггера 9. Появление импульсных сигналов на прямом выходе триггера 3 (выходная клемма 12) означает наличие опережения по фазе импульсов частоты F относительно импульсов- частоты F, , при этом на выходе эле- 5 мента И-НЕ 5 также появляется напряжение логической единицы (фиг. Ал), означающей отсутствие синфазного состояния входных импульсных последовательностей. В этом режиме напряжение логического нуля с инверсного выхода триггера 3, поступая на D - вход триггера 2, запрещает его переключение Е единичное состояние импульсами частоты F) , и триггер ;8 перезаписьшает логический ноль с выхода триггера 2 импульсами частоты Р , т.е. в этом режиме триггеры 2 и 8 постоянно находятся в нулевом состоянии (фиг. 48, 2). 50 Таким образом, при равенстве входных частот fz когда им- пульсы с частотой F опережают по фазе импульсы с частотой F, , на выходе триггера 3 имеется импульсный 55 сигнал, пропорциональный разности фаз входных сигналов, а на выходе элемента И-НЕ 5 имеется уровень i логической единицы.

40

512036856

Техническим преимуществом изобре- гера, отличающийся тем, тения является расширение его функцио- что, с целью расширения функциональнальных возможностей, Которое достигается путем использования ражи- , мов частотного и фазового детектирования. При этом частотное детектирование обеспечивается формированием дополнительных потенциальных сигналов о знаке рассогласования частот. Использование дополнительной информации и синфазности входных сигналов в режиме фазового детектирования также позволяет расширить функциональные возможности устройства.

Формула изобр.етеняя

Частотно-фазовый детектор, содержащий два D -триггера, С -входы которых соединены соответственно с одной из входных клемм детектора и R-входом другого J -триггера, а D-ВХОДЫ их соединены соответственно с инверсным выходом другого О -тригных возможностей, в него введены дополнительно третий и четвертью Ь-триггеры и элемент И-НЕ, при этом

С-вход третьего О -триггера соединен с R -входом первого D -триггера, прямой выход - с первой выходной клеммой генератора, а инверсный вы(0 ход - с первым входом элемента И-НЕ, выход которого соединен с второй выходной клеммой генератора, а второй вход - с инверсным выходом четвертого D -триггера, прямой выход котоJ5 рого соединен с третьей выходной клеммой генератора, С -вход соединен с R -входом второго О -триггера, при этом четвертая выходная клемма генератора соединена с прямым

20 выходом первого и Л -входом третьего и -триггеров, а пятая выходная клемма соединена с прямым выходом второго и D -входом четвертого О - триггеров.

25 I . ,

гера, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены дополнительно третий и четвертью Ь-триггеры и элемент И-НЕ, при этом

С-вход третьего О -триггера соединен с R -входом первого D -триггера, прямой выход - с первой выходной клеммой генератора, а инверсный вы(0 ход - с первым входом элемента И-НЕ выход которого соединен с второй выходной клеммой генератора, а второй вход - с инверсным выходом четвертого D -триггера, прямой выход котоJ5 рого соединен с третьей выходной клеммой генератора, С -вход соединен с R -входом второго О -триггера, при этом четвертая выходная клемма генератора соединена с прямы

20 выходом первого и Л -входом третьего и -триггеров, а пятая выходная клемма соединена с прямым выходом второго и D -входом четвертого О - триггеров.

25 I . ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1124424A1 |

| Цифровой частотно-фазовый компаратор | 1985 |

|

SU1248025A1 |

| Импульсный частотно-фазовый детектор | 1989 |

|

SU1807550A1 |

| Импульсный частотно-фазовый детектор | 1984 |

|

SU1221710A2 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1269255A1 |

| Импульсный частотно-фазовый детектор | 1983 |

|

SU1246334A1 |

| Импульсный частотно-фазовый детектор | 1985 |

|

SU1312718A1 |

| Формирователь разностной частоты импульсных последовательностей | 1984 |

|

SU1265985A1 |

| Частотно-фазовый детектор | 1982 |

|

SU1095351A1 |

| Преобразователь последовательности импульсов в прямоугольный импульс | 1987 |

|

SU1499457A1 |

Изобретение относится к радиотехнике и может быть использовано, нагфимер, в устройствах автоподстройки частоты и фазы. Цель изобретения - расширение функциональных возможностей путем формирования .дополнительных потенциальных сигналов рассогласования в режиме частотного детектирования. Входная клемма 1 детектора соединена с С -входом 1 - триггера 2 и R-входом D -триггера 3. Входная клемма ID детектора соединена с С -входом I -триггера 3 и R - входом D-триггера 2. D -вход Р - триггера 3 соединен с инверсным выходом -триггера 2. Прямой выход D-триггера 2 соединен .с D -выходом D-триггера 8 и выходной клеммой 11 детектора. С -вход триггера 8 соединен с I -входом D -триггера 2, прямой выход - с выходной клеммой 4 детектора, а инверсный выход - с первым входом элемента И-НЕ 5, выход которого соединен с выходной клеммой б детектора, второй вход соединен с инверсным выходом D -триггера 9. Прямой выход последт его соединен с выходной клеммой 7 детектора, С -вход - с R -входом J -триггера 3, а Х -вход - с прямым выходом D -триггера 3 и выходной клеммой 12 детектора. 4 ил. (Л ю о со О) 00 сд

| Устройство для определения знака разности двух частот | 1980 |

|

SU936375A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсный частотно-фазовый детектор | 1980 |

|

SU985929A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1986-01-07—Публикация

1984-04-13—Подача